基于VHDL语言和可编程逻辑器件实现HDB3编译码器的设计

可编程逻辑

描述

1 、引言

HDB3(High Density Bipolar三阶高密度双极性)码是在AMI码的基础上改进的一种双极性归零码,它除具有AMI码功率谱中无直流分量,可进行差错自检等优点外,还克服了AMI码当信息中出现连“0”码时定时提取困难的缺点,而且HDB3码频谱能量主要集中在基波频率以下,占用频带较窄,是ITU-TG.703推荐的PCM基群、二次群和三次群的数字传输接口码型,因此HDB3码的编解码就显得极为重要了。目前,HDB3码主要由专用集成威廉希尔官方网站 及相应匹配的外围中小规模集成芯片来实现,但集成程度不高,特别是位同步提取非常复杂,不易实现。随着可编程器件的发展,这一难题得到了很好地解决。

本文利用现代EDA设计方法学和VHDL语言及模块化的设计方法,设计了适合于FPGA实现的HDB3编译码器的硬件实现方案。不但克服了分立硬件威廉希尔官方网站 带来的抗干扰差和不易调整等缺陷,而且具有软件开发周期短,成本低,执行速度高,实时性强,升级方便等特点。

2、 HDB3编解码原理

要了解HDB3码的编码规则,首先要知道AMI码的构成规则,AMI码就是把单极性脉冲序列中相邻的“1”码(即正脉冲)变为极性交替的正、负脉冲。将“0”码保持不变,把“1”码变为+1、-1交替的脉冲。如:

NRZ码:1 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1

AMI码:-1 0 0 0 0 +1 0 0 0 0 -1 +1 0 0 0 0 -1 +1

HDB3码是一种AMI码的改进型,它的编码原理可简述为,在消息的二进制代码序列中:

(1)当连“0”码的个数不大于3时,HDB3编码规律与AMI码相同,即“1”码变为“+1”、“-1”交替脉冲;

(2)当代码序列中出现4个连“0”码或超过4个连“0”码时,把连“0”段按4个“0”分节,即“0000”,并使第4个“0”码变为“1”码,用V脉冲表示。这样可以消除长连“0”现象。为了便于识别V脉冲,使V脉冲极性与前一个“1”脉冲极性相同。这样就破坏了AMI码极性交替的规律,所以V脉冲为破坏脉冲,把V脉冲和前3个连“0”称为破坏节“000V”;

(3)为了使脉冲序列仍不含直流分量,则必须使相邻的破坏点V脉冲极性交替;

(4)为了保证前面两条件成立,必须使相邻的破坏点之间有奇数个“1”码。如果原序列中破坏点之间的“1”码为偶数,则必须补为奇数,即将破坏节中的第一个“0”码变为“1”,用B脉冲表示。这时破坏节变为“B00V”形式。B脉冲极性与前一“1”脉冲极性相反,而B脉冲极性和V脉冲极性相同。

如:

NRZ码:1 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 1

AMI码:-1 0 0 0 0 +1 0 0 0 0 -1 +1 0 0 0 0 -1 +1

HDB3码:-1 0 0 0 -V +1 0 0 0 +V -1 +1 –B 0 0 -V +1 -1

虽然HDB3码的编码规则比较复杂,但译码却比较简单。从上述原理看出:每一个破坏符号V总是与前一非0符号同极性(包括B在内)。这就是说,从收到的符号序列中可以容易地找到破坏点V,于是也断定V符号及其前面的3个符号必是连0符号,从而恢复4个连0码,再将所有-1变成+1后便得到原消息代码。

3、 编解码器设计

3.1 编码器设计

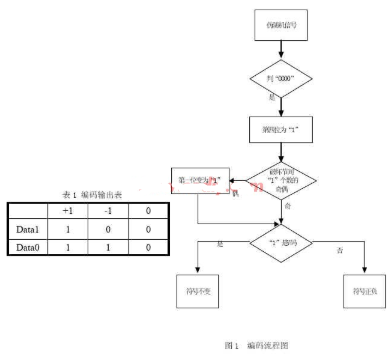

由于VHDL不能处理负电平,只能面向“1”、“0”两种状态,所以要对它的输出进行编码,如表1所示。编码的实现是根据HDB3编码原理把二进制码编码成两路单极性的码字输出,之后经过单双变换模块形成HDB3码。在编码过程中,要经过连0检测、破坏节判断、破坏节间“1”的个数判断、调整“1”的符号输出等步骤,编码部分可分为4个模块,编码流程如图1所示。

在进行HDB3编码器的设计时,需注意以下两个问题:

(1) 考虑将某些“0”改为“1”

用一个四位移位寄存器来对输入的序列进行检测,当检测到4个连“0”时,将其第四个“0”改为“1”。再设置一个T触发器来检测两个相邻的破坏节之间“1”的个数,若T触发器为“0”则说明两个相邻的破坏节之间“1”的个数为偶数,需要将第2个破坏节的第一个“0”置“1”,若T触发器为“1”,则说明两个相邻的破坏节之间“1”的个数为奇数,第2个破坏节的第一个“0”不变。

(2) 正、负号的考虑

除了破坏节的V即“1”的符号与它前面最近的“1”的符号相同外,其他的“1”的符号都是正、负交替的。所以再设置一个T触发器,当它检测到“1”时就使DATA1翻转。当然,这样就不可避免地使破坏节的V的符号也出现翻转,为了防止它的翻转,用一个三位移位寄存器来跟踪V码,以保证V码的符号不变(与它前面最近的“1”的符号相同)。

本文在程序的实体中定义了2个输入端口:时钟、伪随机序列,一个两位的输出数据(编码后的输出)。程序的结构体中使用的是进程语句,共采用4个进程,分别完成判断4连“0”位置并插入V、记相邻V码间1个数、跟踪V码位置及编码输出的功能。敏感信号均选用的是时钟信号,对于其任一变化都将同时启动4个进程,并行执行。在程序中共使用了5个信号,代表了威廉希尔官方网站 的寄存器效果,配置到威廉希尔官方网站 中也相当于寄存器。

3.2 解码器设计

解码设计是根据HDB3码的特点首先检测出极性破坏点,即找出4连零码中添加V码的位置(破坏点位置),其次去掉添加的V码,最后去掉4连零码中添加的B码以将其还原成单极性不归零码。

由HDB3码的编码规则可知,“0000”都被“000+1”或“000-1”或“+100+1”或“-100-1”取代,所以,只要能检测出“+1000+1”、“-1000-1”、 “+100+1”、“-100-1”、将它们分别改为“10000” 、“10000”、“0000”、“0000”就可以了。

当然“+1”、“-1”、“0”还是由Data1,Data0来表示,那么就需要有两个5位移位寄存器(C和D),Data0通过D,Data1通过C。通过D,C来检测,如果测到两个移位寄存器分别为“10001”、“0xxx0”或“10001”、“1xxx1”或“1001x”、“1xx1x”或“1001x”、“0xx0x”,数据输出是将D里面的数据流输出。所以只要将D中所测到的以上数据分别改为“10000”、“10000”、“0000x”、“0000x”,这样就可以得到HDB3码的解码了。

4、 仿真和实验结果分析

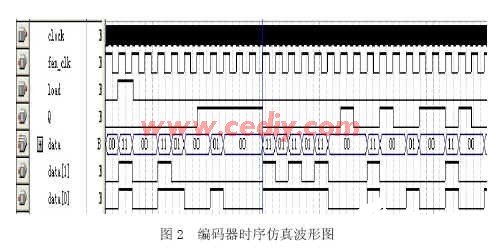

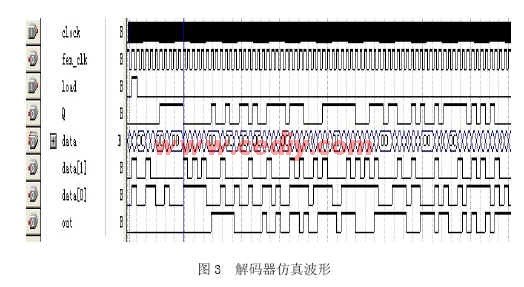

编译码器在QuartusII上仿真的波形分别如图2和图3所示。图2中fen_clk为分频后时钟信号,load 为使能信号,Q为伪随机序列,data为编码输出。由于输入的数据流经过了5个寄存器,所以输出延迟了4个时钟脉冲周期。但由于时钟频率很高,所以影响不大。

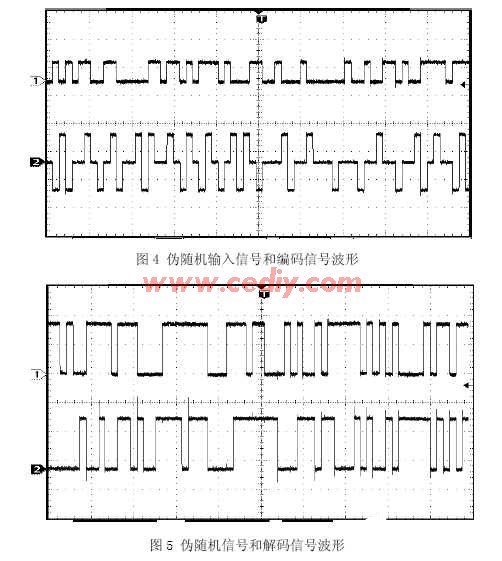

把上述设计下载到Altera EP1C3T144C8芯片上,并通过硬件调试、测试,在示波器上得到伪随机信号波形、编码波形和解码波形分别如图4和5所示。其中,CH1为伪随机信号,CH2分别为编码和解码信号。测试结果和时序仿真结果无失真。随机信号输入相对编码信号输出延迟了5个单位时钟。解码信号延时了11个单位时钟。

5、 结论

实践表明,运用FPGA来实现NRZ码到HDB3码的转换与采用专用集成威廉希尔官方网站 CD22103相比,不仅给调试带来了方便,而且可以把编码威廉希尔官方网站 和解码威廉希尔官方网站 及其它威廉希尔官方网站 集成在同一块FPGA芯片中,减少了外接元件,提高了集成度。该设计已成功应用于网络化集中照明控制系统中。然而在实际无中继长线传输中,会出现信宿端信号严重失真的现象,一种对长线传输系统中HDB3编码的失真信号进行矫正的算法见文献。

本文作者的创新点:本方案设计模块可以作为IP(Intellectual Property)核,与嵌入式处理器及其他功能模块或IP芯核相结合在一片FPGA上构成片上可编程系统SOPC,使得所设计的系统在其规模、可靠性、体积、功耗、性能等方面实现最优化。

作者简介:

吴海涛(1975-),男(汉族),山东青州市人,广东肇庆学院电子信息工程系讲师,硕士,主要从事通信、EDA技术应用研究。

陈英俊(1962-),男(汉族),广东潮州人,广东肇庆学院电子信息工程系副教授,主要从事计算机通信及视频处理技术研究。

梁迎春(1975-),女(汉族),广西玉林市人,广东肇庆学院电子信息工程系讲师,硕士,主要从事EDA/SOPC技术研究。

责任编辑:gt

-

基于Nios的通用编译码器的设计2009-11-30 811

-

可编程逻辑器件2014-04-15 0

-

基于EDA技术的可编程逻辑器件在数字信号处理系统中的应用2019-06-28 0

-

可编程逻辑器件设计2006-03-25 1021

-

基于CPLD的HDB3码编解码威廉希尔官方网站 的设计2010-02-24 714

-

可编程逻辑器件基础及应用实验指导书2010-03-24 631

-

基于CPLD的HDB3码编译码器的设计2010-05-17 769

-

基于FPGA的HDB3编解码器设计2010-07-28 697

-

什么是PLD(可编程逻辑器件)2009-06-20 26356

-

EDA技术与应用(可编程逻辑器件)2012-05-23 917

-

可编程逻辑器件(书皮)2022-07-10 455

-

用VHDL语言设计数据传输系统中的HDB3编码器2018-02-08 13105

-

基于可编程逻辑器件和VHDL语言实现算术逻辑单元的设计2021-01-04 2314

-

可编程逻辑器件测试2023-06-06 685

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2845

全部0条评论

快来发表一下你的评论吧 !