采用FPGA芯片EP1C12Q240C8实现直接数字频率合成器的设计

可编程逻辑

描述

1、引言

自1971年,美国学者J.Tierney等人撰写的“A Digital Frequency Synthesizer”-文首次提出了以全数字技术实现数字频率合成以来,构成DDS元器件的速度的限制和数字化引起的噪声这两个主要缺点阻碍了DDS的发展与实际应用。近几年超高速数字威廉希尔官方网站 的发展尤其是大规模超高速的FPGA技术的日渐成熟,以及对DDS的深入研究,DDS的最高工作频率以及噪声性能已接近并达到锁相频率合成器相当的水平。它具有较高的频率分辨率,可以实现快速的频率切换,并且在频率改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。因此,在现代电子系统及设备的频率源设计中,尤其在通信领域,直接数字频率合成器的应用越来越广泛。而实现直接数字频率合成器的方案也较多,目前,用得最多的有三种技术方案,一种是采用高性能DDS单片威廉希尔官方网站 的解决方案;二是采用低频正弦波DDS单片威廉希尔官方网站 的解决方案;三是自行设计的基于FPGA芯片的解决方案。虽然有的专用DDS芯片的功能也比较多,但控制方式却是固定的,因此不一定是我们所需要的。而利用FPGA则可以根据需要方便地实现各种比较复杂的调频、调相和调幅功能,具有良好的实用性,但因为编制VHDL源程序较为复杂,因此也得不到很好的应用。本文利用Matlab/DSP Builder建模,然后很方便地在FPGA中实现DDS信号发生器的设计,避免了编制VHDL语言源程序的复杂性,使设计制作一个需要的DDS信号发生器变得非常简单和快捷。

2、DDS的基本原理

一个频谱纯净的单频信号可表示为 这种单频信号的主要特征是相位是时间的线性函数,且相位函数对时间的导数是一个常数。相位函数是一条直线,它的斜率就是信号的频率。如果对上式的信号进行采样,采样周期为Tclk,则可以得到离散的波形序列为:

这种单频信号的主要特征是相位是时间的线性函数,且相位函数对时间的导数是一个常数。相位函数是一条直线,它的斜率就是信号的频率。如果对上式的信号进行采样,采样周期为Tclk,则可以得到离散的波形序列为:

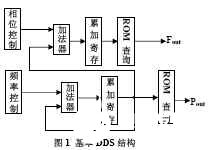

相应的离散相位序列的连续两次采样之间的增量为 ,若采样值在采样间隔内保持,则波形和相位变成了阶段梯形。根据采样定理,可以通过查表法产生波形,即设计一控制威廉希尔官方网站

,使之按照一定的地址关系从存储器当中读取数据,进行数模转换,就可以得到一定频率的输出波形。其基本的威廉希尔官方网站

框图可用图1来表示。

,若采样值在采样间隔内保持,则波形和相位变成了阶段梯形。根据采样定理,可以通过查表法产生波形,即设计一控制威廉希尔官方网站

,使之按照一定的地址关系从存储器当中读取数据,进行数模转换,就可以得到一定频率的输出波形。其基本的威廉希尔官方网站

框图可用图1来表示。

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字k相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

3、DDS在MATLAB/DSP Bulider中的模型建立及在FGPA中实现

3.1 在MATLAB/DSP Bulider建模

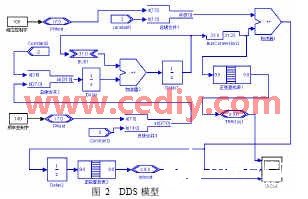

根据DDS的工作原理,可以利用MATLAB建立DDS基本原理图的模型如图2所示,其中正弦查找表的Matlab Array一项填写“ ”,即在让SignalCompiler在编译过程中,自动产生1024个正弦波数据,此波形数据存放在DSP Bulider模型文件夹的一个扩展名为.mif文件里。分别设置频率控制字和相位控制字为100和200后,进行仿真,打开SCOPE观察其波形,发现其频率能够受频率控制字的控制,其相位也能够受相位控制字控制。仿真正确后,双击Singacompler图标,将此模型转换成VHDL源程序。经过分析转换后的VHDL程序并将其转换为ATOM netlist,最后编译ATOM netlist,无误后表明建模已完成。

3.2 在Quartus II 4.0中进行编译仿真生成FPGA下载文件

打开 Quartus II 4.0,找到DDS的Quartus II 4.0项目文件并打开。设置好目标器件,编译后再进行一次仿真。其仿真波形如图3所示。由此可以看出,其输出波形即为我们需要的正弦波数据。最后锁定好引脚,下载到目标器件,实现DDS模块芯片的设计。

4、结语

由上面的设计我们可以看出采用MATLAB/DSP Bulider建模,再在Quartus II 4.0中进行编译,最后下载到目标器件这种方法实现数字频率合成方法,既避免了VHDL编程的复杂性,而且又便于修改和扩充其功能,达到需要的信号。如要改变输出波形的的步进精度,以及如果要增加幅度控制等,则只需要在模型中作简单的修改即可,即将频率控制字、相位控制字的宽度改变即可。如要增加幅度控制,则只需要在模型中用一乘法器控制输出幅度即可实现。因此采用此种方法,完全可以根据用户需要定制一个DDS信号发生器,而不需要增加太多的成本。本文作者创新点,充分利用了嵌入到MATLAB中的DSP Bulider工具的强大功能,实现DDS信号发生器的建模,并给出了具体的模型。避免了复杂的VHDL程序编制,同时也充分利用了FPGA的设计的灵活性,实现用户需要的DDS信号发生器设计。

责任编辑:gt

-

采用AD9914 3.5 GSPS直接数字频率合成器的AD9914/PCBZ评估板2019-03-01 0

-

AD9914BCPZ直接数字频率合成器2019-04-29 0

-

采用FPGA实现直接数字频率合成器设计2019-06-18 0

-

什么是频率合成器2019-08-19 0

-

怎么设计直接数字频率合成器?2019-08-21 0

-

DDS直接数字频率合成器、信号发生器、函数发生器2022-03-24 0

-

基于FPGA的直接数字频率合成器的设计2010-08-09 422

-

FPGA实现的直接数字频率合成器2009-05-11 966

-

基于FPGA的直接数字频率合成器的设计和实现2009-05-16 1015

-

数字频率合成器的FPGA实现2009-06-20 951

-

低功耗直接数字频率合成器的设计2011-07-07 606

-

AD9910: 1 GSPS、14位、3.3 V CMOS直接数字频率合成器2021-03-19 713

-

UG-475:评估采用14位DAC的AD9912 1 GSPS直接数字频率合成器2021-05-27 720

全部0条评论

快来发表一下你的评论吧 !