基于CPLD芯片EPF10K100TC144-3实现虚拟相位测量系统的应用方案

可编程逻辑

描述

1 引言

相位计是用于测量两个具有相同变化规律的信号之间相位差的仪器。两个相同频率信号之间的相位差有多种测量方法。常用的相位-时间转换方法是传统数字式相位差计采用的一种方法,此种方法通用性和灵活性均较差,基于CPLD的虚拟相位计由数据采集、单片机及CPLD(可编程逻辑器件)等组成。

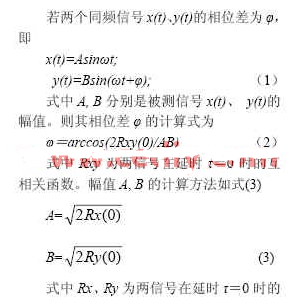

2基于相关原理的虚拟相位差测量法

3虚拟相位计结构

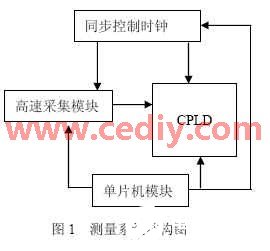

虚拟相位计主要由高速数据采集模块、单片机模块、同步时钟控制模块和CPLD组成。以高性能、高集成度、低功耗系列CPLD作为核心计算部件,负责进行自相关和互相关分析,同步控制时钟负责采样及相关分析的同步计算,利用CPLD高级成集成、高速、高可靠性的特点,满足系统实时、快速测量要求。

系统由单片机启动数据采集和CPLD计算。高速采集模块同时对两个同频信号 x(t)、 y(t)采样,将采得时间序列x(n)和y(n)送往CPLD, 同步时钟同时控制CPLD进行相关分析。采样及相关分析结束后,其计算结果由单片机取出进行反三角函数计算,从而得出相位差。

4 CPLD结构设计

本系统中的CPLD是采用FLEX10K系列EPF10K100TC144-3。该芯片具有高密度、低功耗、高速度和灵活的互联方式,支持多电压接口,多种配置的特点。

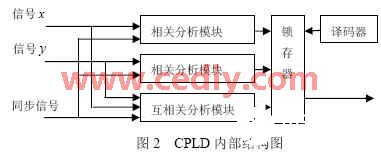

结构分析

根据系统要求,芯片内部主要由计算模块组成。分为信号1自相关分析模块、信号2自相关分析模块、和互相关分析模块。结构如图2所示。本设计使用MAXPLUSΠ软件,根据本系统的逻辑结构,使用图形化输入方法进行程序设计。

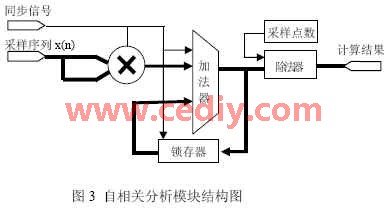

自相关分析模块

相关分析模块主要由乘法器、加法器和除法器组成。同步信号控制平方、相加和相除运算的同步进行,采样点数可由单片机进行赋值。模块结构如图3所示。

在图形化编程中,锁存器、乘法器、加法器和除法器均为LPM(参数化模块库) 中元件。在编程中可通过设置参数来实现器件运算速度和数据线宽度的配置。

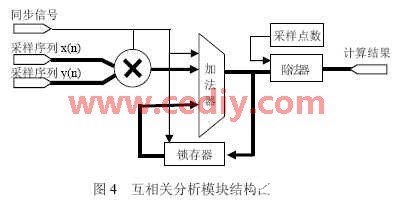

互相关分析模块

互相关分析模块结构如图4所示。

5结论

本文介绍的基于CPLD的虚拟相位测量系统采用了目前比较先进的可编程器件技术和虚拟仪器技术,通过CPLD的相关分析和采样同步进行,可大大减少单片机的计算工作,并对系统存储资源的需求减到很小。但是,由于CPLD计算速度的限制,虽然把器件设置在高速运行并流水设计到最佳,此系统对高频信号的测量仍较困难。随着CPLD技术的发展,对高频信号的测量将有所改善。

责任编辑:gt

-

IIC总线通讯接口器件的CPLD实现2009-10-30 0

-

哪位大神能告我如何在qutars ii上添加EPF10K20TC144-4的裤2014-05-31 0

-

怎样去设计一种基于EPF10K10LC84芯片的IIR滤波器2021-10-20 0

-

S32K144EVB-Q100和S32K142EVB-Q100有什么区别吗?2023-03-27 0

-

基于PLD及FPGA的频率与相位测量系统设计与实现2009-09-25 443

-

基于虚拟仪器技术的比较法相位型振动测量系统2009-11-29 580

-

低频数字相位(频率)测量的CPLD实现2010-07-28 713

-

基于CPLD的虚拟相位测量2010-08-09 646

-

用PLD实现相位精确测量的研究2006-03-11 3807

-

基于EMP7128的数字式相位测量仪2009-06-20 1243

-

以EP1K30TC144-3为控制核心实现CPLD出租车计费器系统的设计2018-11-14 3704

-

AVR单片机Atmega128在FPGA配置的应用和对EPF10K10软硬件设计原理2018-10-26 1220

-

基于FPGA器件EPF10K20RC240-3实现HDLC协议控制器的应用方案2020-09-27 1401

-

基于MCU+CPLD的相位差和频率的测量方法研究及实现2023-10-31 1140

-

AGM CPLD 应用指南2024-01-10 1035

全部0条评论

快来发表一下你的评论吧 !