FPGA工程的时序约束实践案例

可编程逻辑

描述

1. 理论回顾

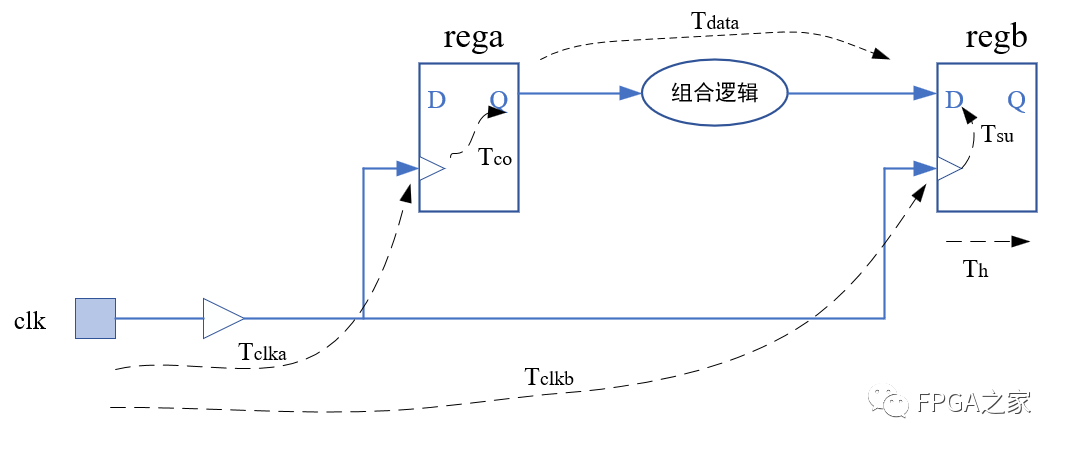

先来回顾一下有关时序的理论知识,上图是典型的同步时序模型及其时序图,由发起寄存器(rega)、组合逻辑、捕获寄存器(regb)及其中间的走线组成。

源时钟clk到达rega的时钟端口时,会有一定的延迟,从而形成clka。同理,时钟延迟到达regb的时钟端口,形成clkb。Tco为有效数据出现在发起寄存器Q端口所需时间。Tdata为数据延迟,包括组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或者干预,其中Tdata由组合逻辑(代码)及布局布线决定,这也决定了系统最高的工作频率。

2. 时间裕量

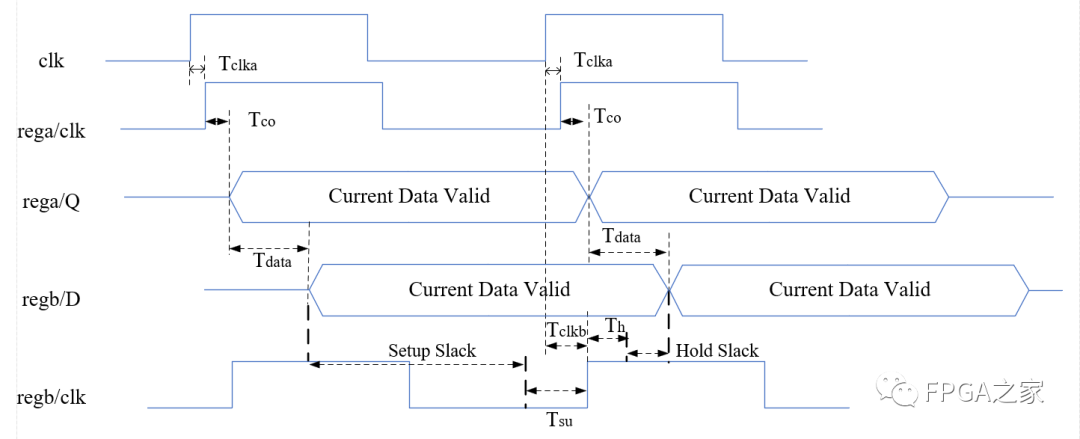

时间裕量包括建立时间裕量和保持时间裕量(上图中的setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多是不是就意味着时序约束越宽松呢?应该是这样的。

通俗的讲,一个FPGA工程在综合实现后,是否满足时序约束,其实就是看所有的捕获寄存器是否能正确稳定捕获到发起寄存器发出的数据。如上图所示,也就是说到达捕获寄存器的数据输入端口D(regb/D)的数据要满足建立和保持时间要求,也就是说在Tsu之前,current data valid就要准备就绪,而在Th之后呢,current data valid还要多维持一段时间。换言之,在Tsu之前以及Th之后多出的这部分时间,我们就称之为“裕量”,裕量越大,时序越宽松。裕量的大小与时钟频率、代码设计以及布局布线有着紧密的联系。一个设计的时序报告中,裕量为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是一个风险(时序报告是按照工艺、电压以及温度的上下限给出的结果)。当违例数较多,也就意味着设计在实际环境中出现问题的概率也会越大。

3. 最大延迟和最小延迟

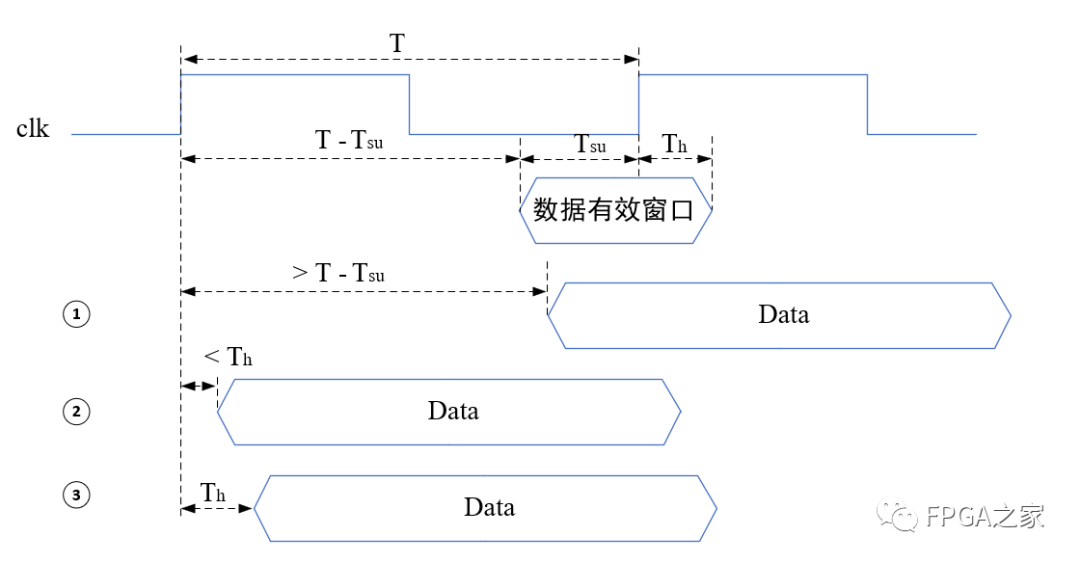

如下图所示,“数据有效窗口”表示捕获的数据满足建立时间和保持时间,在此窗口中要捕获的数据不能发生变化,否则将引起不稳定的结果。

我们来看1、2、3三种情况,在分析之前,首先要明确Data的持续时间长度一定是一个时钟周期(多周期打拍另说)。1:当延迟时间大于T-Tsu时,Data在建立时间区域内才到达regb,所以不满足建立时间要求,这就是说数据来的“太晚了”;2:当Data延迟了很小一段时间(

综上所述,数据的最大延迟是T-Tsu,最小延迟是Th。一看是看到这儿有点纳闷,最大延迟我们还能理解,延迟太大,捕获不到数据,这是理所当然。延迟还有下限是什么意思?仔细看看文章开头的时序模型和时序图,实际生成的威廉希尔官方网站

图之后,除了要满足Th的要求外,数据路径和捕获时钟路径肯定不太可能一定拥有相同的延迟,举个极端的例子,如果clkb延迟非常大,那么current data valid必须增加延迟才能保证被clkb捕获到。

一般而言,在综合之后,我们需要特别关注的是建立时间的时序违例,因为可以通过增加布线长度来保证保持时间。大多数保持时间违例在实现之后自然会被优化掉。

4. 案例分析

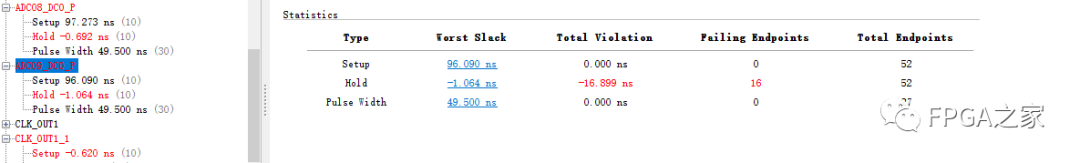

以下是在实际工程(VIVADO平台)中的时序分析结果:

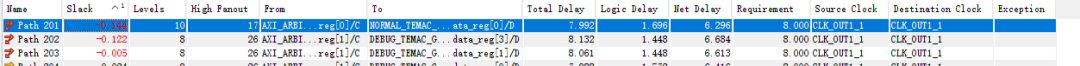

如上图所示,综合后给出的时序报告,可以看到ADC的时钟出现了hold时序违例,clk_out1_1出现了setup违例。然后进行实现,实现完成后hold违例消失(正如上面所述,保持时间往往可以修改布线长度来保证),如下图所示为实现后的结果,目前只存在3条路径出现setup违例,即建立时间裕量为负。

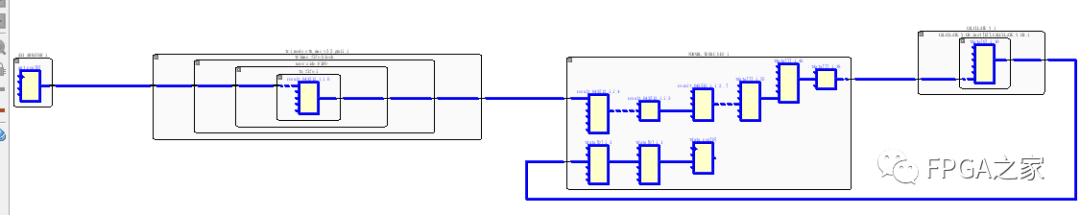

以path201为例:选中path201,按F4(或右键schematic),打开路径的原理图,如下图所示,可以看到该路径经历多个模块,时序路径较长。

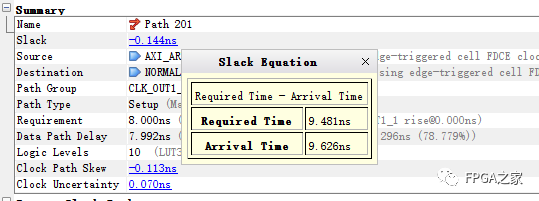

双击path201,会显示该路径的具体信息,点击slack可以弹出相应的需求时间和实际的到达时间,可以清晰的看到实际到达时间是长于需求时间的,所以出现时序违例的情况。

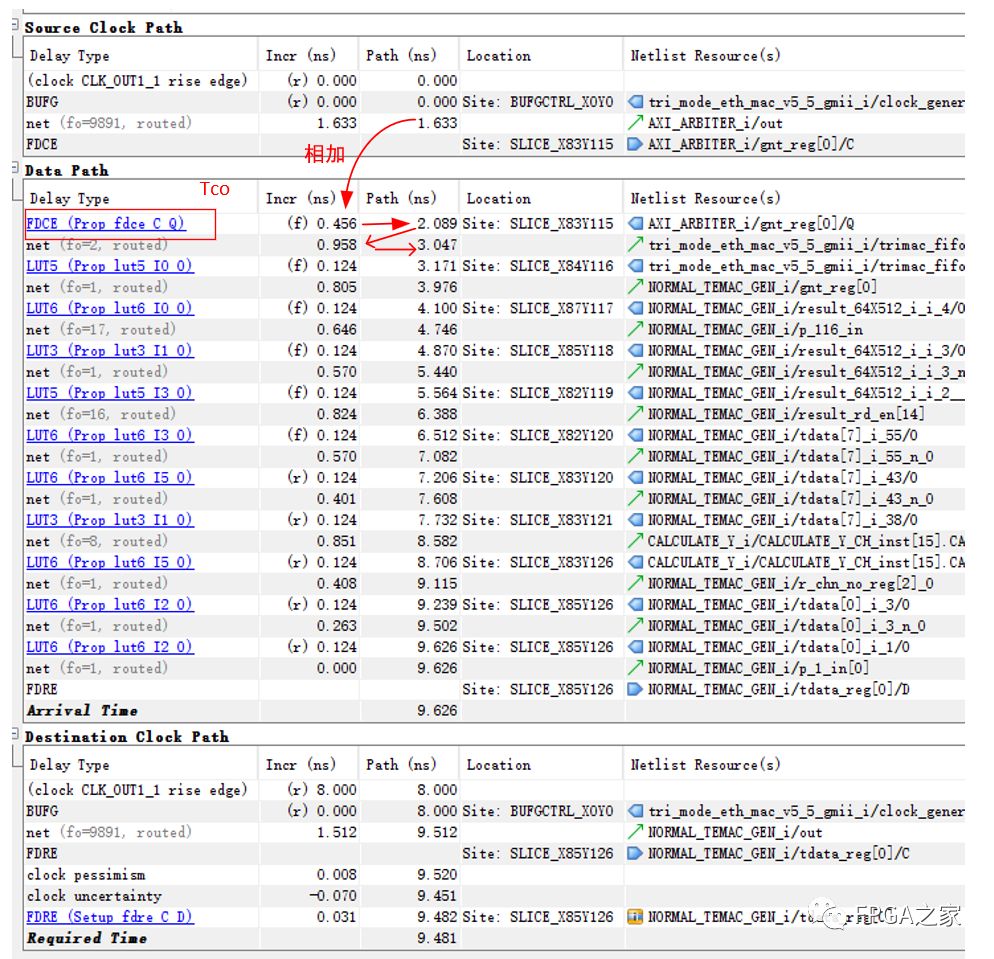

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。通过观察各中间过程,分析其中延迟较大的环节,可以做相应的优化约束或代码有效。

一般而已,少量的时序违例(如本工程,只有3条路径违例),是可以通过实现策略(strategy)的修改达到要求。如果时序违例较严重,那么就需要详细的分析各时钟之间的关系(同步or异步)、是否分析该路径等各方面进行深刻的分析,然后修改时序约束文件,更严重的可能要手动布局及修改布线,我对这方面还理解的不是很透,所以等弄明白了再总结。

审核编辑:黄飞

-

FPGA时序约束OFFSET2015-09-05 0

-

FPGA时序约束方法2015-12-14 826

-

FPGA中的时序约束设计2017-11-17 2568

-

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果2017-11-24 5483

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2179

-

【潘文明至简设计法】系列连载教程 FPGA时序约束视频教程2017-06-14 0

-

FPGA设计之时序约束2022-03-18 1670

-

详解FPGA的时序input delay约束2022-05-11 4120

-

FPGA的时序input delay约束2022-07-25 3047

-

FPGA的IO口时序约束分析2022-09-27 1746

-

FPGA时序约束的基础知识2023-06-06 1501

-

FPGA主时钟约束详解 Vivado添加时序约束方法2023-06-06 10724

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 2725

-

FPGA时序约束的原理是什么?2023-06-26 717

-

FPGA I/O口时序约束讲解2023-08-14 1635

全部0条评论

快来发表一下你的评论吧 !