基于FPGA的帧内预测编码器硬件架构设计详解

可编程逻辑

描述

针对帧内预测的快速算法,由于DSP 架构软件顺序执行的局限性难以满足实时性要求,而FPGA 以其高速的计算速度和强大的并行处理能力成为H.264 和AVS 编解码的理想平台。本文在FPGA 平台上采用资源共享、高并行和多流水线结构实现了亮度帧内预测算法。该方法在分析AVS 帧内亮度5 种预测模式的基础上,将像素预测与模式判决在一个模块中完成,并且利用各模式预测的相似性,实现运算单元共享和多种模式并行执行,兼顾了处理速度和实现代价。仿真及综合结果表明该设计能够完全满足标清(704×576,30f/s) 数字视频的实时处理要求。

AVS(Audio Video Coding Standard) 标准, 是《信息技术—先进音视频编码》系列标准的简称, 是由我国自主提出的数字音视频编解码技术标准, 这个标准达到了当前国际先进水平。AVS 具有以下优点:(1) 性能高, 编码效率是MPEG2的2 倍以上, 与H.264 的编码效率处于同一水平;(2) 复杂度低, 算法复杂度比H.264 明显低, 软硬件实现成本都低于H.264;(3) 我国掌握主要知识产权, 专利授权模式简单, 费用低。AVS 视频标准制定的目标是: 适应数字电视广播、数字存储媒体、因特网流媒体、多媒体通信等应用中对运动图像压缩技术的需要,这就对编码的实时性提出了很高的要求。

帧内预测是AVS 编解码中很重要的部分,其原理是利用图像内部相邻像素间的相关性来降低编码码率,也就是通过减少空间冗余度来达到压缩的目的。视频编码器帧内预测部分的硬件架构设计方案一般分为两种。第一种是基于可重构硬件威廉希尔官方网站 的设计。这种威廉希尔官方网站 结构设计思想是根据帧内预测各模式算法上的相似性,设计出能够处理所有预测模式的可重构的运算单元。该运算单元可根据预测模式的不同对输入的数据选择相应的数据通路,从而达到资源的最优化利用。由于该威廉希尔官方网站 结构是逐个处理各个模式的预测,因此其缺点是处理速度慢。第二种设计方案是将具有相同预测值求解算法的预测模式共用同一个预测器,以优化资源利用,文献 采用了这种设计方案。本文参考第二种设计方案,提出了一种基于资源共享以及并行流水[7] 的帧内预测编码器硬件架构。

1 AVS 帧内预测模块算法原理

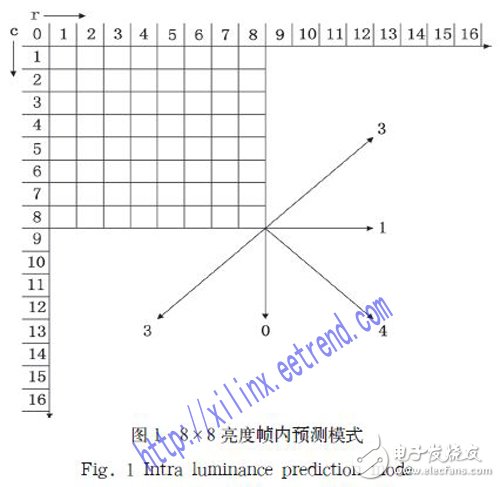

AVS 的帧内预测分为亮度(1uma) 和色度(chroma) 预测两种,都是以8x8 的块为单位进行预测的。其中,亮度预测包括33 个参考像素点,有5 种预测模式(如图1 所示),Vertical预测模式、Horizontal 预测模式、DC 预测模式、Down_Left 预测模式和Down_Right 预测模式。图1 标示了AVS 帧内预测模式的预测方向,标号的对应关系为:Vertical 模式( 模式值为0)、Horizontal 模式( 模式值为1)、DC 模式( 模式值为2)、Down_Left 模式( 模式值为3)、Down_Right( 模式值为4)。

色度预测包括17 个参考像素点,有4 种预测模式,分别为:DC 模式( 模式值为0)、Horizontal 模式( 模式值为1)、Vertical模式( 模式值为2) 和Plane 模式( 模式值为3)。其中,DC模式、Horizontal 模式、Vertical 模式与亮度预测算法相同。

AVS 的帧内预测模块子块级主要包括像素值预测和模式判决两部分,实现的功能主要是在给出当前块的左边像素,左上像素以及上边像素的情况下按照各种模式预测的方法得到当前块的预测像素值。

AVS 编码标准采用了计算预测块和原始块之间的SAD 来寻找最合适的预测模式的方法。编码器将所有的预测模式遍历一遍,算出所有模式对应的SAD 值,取其中拥有最小SAD的模式作为最终选择的模式。

2 帧内预测硬件设计与实现

2.1 帧内预测模块硬件设计方案

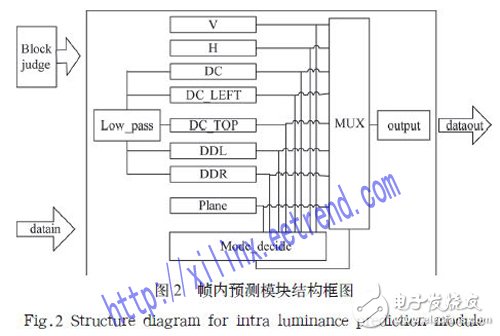

设计中,Blockjudge 子模块的功能是由系统计数的BlockNum 变量判断当前块在一帧图像中的位置,从而决定当前块的相邻块边缘像素的可用性。由图2 可知,在给定输入数据的情况下,多种模式并行挂起,由于预测是按一个时钟预测一个像素进行的,在预测完一个像素就进计算一次绝对误差计算,然后预测完下一个就将误差累加,最终预测完成,SAD 的计算也完成。模式判决模块完成的是在SAD 计算完后比较得出各模式下的SAD 最小值,按其对应的预测模式即最佳预测模式选择输出对应的预测数据。可见整个过程是多个模式并行,并且共享公共运算单元,单个模式多级流水,从而提高资源利用率。

2.2 亮度预测模块的VHDL 实现

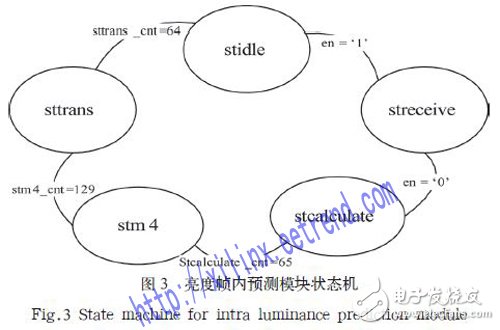

帧内亮度预测模块的VHDL 实现主要涉及到四部分:读写数据单元, 运算单元,数据比较单元,输出单元。这四个部分分别对应于状态机(亮度帧内预测模块状态机如图3 所示)的streceive、 stcalculate、stcompare 和sttrans 状态。状态之间的转换通过状态计数器完成,预测输出数据用于与当前块数据做残差供DCT 使用,最佳模式输出供熵编码写码流。

系统的起始状态是stidle 状态,当使能en 置1 时转到streceive 状态;streceive 状态将接收的数据(总共接收97 个数据,前64 个是8x8 块的原始数据,后33 个是参考数据)分别暂存到RAM00 和RAM11 中,RAM00 中存储的当前块数据用于与各种模式预测值进行SAD 运算,RAM11 中的数据用于得出预测数据,同时在该状态存储预测模式V 和H 需要的参考数据;当使能en 置0 时进入stcalculate 状态,在stcalculate 状态将33 个参考数据中相邻的三个数据按(a+2b+c+2)》》2 低通滤波, 得到31 个预测数据。并且存储DDR 模式,DDL 模式,DC_LEFT 模式和DC_TOP 模式需要的预测数据。在stm4 状态读取DC_LEFT 和DC_TOP 的预测数据d 和e,同时进行运算(d+e)》》1 得到f, 将f 进行限幅运算clip(f), 从而得到DC 模式的预测值并将其存储;同时完成的有V,H,DDL,DDR的模式预测。预测过程按单像素进行,即串行输入串行输出,SAD 的计算通过SAD《=SAD+ABS(a-b) 累加完成。各种模式下2 个时钟完成一个像素值的存储和绝对差值的计算;系统在stcompare 状态通过冒泡排序法得到SAD 最小值minSAD,其对应的模式即为最佳预测模式;sttrans 状态完成最佳预测模式以及对应的预测值输出。

各种模式实现过程中的公共单元:

主要运算单元:

l《=(a+b+b+c+2)》》2;

SAD《=SAD+ABS(a-b);

读写数据单元:

V,DC_TOP 是将8 个值按列赋值得到64 个数据;H,DC_LEFT 是将8 个值按行赋值得到64 个数据;DDL,DDR 是将15个值按照循环移位的方式给行赋值得到64 个数据,都是通过循环嵌套计数器来完成。

色度预测的状态图与亮度类似,只是输入的参考数据是17个。Plane 模式预测实现比较复杂,在给出输入数据的情况下有一个预处理的过程,运算量较大,预处理过程中得到的中间结果需要判断正负号,而且涉及到左移四位右移五位的运算,因此数据位宽需要扩展至16 位,最终的符号位才不会被移走,负数在运算的过程中以补码的形式存在,所以若符号位为1 则在右移后高位补1,反之则补0。

3 实验结果

本文设计是以8×8 块为单元,采用VHDL 硬件描述语言实现了帧内像素值预测以及模式判决模块。设计中所采用的硬件处理平台是Xilinx 公司的VidexII 系列FPGA xc2vp20,整个设计在ISE 10.1 环境下进行。

3.1 功能仿真结果

仿真过程中我们将预测输出内容存储到Pre_RAM 中,在每个子块预测结束时打印至文本文件,同时将相同的视频码流加入到我们采用的软件模型并打印与我们仿真相应的部分内容, 将两者进行比较。至模块完成时,已成功完成一个完整视频码流的数据对比,结果完全相同。

3.2 时序仿真结果

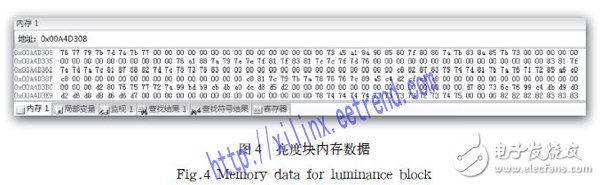

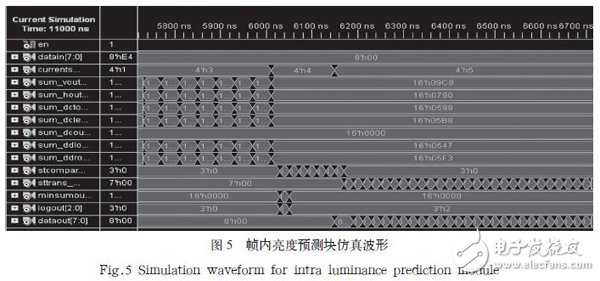

与功能仿真一样, 我们将Pre_RAM 中存储的内容在每个块预测结束时打印至文本文件, 同时将相同的视频码流加入到我们采用的软件模型并打印与我们仿真相应的部分内容,将两者进行比较,结果也完全相同。由于篇幅限制图4 仅给出了与图5 对应的同一亮度块在软件模型中的内存数据,8x8亮度块预测的仿真结果如图5 所示,图中显示的当前状态是stm4,stcompare 和sttrans,其中sum_v, sum_h, sum_dc,sum_dc_left, sum_dc_top, sum_ddl, sum_ddr 分别表示各

对应模式下的SAD 值,log 表示最佳预测模式,dataout 表示最佳预测值,对比可知二者结果一致。

3.3 综合

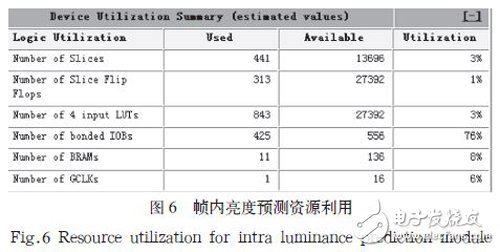

资源利用情况如图6 所示,整个预测过程占用了328 个时钟周期。而系统时钟频率在100MHZ 的情况下要达到实时时钟周期需要控制在526 之内,显然仿真结果表明该硬件结构完全满足标清AVS 视频实时编码要求。

4 结束语

本文将AVS 帧内亮度预测模块的像素值预测和模式判决结合到一个模块中在FPGA 平台硬件实现。采用资源共享的设计思想,同时将各种模式并行执行和流水处理,兼顾了时钟和资源利用率。仿真结果表明,当工作在155.927MHz 时钟时,可以实时处理704x576、4:2:0、30 帧/s 的视频图像。拥有中国自己的自主知识产权的数字音视频编解码标准(AVS),在技术和性能上处于国际先进水平。本论文的研究内容对于AVS标清视频编码芯片的设计有着实际的参考价值。

-

AG32:工业伺服编码器应用2024-05-08 0

-

H. 264 /AVC帧内预测模式选择算法研究2008-06-25 0

-

基于纹理复杂度的快速帧内预测算法2010-05-06 0

-

编码器的实现2011-08-10 0

-

基于H.264的无再损帧内编码2010-02-09 747

-

基于FPGA增量式编码器的接口设计2011-11-03 773

-

LDPC码编码器的FPGA实现2016-05-09 739

-

基于FPGA的AVS帧内预测的研究与设计单天燕2017-03-19 739

-

高精度增量式编码器与基于DSP和FPGA编码器信号测量模块2017-10-13 1237

-

硬件编码器是什么,软件编码和硬件解码的区别2018-08-02 19637

-

如何使用FPGA实现H.264帧内预测2021-01-28 706

-

一种屏幕内容编码帧内CTU深度范围预测快速算法2021-03-17 697

-

面向硬件实现的HEVC帧内编码快速算法2021-06-21 711

-

架构与微架构设计2023-05-08 1199

-

编码器类型详解:探索不同编码技术的奥秘2024-11-19 599

全部0条评论

快来发表一下你的评论吧 !