采用以FPGA为基础的变频器惯性输出技术,能大大提高变频器的稳定可靠性

可编程逻辑

描述

1 引 言

节能降耗是国家的基本国策,而电厂节能是电力系统节能降耗的重要环节,采用高压变频技术对电厂重要用电设备的驱动电源进行技术改造,是火电厂节能降耗有效途径。随着高压变频器已经在电厂中得到越来越广泛的应用,变频器运行的稳定可靠性将直接影响整个电厂的安全。在实际运行中如果变频器的主控制器死机或者复位将引起变频器停止输出,使负荷电动机停机,这将给电厂造成巨大的损失。针对目前使用最广泛的级联多电平变频器,本文采用基于fpga的变频器惯性输出技术,即fpga在检测到主控制器异常时,根据记忆值维持变频器的输出直至控制器恢复正常,将大大提高变频器的稳定可靠性。

2 级联多电平变频器工作原理

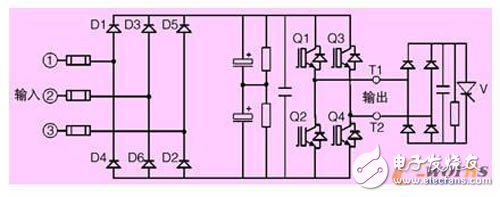

级联多电平变频器又称单元串联多电平变频器或完美无谐波变频器,通过串联若干低压功率单元的方式来实现高压输出,电压电流的谐波含量低,对电网谐波污染较小,输入功率因数较高,并且不必采用输入谐波滤波器和功率因数变换器,在实际中应用较为广泛。以6kv变频器为例,每相由6个额定电压为577v的功率单元串联,三相共有18个功率单元,分别由输入隔离变压器的18个二次绕组供电,18个二次绕组分3组,每组之间存在20°相位差,形成相当于18脉冲整流。使得电压总畸变率只有3%,电流总畸变率小于4%。其结构图如图1所示。

图1 级联式6kv变频器结构图

功率单元的结构如图2所示,三相交流电整流后经滤波电容滤波形成直流母线电压,逆变器由4个耐压为1700v的igbt模块组成h桥式单相逆变威廉希尔官方网站 ,通过pwm控制,在输出端得到变压变频的交流输出,输出电压为单相交流0~577v,频率为0~50hz。旁路功能是一种当设备出现故障后断开故障点而使设备继续正常运行功能。当需要旁路时,通过晶闸管v导通,旁路该功率单元输出,平常正常工作时,晶闸管v处于关断状态。

图2 级联式变频器功率单元结构图

3 基于fpga的相位移载波spwm调制方法

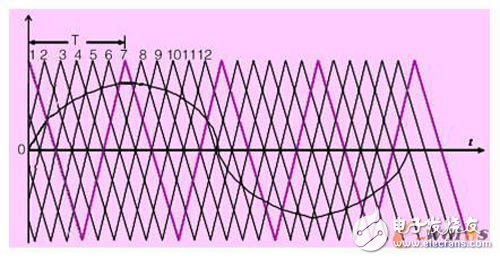

相位移载波技术的基本原理是使用几个1.2khz三角载波信号和一个正弦参考信号(每相) 比较,产生spwm信号。将三角载波进行合适的移相,可以消除特定次数的谐波。以a相为例,正弦调制波和三角载波如图3所示。六级功率单元使用的正弦调制波的幅值和相位相同,而每级功率单元的三角载波形状相同相位不同,各载波间相角依次移动2π/6即60°,这样就可以有效抑制输出电压和电流变化率。h桥单元左右桥臂的调制波相位相反,有助于提高整个系统的等效载波比。试验已证明n级单元串联时的等效载波频率为三角载波的频率的2n倍,并且在该种方式控制下的直流电压利用率高。

图3 相位移载波调制原理图

目前所使用的变频器一般将上述比较过程放在cpu中完成,当cpu遇到干扰复位或程序出错的时候,变频器将停止输出。由fpga来完成三角波和正弦波的比较过程将很好的解决这个问题,利用cpu的强大计算能力实时计算参与比较的正弦波,利用fpga高速度的时钟精确产生移相三角波,然后在fpga中进行比较输出。

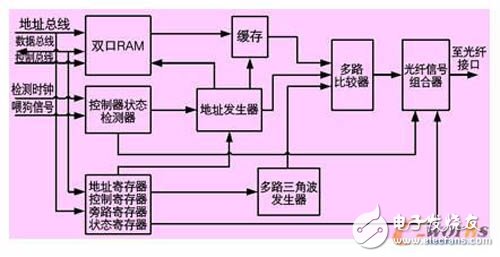

4 fpga脉冲发生器及惯性输出原理

由fpga实现相位移载波spwm调制的结构框图如图4所示。fpga与cpu的接口由数据总线、地址总线和控制总线实现,cpu上电后首先对fpga的控制寄存器进行初始化,设置spwm的输出周期,各路三角波的初始相位和幅值。地址发生器根据周期寄存器的值产生ram读取地址,输出数据进入缓存。在每个三角波的谷值处给cpu一个中断,通知cpu更新数据,在每个三角波的峰值处从ram中读取数据进入缓存。cpu每次更新数据的同时也更新地址寄存器,指明当前输出数据的地址长度,此地址长度决定了变频器输出的频率。多路比较器实时将缓存数据与对应三角波进行比较产生spwm波形,光纤信号组合器将每一个功率单元所需信号即左臂信号、右臂信号、闭锁信号、旁路信号组合编码成一路串行信号送入光接口。

图4 fpga实现变频器惯性输出结构图

在fpga内部实现了一个看门狗(控制器状态检测器)对cpu进行监视,cpu在正常工作时,在每ms之内必须给fpga一个喂狗信号,当检测器在2ms没有检测到此信号变化则给地址发生器一个信号,地址发生器则根据当前的地址寄存器产生地址从双口ram中读取数据,从而实现cpu死机时变频器输出的相位和频率能够继续,即具有惯性输出功能。fpga实现惯性输出时,状态寄存器保存当前输出频率值和故障标志,以供cpu复位之后读取。

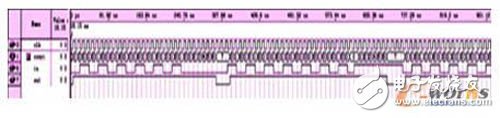

5 verilog设计与仿真

根据图4的结构框图应用verilog语言进行设计,选用lattice的xp3系列fpga进行设计,与传统的基于sram的fpga不同,latticexp3器件不需要外接引导存储器,因此能提供单芯片的解决方案,从而减少了威廉希尔官方网站 板面积,并简化了系统制造过程。以控制状态检测器为例,当fpga在一段时间内检测到cpu的喂狗信号没有改变时,给出cpu异常信号,改变地址控制器的输出策略。其仿真图形如图5所示。

图5 cpu状态检测器仿真时序图

6 实验结果

依据本文所述的惯性输出理论所研制的6kv变频器样机,在运行时手动复位主cpu,输出的电压波形能够与复位前的频率和幅值一致,主cpu复位之后根据fpga中保持的复位前数据维持变频器输出的连续。上述实验验证了变频器主cpu死机复位时的惯性输出理论。

7 结束语

本文详细论述了惯性输出技术在级联式多电平变频器设计中的应用,通过仿真和实际样机的研制验证了该技术的可行性,采用此技术可以大大提高变频器输出的稳定可靠性。虽然惯性输出技术目前在高压变频器中的应用仅限于样机,但随着行业的逐渐认同和实际运行的检验后,惯性输出技术必将成为检验下一代变频器的重要技术指标。

-

基于AN8026变频器高性能电源设计方案2018-09-28 0

-

基于AN8026控制芯片的变频器电源设计方案2018-11-29 0

-

变频器如何选择?变频器与变频电源的区别有哪些呢2022-05-22 0

-

中压变频器及应用综述2009-07-18 3020

-

变频器控制技术与应用2016-03-04 1192

-

变频器实用技术分享:变频器选型方法和原则、变频器使用保养注意事项2017-08-14 1711

-

变频器的外部运行操作2020-02-26 11063

-

基于FPGA的数字下变频器(DDC)的设计2021-09-16 1160

-

变频器能节电吗?变频器节电原理2023-03-29 1543

-

什么是变频器?变频器能实现哪些控制功能?2023-08-11 1237

-

变频器输出电压怎么测2023-09-13 17922

-

输入和输出的变频器滤波器如何区别?2023-10-28 1636

-

变频器电阻容易烧坏的原因及预防措施2024-05-31 2576

-

变频器使能端子的设置方法2024-06-11 1418

全部0条评论

快来发表一下你的评论吧 !