以FPGA为基础的玻璃缺陷图像采集处理系统方案详解

可编程逻辑

描述

1. 引言

玻璃缺陷检测是玻璃生产过程中一个相当重要课题,玻璃缺陷(气泡、结石、锡点等)妨碍了其在重大技术领域中的应用,不但影响了产品的外观,同时由于它的不平整度及屈光度的影响,使得人透过玻璃观察实物时受到障碍。目前国内外在本领域的研究成果大致为分别利用线、面阵CCD 获取表面图像,由后续软件对图像加以分析的方法来实现对表面质量的检测处理。本课题正是基于这样一种指导思想下,设计了一种基于FPGA 的玻璃缺陷在线检测系统方案,利用FPGA 实时、高速、可重构的特点,并对玻璃缺陷图像进行的预处理(卷积运算),从而大大降低了后期数据处理的压力,使得图像处理系统运算速度快,具有很好的适应性。

2. 图像采集处理系统硬件平台

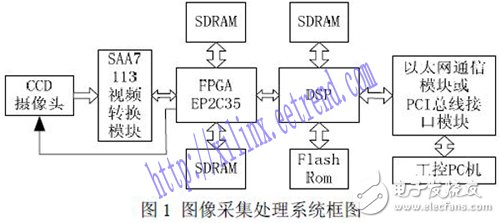

在图像信号处理过程中为保证实时性,首先要求实时图像处理系统具有处理大数据的能力;其次对系统的体积大小、功能、稳定性等也有严格的要求。实时图像处理算法中经常要用到对图像的求和、求差运算、二维梯度运算、图像分割等不同层次、不同种类的运算[1]。基于上述因素,考虑到FPGA 和DSP 的优异性能,我们在玻璃缺陷检测系统中采用了如图1 所示的硬件平台。

系统内各模块功能简要描述如下:(1)视频采集异步FIFO 模块(内嵌于FPGA 中)接收从视频A/D 芯片SAA7113 送来的数字视频流,解决系统数据缓冲和异步时钟的问题,因为:SAA7113 送过来的LLC 频率为27MHz,而FPGA 系统时钟频率为48MHz. (2)视频解码模块用来对得到的数字视频流进行解码,识别出行、场同步信号,并且根据需要选择采集图像的大小。(3) I2C 配置接口模块(通过EP2C35 进行模拟配置)通过I2C 总线对SAA7113进行初始化配置,选择产生的数字视频格式等。(4)图像帧存控制模块用来读写系统两片帧存储器并且可以在它们之间进行读写切换操作。(5)图像低级处理模块从帧存中读取一帧图像数据,对其进行底层大量运算的图像预处理,如噪声消除、边缘检测等,最后将处理完的图像数据经通信模块送至后端DSP 处理器做进一步操作。此外由于采用基于SDRAM 工艺的FPGA 芯片,所以还需要配置威廉希尔官方网站 在上电时对FPGA 进行配置。

系统上电时,FPGA 首先从外部配置芯片中读取配置数据,通过AS 主动串行方式完成自身的程序加载,进入工作模式状态。随后I2C 配置接口模块完成对SAA7113 的初始化,初始化结束后,FPGA 等待采集图像的命令。FPGA 收到采集命令后,启动采集视频数据模块、异步FIFO 模块和视频解码模块进行解码,将数据轮换写到两个帧存中,供图像低级处理模块处理、经DSP 对图像做了进一步处理后由通信模块送往工控PC。

3. 系统中内存管理和图像低级处理技术

3.1 SDRAM 控制实现及仿真

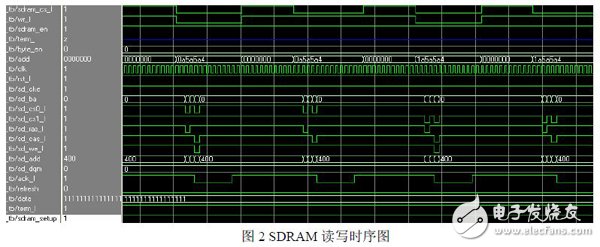

视频转换芯片输出的视频图像数据通过 8 位总线VPO 传输给FPGA,FPGA 需要将数据保存到SDRAM 中,SDRAM 在读写上有严格的时序要求。SDRAM 的命令由RAS_n、CAS_n、WE_n 和LOAD_mode 构成,分别表示行选择、列选择、读写控制和寄存器配置控制[2]。在本系统中,我们设计了SDRAM(基于FPGA)接口模块,该模块控制SDRAM 的命令与时序。模块内设计了初始化机制和系统指令分析机制。初始化机制不仅要完成对SDRAM 的初始化配置,还要完成对控制器的初始化配置,从而使控制器与外部SDRAM 的工作模式一致。为了实现高效的SDRAM 存取,提高SDRAM 总线的利用率,SDRAM 接口模块CLK 采用133MHz 的高速时钟,当得到数据存取模块的读FIFO 要求后,向SDRAM连续写入16 个字。当得到PC 接口模块的读SDRAM 请求后读出1 个字,其他时间保证SDRAM 进行刷新工作,以免数据丢失。从我们的硬件设计平台可以看出,系统中的SDRAM分别由PFGA 和DSP 控制。当DSP 和FPGA 完成对相应SDRAM 的操作后,需要进行总线切换。总线切换后,DSP 和FPGA 开始对另一块SDRAM 进行相应操作。其主要代码如下:

//控制信号tg =1 ,dsp 的EMIF 接口连接到sdram1,dsp 从sdram1 中读取数据

//控制信号tg=0,切换到sdram2

assign ed_sdram=tg?sdram_1_in_ed:sdram_2_in_ed;

assign sdram_1_o_ed = tg ? 8‘hzz : ld;

assign sdram_1_oen = tg ? 1’b0 :1‘b1;

assign sdram_1_ea= tg ? ea_sdram : l a;

assign sdram_1_ce=tg? ce_sdram: sdram_ce;

assign sdram_1_oe= tg ?oe_sdram :sdram_oe;

assign sdram_1_we= tg ? we_sdram: sdram_we;

//控制信号tg =1 ,fpga 连接到sdram2,fpga 写数据到sdram2

//控制信号tg=0,切换到SDRAM1

assign sdram_2_o_ed = tg ? ld:8’hzz;

assign sdram_2_oen = tg ? 1‘b1:1’b0;

assign sdram_2_ea = tg?la:ea_sdram;

assign sdram _2_ce= tg?sdram_ec:ce_sdram ;

assign sdram_2_oe= tg?sdram_oe: oe_sdram;

assign sdram_2_we= tg?sdram_we: we_sdram ;

3.2 图像低级处理的FPGA 实现

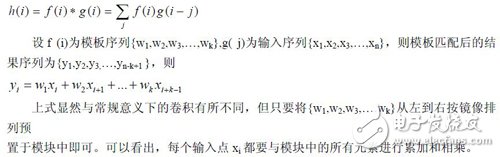

图像处理系统中,底层的图像预处理(滤波、锐化)的数据量很大,要求运算速度很快,但运算结构相对比较简单,适应于FPGA 通过硬件实现。而在数字信号处理中,卷积器经常被用于图像滤波、边缘检测、图像锐化[3],我们在玻璃缺陷检测系统中,对采集的图像进行滤波去噪处理,以降低后续处理运算的压力。设对于两个长度分别为 m 和 n 的序列f (i)和g( j) ,我们可以给出一个长度为N = m + n -1 的输出序列:

VHDL 程序顶层文件代码如下:[4]

entity muladd is

port (

ain: in std_logic_vector(7 downto 0);

bin: in std_logic_vector(15 downto 0);

c: in std_logic;

dout: out std_logic_vector(15 downto 0)

);

end muladd;

architecture muladd_arch of muladd is

component adder16b is

port (

a: in std_logic _vector(15 downto 0);

b: in std_logic _vector(15 downto 0);

cin: in std_logic;

cout: out std_logic;

s: out std_logic _vector(15 downto 0)

);

end component;

component multi8 is

port(a:in std_logic_vector(7 downto 0);

c:in std_logic;

prod:out std_logic_vector(15 downto 0)

);

end component;

component fd16ce is

port(d:in std_logic_vector(15 downto 0);

ce,c,clr:in std_logic;

q:out std_logic_vector(15 downto 0)

);

end component;

signal pro,do:std_logic_vector(15 downto 0);

signal gndint ,vccint:std_logic;

begin

gndint《=‘0’;vccint《=’1’;

u1:multi8 port map(a=》ain(7 downto 0),c=》c,prod=》pro(15 downto 0));

u2:adder8b port map(a=》pro(15 downto 8),b=》bin(15 downto 8),

cin=》gndint,cout=》gndint,s=》do);

u3:fd16ce

portmap(d=》do,c=》c,ce=》vccint,clr=》gndint,q=》dout);

end muladd_arch;

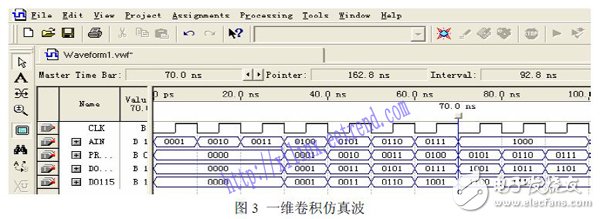

假设模板为{1,1,1},其仿真波形如图3 所示,在实际操作中,模板的值预置于每个单元中,很容易修改,可以方便的完成各种“窗口”的卷积运算。在卷积实现的基础上,只要采用不同系数的模板就可以完成各种运算,而且如果将卷积中的乘法和加法运算,分别换成比较运算和布尔运算中的“与”运算,那么卷积问题就换成了图像匹配问题了。如果将乘法运算改为加减法,将累加运算改为取最大最小值,就可以完成灰度图像的膨胀和腐蚀运算,这对于我们进行玻璃缺陷检测是有着极大帮助的。

4. 结束语

本文阐述了一种基于 FPGA 的玻璃缺陷图像采集处理系统方案,给出了具体的应用和设计框图,它体积小、系统集成度高,能有效的对图像进行高速采集处理。系统中采用的图像数据卷积算法,大大减轻DSP 后期数据处理的压力,在研究过程中表明,采用FPGA 实现图像低层次算法,设计者必须非常了解FPGA 器件内部的资源,同时系统中涉及到时钟信号、RAM、PCI 接口等各种器件,大量复用的数据、地址线要求设计者必须精心考虑逻辑结构和功能时序才能充分发挥出FPGA 的功能,取得理想的应用效果。

-

基于FPGA的远程图像采集系统设计2009-11-23 1269

-

基于Flash FPGA的电子内窥镜图像处理系统研究2017-08-31 752

-

基于DSP的图像处理系统的应用研究2012-12-19 0

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 0

-

基于FPGA玻璃缺陷图像采集处理系统2009-11-13 733

-

基于PCI总线和DSP的实时图像采集与处理系统2011-02-25 664

-

基于FPGA的网络图像采集处理系统设计2012-02-08 1910

-

基于FPGA多路机载冗余图像处理系统的设计方案2014-01-07 3194

-

基于FPGA的玻璃缺陷图像采集预处理系统设计2016-08-30 591

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1048

-

基于FPGA和DSP的高速图像处理系统2017-10-19 934

-

实时图像采集和处理系统的设计方法2017-10-31 1226

-

以FPGA和TMS320DM642为核心的实时图像采集和处理系统设计详解2018-07-16 2852

-

基于FPGA的实时视频图像采集处理系统2018-02-10 19922

-

如何使用FPGA实现玻璃缺陷图像采集预处理系统的设计2021-01-29 578

全部0条评论

快来发表一下你的评论吧 !