如何应用可编程逻辑器件PLD将高速视频内容连接到视频播放器

可编程逻辑

描述

从便携媒体播放器和手机,到视频游戏控制台,消费类视频应用的迅速增长需要大量不同的接口和适配器,以使用户在其电脑和各种娱乐信息设备间相互传输视频数据。

常用的消费类视频接口包括IEEE 1394(火线)、USB 2.0、DVI、HDMI和各种各样的无线标准。本文将介绍如何应用可编程逻辑器件(PLD)将不同的高速视频内容连接到视频播放器。

视频输入

USB 2.0是目前连接电脑和娱乐信息设备的主流高速视频标准。USB 2.0采用NRZI编码,带宽480Mb/s。从数码相机、机顶盒、信息家电,到MP3播放器、PDA、游戏控制台和3G手机,每种设备都有一两个USB 2.0接口。

USB主设备可为其外部设备供电,在5m电缆上最高可实现500mA、5V供电,最多可支持127个外部设备。数字电视(DTV)调谐器安装有USB模块,如果使用者将其连接到笔记本电脑,那么就可以在旅途中收看电视节目了。

标清视频解码的数据传输速率高达8Mb/s,而高清视频解码的传输速率要求是55Mb/s,都比USB 2.0的传输速率低很多。低成本的专用标准产品(ASSP)主/设备USB控制器可用做视频的PHY接口。输出经并行总线可以被送往PLD以进行数据处理,为了进一步集成,USB MAC(介质访问控制器)可以被设计到PLD中。

并行的视频数据可以经复用器被送至最终的视频解码器播放。USB 2.0 PHY芯片可被轻松连接至PLD的任意I/O引脚。大多数PLD的I/O引脚都可被编程实现3.3、2.5、1.8或1.5V LVTTL/LVCMOS。

IEEE 1394采用全双工8b/10b编码,传输速率最高可达400 Mb/s。火线接口可在没有主设备的情况下运行,进行点对点的通信,线缆最长可达4.5m,最多支持63个设备。对于相连的设备,可提供1.25A、 12V供电。低成本的物理层ASSP可用做与PLD的接口,以进一步增强数据处理。

视频输出

DVI和HDMI都基于最小化传输差分信号(TMDS)信道,采用8b/10b编码。A类HDMI向下兼容仅传输数字信号的DVI-D,这就意味着采用合适的适配器,DVI输出可以驱动HDMI监视器,反之亦然,但这时HDMI的音频和遥控点选功能不可用。

B类HDMI向下兼容双传输频道DVI。高带宽数字内容保护(HDCP)是用于保护数字娱乐内容的技术,可以防止最终用户观看或复制受限的内容。大部分HDMI接口支持HDCP规范,但DVI大多不支持HDCP。

现有的多种DVI和HDMI PHY芯片可与PLD直接接口。PLD通常都提供消除交错信号、色彩空间转换和2D滤波等图象的处理和增强功能。这些是当今面向大逻辑单元、DSP块和闪存的PLD的完美应用。

大多数消费电子产品都提供了用于控制和配置的I2C接口。

有很多参考设计可以下载和重用。为Altera的PLD产品系列优化的VHDL语言中有其I2C控制器。设计中,VHDL源文件的寄存器地址全被定义为常数,设计人员可以简单的进行自定义。内存基地址寄存器的地址定义为类属参数,也可方便的被修改和自定义。这一设计中的一个引脚给出了输出指示信号,可在I2C数据传输完成时被 MCU用做指示信号。

系统应用实例

大多数PLD都可接受不同格式和协议的数字视频源。PLD将输入的视频数据经过格式转换送入10b CCIR 656标准并行视频总线,从而通过现有的数字编码器(DENC)芯片播放这些视频流。这种总线可被选通或复用输出到DENC。

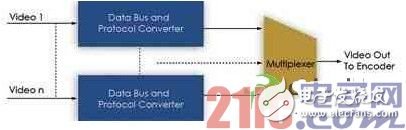

图1给出的PLD应用框图将数字视频源连接到视频播放。一个典型的高I/O引脚密度的PLD可容纳来自PHY芯片的并行视频数据。

图1 PLD可将数字视频源连接至视频播放

从USB和IEEE 1394等接口输入的不同数据总线首先要进入通用I/O引脚。第二步是将并行的视频数据转入类属视频总线,从而允许复用或选通以播放。I2C的参考设计用于控制PLD和板上ASSP的配置。

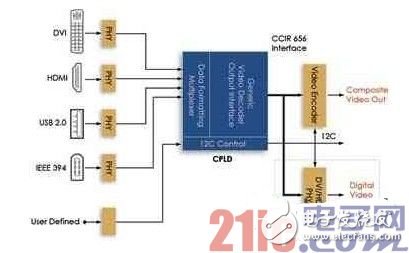

图2给出了整个系统的框图,包括视频PHY芯片到PLD的连接。PLD的输出产生了CCIR 656视频格式数据,经总线进入现有的视频编码器。采用I2C参考设计可完成对全部PLD和标准芯片的控制。

图2 视频PHY芯片经PLD生成CCIR 656格式的视频信号

-

什么是可编程逻辑2009-05-29 0

-

基于PLD的视频接口2018-12-28 0

-

基于可编程逻辑器件的高速视频内容与视频播放器连接2019-06-12 0

-

如何应用PLD将不同的高速视频内容连接到视频播放器2021-05-06 0

-

PLD可编程逻辑器件2021-07-22 0

-

第三十二讲 可编程逻辑器件及应用2009-03-30 1465

-

什么是PLD(可编程逻辑器件)2009-06-20 26312

-

可编程逻辑器件技术_pld技术2012-06-16 1223

-

可编程逻辑器件PLD介绍2019-02-23 1900

-

FPGA视频教程:可编程逻辑器件基础2019-12-11 2358

-

PLD可编程逻辑器件的原理详细讲解2021-01-21 1526

-

可编程逻辑器件PLD课件下载2021-08-13 1089

-

一文详细了解可编程逻辑器件(PLD)2022-03-22 8153

-

可编程逻辑器件测试2023-06-06 685

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2844

全部0条评论

快来发表一下你的评论吧 !