基于DSP乘法模块的高效FPGA器件在无线基站中的使用情况详解

可编程逻辑

描述

基于WiMax及其派生标准的新兴宽带无线协议需要越来越高的吞吐量和数据速率。这些协议提出的快速芯片速率和数字射频处理可以在使用FPGA方案的硬件上得到最佳的实现。

FPGA非常适合作为高性能、高性价比的解决方案来实现这些物理层协议中的数字功能,因为它们包括以下丰富的资源:

1.DSP模块,可以用来实现各种FIR滤波和FFT/IFFT操作所要求的乘法器和加法器/累加器功能;

2. SERDES收发器,可以支持无线前端与基带数字板之间的CPRI和OBSAI接口;

3. 重要的FPGA嵌入式RAM块存储器(EBR),可以用来存储滤波器系数,执行块交错以及实现FEC解码(Turbo、维特比、Reed-Solomon等);

4. 高速LVDS I/O,分别支持到DAC和来自ADC的宽并行接口。这些转换器定义了射频/模拟功能和廉价数字基带逻辑之间的界限。接口的速率越高,低成本FPGA解决方案便能集成更多的数字上变频/数字下变频功能。

本文重点讨论第一种资源,即DSP乘法模块。通过减少和优化DSP乘法模块在FFT和FIR中的实现,设计师可以在尽量减少资源使用的条件下满足吞吐量要求,从而允许用户使用最具性价比的现成FPGA器件。下面对这四种乘法器节省技术进行介绍。

用于WiMaxOFDM功能的高效复数乘法

WiMax系统设计的一个重要特征是支持正交频分复用(OFDM)。FPGA使得分别使用IFFT和FFT在离散时间内实现OFDM发送器和接收器变得特别容易。诸如802.16a等协议需要256样点的FFT。而802.16e这些协议要求多种FFT样点,或者可以灵活调整的FFT样点以适应动态信道和带宽要求(可扩展OFDMA)。

复数乘法

在执行256和1024样点FFT时,可通过Radix-4结构获得乘法器的最高效使用。FFT算法通过复用4样点离散傅里叶变换(DFT)蝶形结构进行分解。例如,一个16点的FFT可以通过按时间抽取、按频率抽取或其他相关分解方式用2级Radix-4 DFT结构实现。第1级由4个4样点DFT组成,第2级同样由4个4点DFT组成。由于每个DFT的输出要求在馈送给下一级之前为结果提供3个相位因子,因此第1级和第2级之间的9个相位因子需要9次复数乘法。

初看起来,执行一次复数乘法需要4个乘法器和2个加法/减法器。然而,该表达式可以重新写成另外一种只需3个乘法器、3个加法器和2个减法器的表达式。值得注意的是,加法器是在FPGA的内核逻辑中实现的,使用了丰富的逐位进位模式(ripple mode)的通用可编程逻辑单元(PLC)片。

如果D=Dr+jDi是复数数据,C=Cr+jCi是复数系数,那么复数乘法的标准表达式如下:

E1:R=D*C=(Dr+jDi)*(Cr+jCi)=Rr+jRi (1)

其中Rr=Dr*Cr-Di*Ci, Ri=Dr*Ci+Di*Cr

上述标准表达式要求使用4个乘法器。该表达式可以通过代数方法重新整理为:

E2: Rr=Dr*Cr-Di*Ci (2)

E3: Rr=Dr*Cr-Di*Ci+0 (3)

E4: Rr=Dr*Cr-Di*Ci+(Dr*Ci-Di*Cr)-(Dr*Ci-Di*Cr) (4)

E5: Rr=(Dr*Cr-Dr*Ci+Di*Cr-Di*Ci)+(Dr*Ci-Di*Cr) (5)

复数结果的新表达式是:

E6: Rr=[(Dr+Di)*(Cr-Ci)]+(Dr*Ci-Di*Cr) (3次乘法) (6)

E7: Ri=Dr*Ci+Di*Cr (复用来自Rr的乘积) (7)

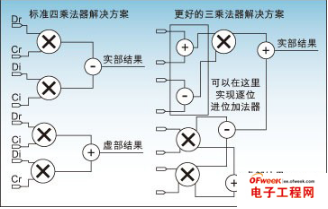

如图1所示,最优的复数乘法可以用3个乘法器、3个加法器和2个减法器实现。值得注意的是,在FPGA中,加法/减法模块所用的相对裸片面积要小于18×18的乘法器模块。

图1:采用4个和3个乘法器的复数乘法。

总之,所用乘法器数量减少25%可以带来下面两大好处之一:

1.在相同FFT吞吐量的条件下可以少用乘法器;

2.在乘法器数量不变的条件下可以提高FFT吞吐量。

数字上变频/下变频器中FIR滤波器的高效实现

如下的三个高效乘法器技术可用于实现FPGA中的数字上变频和下变频。这已经成为优化的重点领域,因为无线设计师需要满足将数据从非常高的采样速率向芯片处理速率转移的要求。数字下变频器/上变频器(DDC/DUC)子系统是基站内发送器/接收器的主要数字器件,以前是用昂贵的模拟/混合信号器件实现的。共有三种技术可以用来减少FPGA实现方案中的乘法器数量。

1.系数对称的FIR滤波器可节省乘法器;

2.分布式运算操作使用嵌入式块存储器;

3.级联积分梳状滤波器使用加法器。

上变频/下变频概述

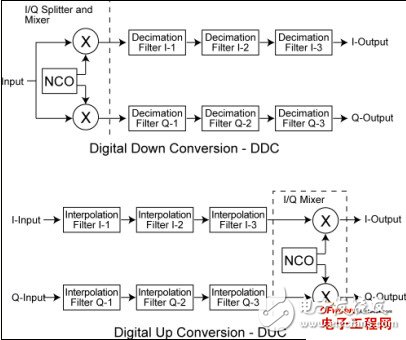

如图2中上半部分描述的那样,DDC由以下器件组成:一个基于数控振荡器(NCO)的I/Q分离器,它通过两个混频器将来自射频部分的输入信号用正弦和余弦波进行调制;一个抽取部分,可以由3级FIR抽取滤波器或后接级联积分梳状(CIC)滤波器的FIR抽取滤波器进行配置。

图2:DDC/DUC结构。

图2中的DUC由以下器件组成:3级FIR内插滤波器或后面接FIR内插滤波器的CIC滤波器;一个基于NCO和两个混频器的I/Q混频器,其在I、Q输出信号到达射频部分前对它们进行解调。请记住,抽取用于采样删除以达到较低的采样率,而内插用于增加外推样本以提高采样率。

变频器的通用实现指南

DDC/DUC系统是一个需要大量乘法器的系统。抽取和内插滤波器通常由乘法器和加法器阵列实现,而混频功能就是一个乘法器。利用面积优化方法实现NCO要基于使用复数乘法器的相移。

克服需要大量乘法器的系统所带来的挑战首先是要分解和级联滤波器:

1. 一个抽取/内插系数为N的大型FIR抽取滤波器或FIR内插滤波器可以分解成两个或三个抽取/内插系数分别为N1、N2和N3的较小、较简单的级联滤波器。抽取/内插系数满足以下等式:

E8: N=N1*N2*N3

2. 将FIR抽取滤波器或FIR内插滤波器分解成两个或三个独立滤波器可以减少实现整个滤波器所需的抽头总数。抽取或内插系数为N的单个滤波器需要大量的抽头(乘法器)才能满足基本的滤波器衰减和噪声特性要求。将滤波器分解成两个或三个更小和更简单的滤波器可以减少整个滤波系统的抽头数量。另外,第二和第三级联滤波器的较低采样率可以实现时间复用,从而进一步缩小实现的尺寸。

当滤波器阶数确定好后,还可以采取多种措施减少实际滤波器中的乘法器数量。下面将对此进行介绍。

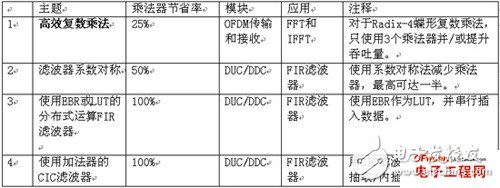

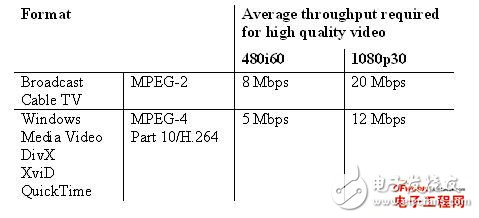

表1:可减少WiMax系统设计中乘法器数量的四种技术。

三种专用于变频器的乘法器节省技术

1. 对称抽取和内插滤波器

系数对称的DDC抽取滤波器和DUC内插滤波器可以用来获得最多50%的乘法器节省效果。在对称条件下,n个抽头的FIR滤波器系数h(0)、h(1)、…、h(n)满足h(k)=h(n-k){0≤k≤n}。

由于h(k)=h(n-k)、h(k)与两个相关样本之和的乘积可以一次完成,因此所需乘法器的数量可以最多减少2倍(对于偶数个系数)。在FPGA中,可以利用低成本的逐位进位逻辑实现使用相同系数的两个数据样本的加法。

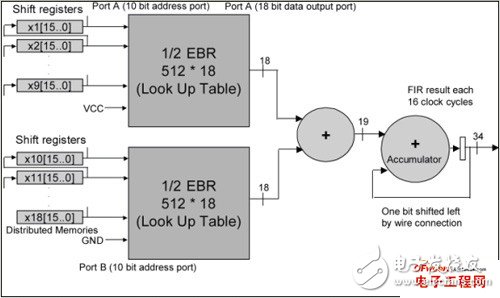

2. 通过分布式运算功能并利用EBR存储器块实现FIR滤波器

对乘法器密集应用(如DDC或DUC)来说,FPGA资源的高效使用特别重要。将存储器和LUT结构资源用作乘法器可以显着提升实现效率。EBR和这种结构的分布式存储器可以用作使用分布式存储器技术的FIR滤波器乘法器。分布式存储器技术也被称为软乘法技术,使用这种技术通常可以使FPGA器件中的乘法器数量增加2到5倍。

从图3可以看出如何使用EBR实现使用分布式算术技术的FIR滤波器。样本被串行移位进EBR地址总线。在EBR内部有一个预计算的结果乘法表以及带合适系数的各个输入样本比特(地址比特)总和。累加器将累加n个(n是样本比特分辨率)中间结果,并在n个时钟周期后提供完整的FIR滤波结果。

图3:将块存储器用作FIR乘法器。

3. CIC滤波器使用加法器而不是乘法器

用CIC乘法器代替某些内插/抽取FIR滤波器链部分是另一种减少实现所需乘法器数量的方法。CIC乘法器没??/下变频通常要求数百阶的大范围速率变化。高速率变化内插或抽取滤波器在硬件方面非常昂贵。CIC滤波器也被称为Hogenauer滤波器,可以用作低成本的高因数抽取或内插滤波器。它们可以用来在数字系统中取得任意的和很大的速率变化,并能够仅使用加法器和减法器高效实现。因为FPGA有很快的进位链用于实现加法器,因此CIC滤波器非常适合FPGA实现。积分器和梳状滤波器的结构与特性请参见表2。

表2:梳状滤波器和积分器的结构与特性。

利用IP核实现变频器和OFDM

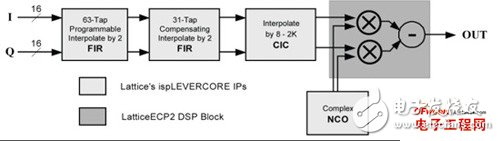

用Lattice的FPGA实现DDC或DUC变频器相当简单,因为FPGA提供了作为IP内核使用的重要组成器件。将CIC滤波器用作数据速率转换中内插器的应用如图4所示,它给出了用作数字无线应用中的变频器的CIC内插器的使用。

图4:用于数字无线电应用的数字上变频器。

数字上变频器使用以下一些IP内核配置:

1. FIR滤波器(63个抽头的内插滤波器);

2. FIR滤波器(31个抽头的内插滤波器);

3. CIC滤波器(速率在8到2K之间可编程的内插CIC滤波器);

4. NCO(带正弦和余弦输出的NCO)。

LatticeECP2/M的优势

LatticeECP2/M系列低成本FPGA具有多种与WiMax系统设计高度相关的高性能特性。在其他低成本FPGA系列器件中很难找到这些特性,而只能在昂贵的高端FPGA产品中才能找到:

1. 带硬连线的乘法器、加法器/累加器模块和管线级的高性能DSP模块;

2. 速率高达3.125Gbps的SERDES收发器通道,支持无线电头部和基带数字板之间的CPRI和OBSAI接口;

3. 在LatticeECP2/M存储器增强系列产品中数量众多的18kB EBR存储器块;

4. 支持ADC/DAC接口的高速LVDS I/O,输入和输出速率均可高达840Mbps;

5. 低成本的LatticeECP2/M系列器件均可提供这些丰富和高性能的资源,而价格远低于其他FPGA器件。WiMax系统设计师还能使用多种威廉希尔官方网站 减少所需DSP乘法器的数量,从而让用户有可能使用更小、更便宜的FPGA器件。

-

主流GPS芯片使用情况2017-11-27 3704

-

CUBEIDE运行完可以看RAM的使用情况,运行中可以实时查看RAM的使用情况吗?2024-03-12 0

-

如何计算FPGA的片上资源使用情况2019-06-17 0

-

FPGA和DSP在无线基站中的组合2019-07-26 0

-

如何查看RAM使用情况?2019-08-05 0

-

HBM产品在电机测试中的使用情况2021-01-22 0

-

电池使用情况统计信息2021-12-31 0

-

如何检查imx6中的GPU使用情况?2023-05-22 0

-

SoC如何查看内存使用情况2023-09-19 0

-

FPGA和DSP组合在无线基站中的应用2009-10-12 1068

-

EMC主要元器件工作原理与使用情况2012-08-09 4368

-

Python脚本使用时CPU使用情况检测过程详解2017-11-30 7648

-

一文解析FPGA的片上资源使用情况(组合逻辑及时序逻辑)2018-04-18 17273

-

浅谈电源设计中的电容使用情况2022-11-30 623

-

TMS320C64x在高性能DSP应用中的高速缓存使用情况2024-10-21 86

全部0条评论

快来发表一下你的评论吧 !