当AI遇到FPGA,低功耗智能探测系统不再是难题

人工智能

描述

从家庭控制中智能门铃和安全摄像头的存在检测,到零售应用中用于库存的对象计数,再到工业应用中物体和存在检测,越来越多的网络边缘应用正在不断推动新型AI解决方案面市。根据IHS Markit(现Omida)的预测,2018-2025年物联网设备数量将达到400亿,截至2022年,所有企业产生的数据中近50%会在传统数据中心或云端以外的地方进行处理。

但与此同时,市场一方面要求设计人员开发出性能比以往更高的解决方案;另一方面,延迟、带宽、隐私、功耗和成本问题又限制了他们依赖云的计算资源来执行分析。如何解决系统对于日益严格的功耗(毫瓦级)和小尺寸(5mm2到100mm2)要求?如何能够快速获得相应的硬件和软件工具、参考设计、演示示例和设计服务?莱迪思公司为此做出了有益的尝试。

Lattice sensAI再获重大更新

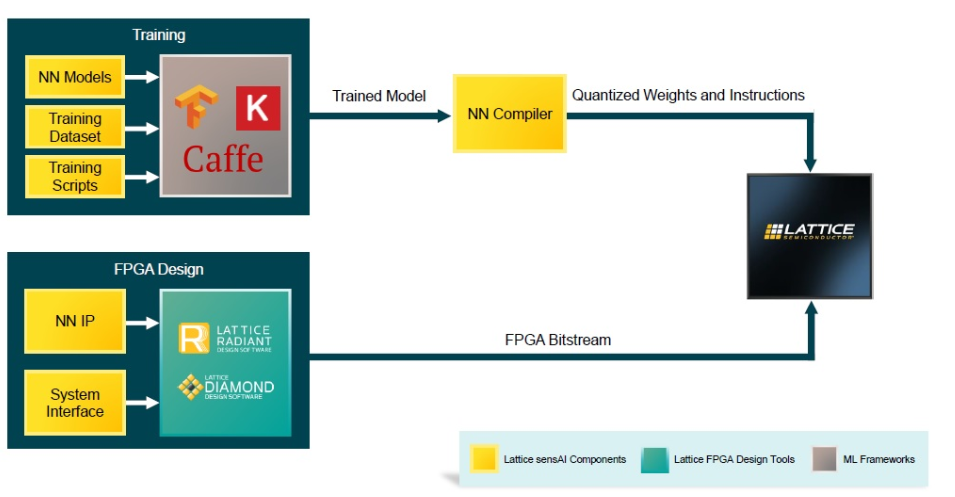

作为莱迪思推出的业界第一款用于网络边缘设备端AI处理的完整解决方案集合,sensAITM提供了供开发人员评估、开发和部署基于FPGA的机器学习/人工智能解决方案所需的全部资源,包括模块化硬件平台、演示示例、参考设计、神经网络IP核、软件开发工具和定制化设计服务。

图1:sensAI架构框图

2019年上半年,sensAI通过更新迎来10倍性能提升,这是由多个优化促成的,包括通过更新CNN IP和神经网络编译器、新增8位激活量化、智能层合并以及双DSP引擎等特性。而最令人感到兴奋的是它新增并优化了用于快速实现网络边缘常见AI应用的参考设计,为关键词检测、人脸识别、人员侦测、人员计数等赋予了更强大的特性。

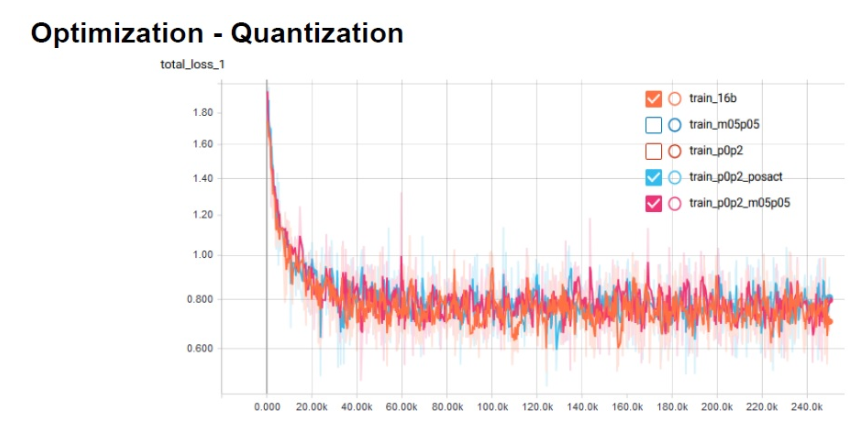

图2:在训练过程中支持8位量化可在神经网络模型训练过程中实现更高的精度

为了演示关键词检测系统的功能,工程师使用了搭载iCE40 UltraPlus FPGA的HiMax HM01B0 UPduino shield开发板。该开发板有两个直连到FPGA的I2S麦克风、用于FPGA设计的外部闪存、权重激活存储器、以及LED指示灯用以指示是否检测到关键词。用户可以直接对麦克风说话,一旦检测到关键词,LED就会亮起。

图3:关键词检测演示系统

图4左侧是针对低功耗运行进行优化、采用CMOS图像传感器的人员侦测演示,通过VGG8网络提供64 x 64 x 3的分辨率,该系统以每秒5帧的速率运行,使用iCE40 UltraPlus FPGA功耗仅为7mW;右侧是性能经优化的人员计数应用演示,同样也使用CMOS图像传感器,通过VGG8网络提供128 x 128 x 3的分辨率。该演示以每秒30帧的速率运行,使用ECP5-85K FPGA功耗为850mW。

图4:这些参考设计展示了sensAI提供的功耗与性能可选方案

Lattice人员识别参考设计方案也应用于售卖机上检测人员的出现,唤醒售卖机的内核。通过减少非人员靠近造成的误触发,或人员路过造成的误触发,达到减小功耗的目的。

2020年5月,sensAI又成功升级至3.0版本。

在此前支持ECP5/ECP5-5G和iCE40 UltraPlus 模块化硬件平台的基础上,新推出的sensAI 3.0版本支持CrossLink-NX™系列FPGA,运行sensAI软件的CrossLink-NX FPGA比之前版本降低了一半的功耗,同时实现性能翻倍,从而为监控/安防、机器人、汽车和计算领域的智能视觉应用带来功耗和性能上的再次突破。同时,它还拥有定制化卷积神经网络CNN IP并新增支持MobileNet v2、SSD和ResNet模型,这些灵活的加速器IP可简化常见CNN网络的实现,经优化后可更加充分利用FPGA的并行处理能力,开发人员可轻松编译经过训练的神经网络模型并将其下载到CrossLink-NX FPGA中。

图6:sensAI支持多种AI算法模型

CrossLink-NX FPGA采用28nm FD-SOI工艺制造,与同类FPGA竞品相比,功耗可降低75%。在CrossLink-NX FPGA上运行解决方案时,sensAI可提供多达2.5Mb的分布式内存、RAM块以及额外的DSP资源,MIPI I/O提供瞬时启动的性能可在不到3ms的时间内完成自我配置,而整个器件的配置也只需8ms。在基于CrossLink-NX的对象计数演示中,——基于VGG的对象计数演示拥有10帧/秒的性能,功耗仅为200mW。

当AI遇见超低功耗FPGA

拥有5K LUT的iCE40 UltraPlus FPGA可实现网络边缘实时在线的智能应用所需的神经网络模式匹配。其拥有5280个4输入LUT、自定义I/O、多达80Kb和1Mb的嵌入式存储器,睡眠电流低至75uA,工作电流仅为1-10mA,功耗低至1mW,硬件平台尺寸小至5.5mm2。为了满足各类应用的需求,还采用了包括从专为电子消费品和IoT设备优化的超小尺寸2.15 mm x 2.50 mm x 0.45 mm WLCSP封装,到低成本应用的0.5mm间距7x7mm QFN封装在内的多种封装选项。

功耗优化遥遥领先的原因,得益于其采用的分布式异构处理(Distributed Heterogenous Processing, DHP)架构。由于不使用云端执行算法,而是使用内置的数字信号处理器(DSP)执行重复的数字处理任务,因此大幅减少了功耗极大的应用处理器(AP)的计算负载,从而实现更长时间的睡眠模式以延长电池使用时间。另一方面,内置的神经网络软IP和编译器实现了灵活的机器学习/人工智能应用,消除了云端智能应用带来的延迟,降低了整个系统解决方案的成本。

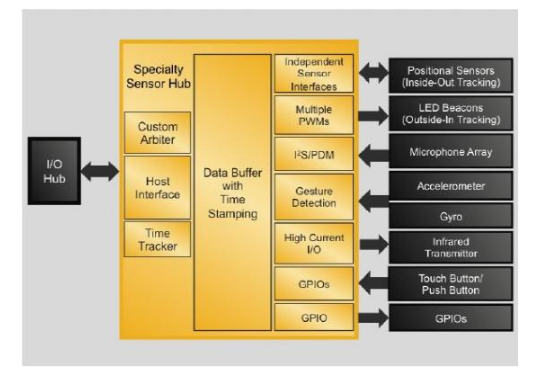

图7:iCE40 UltraPlus采用的分布式异构处理(DHP)架构

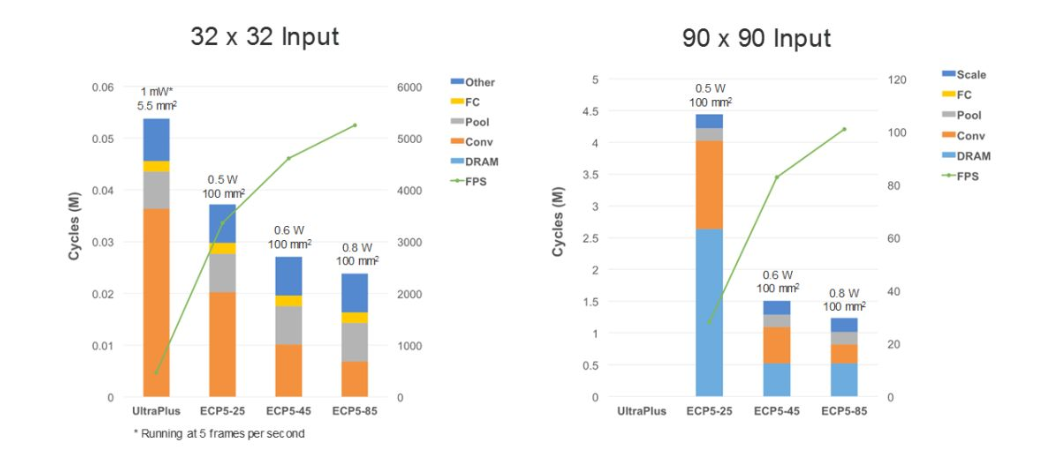

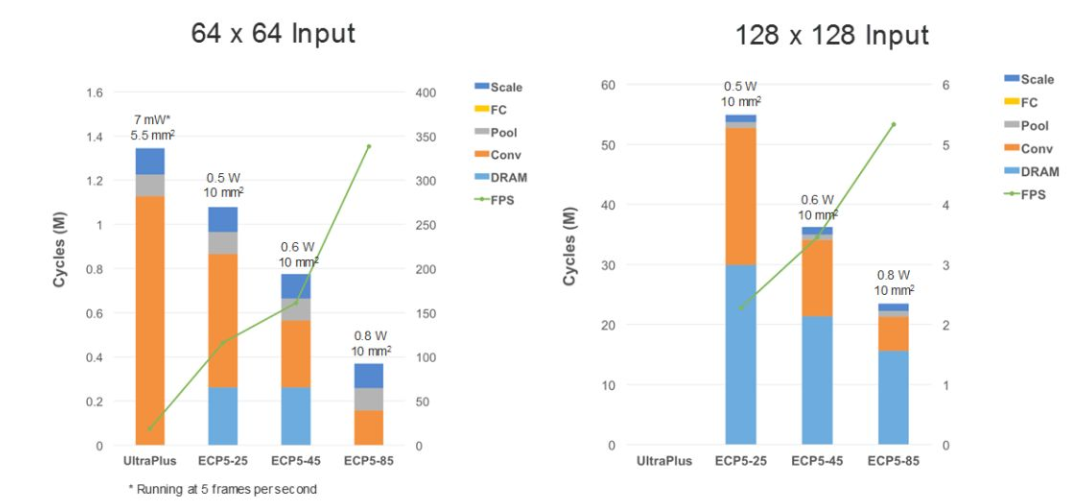

图8和图9描述了不同FPGA之间存在的资源差异如何影响到人脸检测和人员检测应用的性能和功耗。图8左侧的32x32输入示例中,橙色部分代表卷积层上运行的周期。在四个示例中,UltraPlus的乘法器数量最少,其他三片ECP5 FPGA的乘法器数量依次递增。随着乘法器数量的增加,卷积层所需的周期数减少;右侧的90x90输入示例中,在每个柱形图的底部有大面积的蓝色区域。这是由于设计更为复杂,需要占用外部DRAM,性能就有所折中。

图8:在UltraPlus和ECP5 FPGA上实现入门级和提高级人脸检测时的性能、功耗和占用面积

人员侦测应用的情况类似,两组分别采用了64x64输入和128x128输入的情况。同样,较多的乘法器会减少卷积层的负担,而依赖DRAM则会影响性能。

图9:在UltraPlus和ECP5 FPGA上实现简单和复杂人员检测时的性能、功耗和占用面积

其实,设计AI模型的最常见做法就是使用处理器,可能是GPU或者DSP,也有可能是微控制器(MCU)。不过,低端MCU可能连简单的AI模型也无法处理,高性能处理器又可能会违反设备的功耗和成本要求,但这正是低功耗FPGA发挥作用的地方。与增强处理器来处理算法的方式不同,莱迪思iCE40 UltraPlus FPGA可以作为MCU的协处理器,处理MCU无法解决的复杂任务之余,将功耗保持在要求范围内。

另一种思路是将低功耗FPGA作为单独运行的、完整的AI引擎,此时FPGA中的DSP就起到了关键作用。即便网络边缘设备没有其他的计算资源,也可以在不超出功耗、成本或威廉希尔官方网站 板尺寸预算的情况下添加AI功能,更何况它们还拥有支持快速演进算法所需的灵活性和可扩展性。

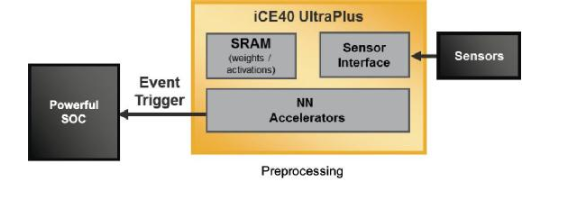

无论采取哪种方法,都意味着设计人员可以采用莱迪思sensAI以及一片低功耗的iCE40 UltraPlus FPGA对传感器数据进行预处理,从而最大程度地降低了向SoC或云端传输数据进行分析的成本。例如,如果是用在智能门铃上,sensAI会初步读取来自图像传感器的数据。如果判断为不是人,比如说是一只猫,那么系统就不会唤醒SoC或连接到云端作进一步处理。因此,这种方法可以最大程度降低数据传输成本和功耗。如果预处理系统判断门口的对象是人,则唤醒SoC作进一步处理。这能极大减少系统需要处理的数据量,同时降低功耗要求,这对于实时在线的网络边缘应用来说至关重要。

图10:基于iCE40 UltraPlus FPGA的sensAI会预处理传感器数据以判断该数据是否需要发送到SoC作进一步处理

结语:

莱迪思的FPGA具有独特的优势,可以满足网络边缘设备快速变化的市场需求。设计人员可以在不依赖云端的情况下,快速为网络边缘设备提供更多计算资源的其中一个方法是使用FPGA中本身的并行处理能力来加速神经网络性能。此外,通过使用针对低功耗运行而优化的低密度、小尺寸封装FPGA,设计人员可以满足新的消费和工业应用对功耗和尺寸的严格限制。

-

天基红外探测系统的杂散光分析与计算2010-04-24 0

-

BSD盲点探测系统2015-09-10 0

-

基于超声波的车辆运动探测系统毕业设计下载2018-07-19 0

-

当AI遇到FPGA,会发生什么化学反应呢?2020-10-23 0

-

基于DSP无人值守地面探测系统的硬件设计2021-02-04 0

-

怎样去设计一种无线传感器网络轴温探测系统?2021-06-02 0

-

舰船尾流实时探测系统设计2011-09-06 1430

-

基于STM32的红外火灾探测系统设计2017-09-28 853

-

基于方位测量的地下管线探测系统设计与研究2017-11-23 920

-

使用FPGA实现CCD探测系统的论文说明2019-11-29 827

-

地下车库CO探测系统的设置与安装2021-05-08 4896

-

浅谈无人机探测系统2021-06-04 2428

-

基于电场探测与无线组网的新型探测系统2021-06-19 636

-

实时地震探测系统开源分享2022-11-14 494

-

非吸烟环境烟雾探测系统2022-11-17 372

全部0条评论

快来发表一下你的评论吧 !