资料下载

8兆位(512 K×16)静态RAM,CY7C1051DV33

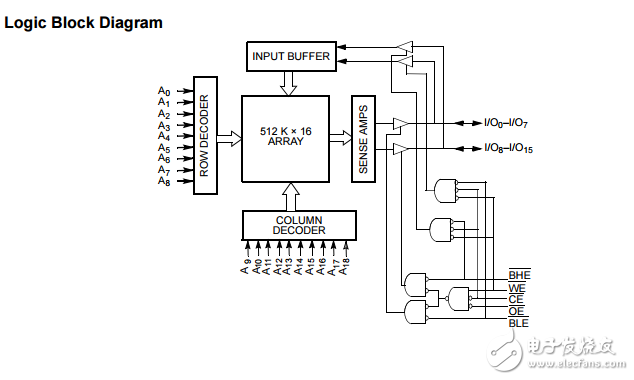

The CY7C1051DV33 is a high performance CMOS Static RAM organized as 512 K words by 16-bits. To write to the device, take Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte LOW Enable (BLE) is LOW, then data from I/O pins (I/O0–I/O7), is written into the location specified on the address pins (A0–A18)。 If Byte HIGH Enable (BHE) is LOW, then data from I/O pins (I/O8–I/O15) is written into the location specified on the address pins (A0–A18)。 To read from the device, take Chip Enable (CE) and Output Enable (OE) LOW while forcing the Write Enable (WE) HIGH. If Byte LOW Enable (BLE) is LOW, then data from the memory location specified by the address pins appears on I/O0–I/O7. If Byte HIGH Enable (BHE) is LOW, then data from memory appears on I/O8 to I/O15. See the Truth Table on page 10 for a complete description of read and write modes. The input/output pins (I/O0–I/O15) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or a write operation (CE LOW, and WE LOW) is in progress. The CY7C1051DV33 is available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout and a 48-ball FBGA package. For a complete list of related documentation,click here.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章