相关推荐

评论0

1.2w 543

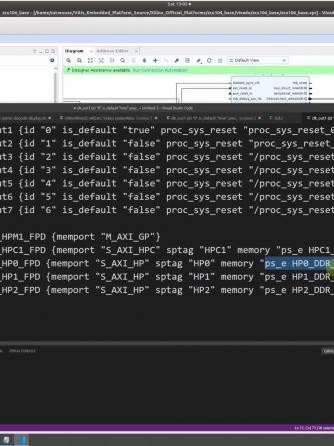

Vivado设置06【Vitis从入门到精通】#从零开始学Vitis

3130 221

八分钟掌握I2C核心知识点及时序

2945 52

FPGA实现千兆网UDP协议图传,上位机显示

2402 53

如何测量芯片电源的上电时序 #威廉希尔官方网站 设计

2396 70

基于FPGA的FFT快速傅里叶变换,数字信号处理常见算法-1

2315 24

千万别眨眼!资深工程师ZNYQ开发板快闪测评!创龙科技Zynq-7000系列异构多核SoC开发板#嵌入式开发

2085 178

#我在现场 高云半导体2021ELEXCON电子展新品展示

1839 26

一个方法解析多种XILINX(赛灵思)芯片命名规则! 你知道它涨价最疯狂的型号吗?芯片速度等级小速度快是误区?

1416 190

第九章 #时钟技术 9.1 同步时序逻辑的时钟(2)

1335 143

FPGA芯片结构,你都弄懂了吗?#跟着UP主一起创作吧 #硬件设计遇到过哪些坑?

1236 21

飞凌嵌入式国产芯片系列开发板知识问答大PK!

1195 57

FPGA与数字IC有什么区别?

2217 185

属于自己的DPU硬件01【Vitis从入门到精通】#从零开始学Vitis

2023 153

什么是CML电平#硬声新人计划

1823 127

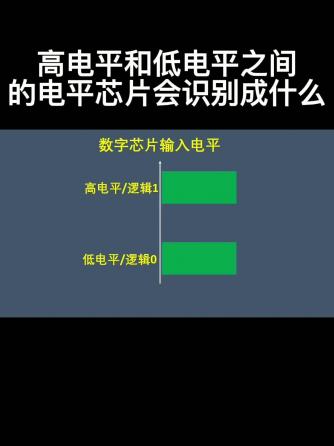

高电平和低电平之间的电平芯片会识别成什么#硬声新人计划

1748 118

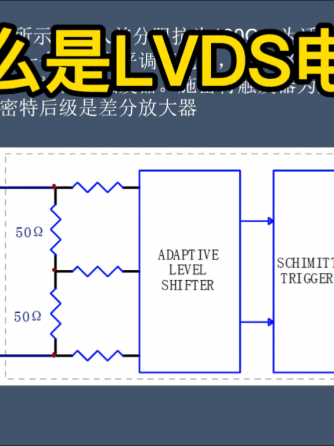

什么是LVDS电平#威廉希尔官方网站 设计

1641 203

分析KV260上的黑魔法gst框架01【KV260开发笔记】#从零开始学Vitis

1582 177

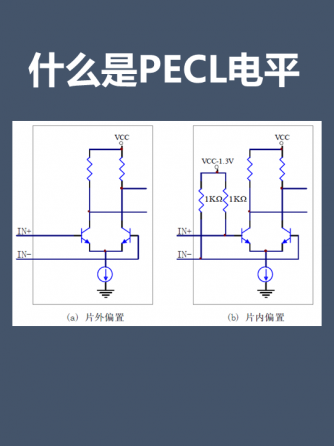

什么是PECL电平#硬声新人计划

1382 213

vitis2020.2编译平台更新说明【Vitis从入门到精通】#从零开始学Vitis

1160 90