ZYNQ中DMA与AXI4总线

描述

ZYNQ中DMA与AXI4总线

为什么在ZYNQ中DMA和AXI联系这么密切?通过上面的介绍我们知道ZYNQ中基本是以AXI总线完成相关功能的:

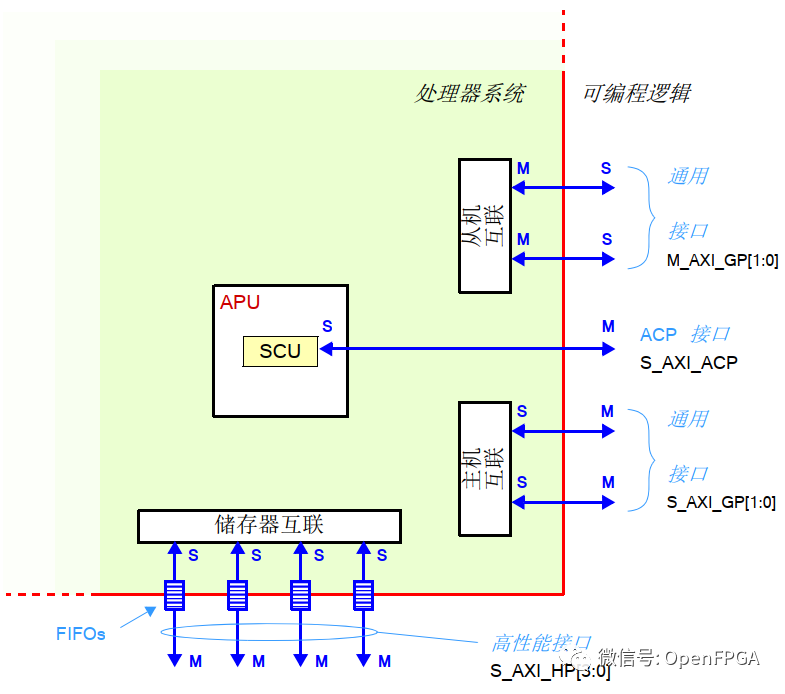

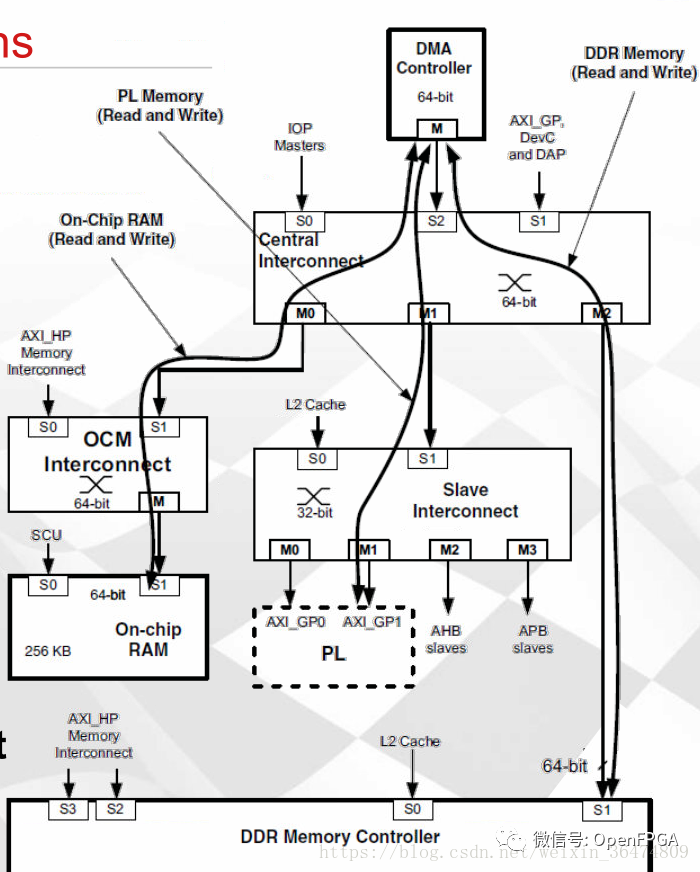

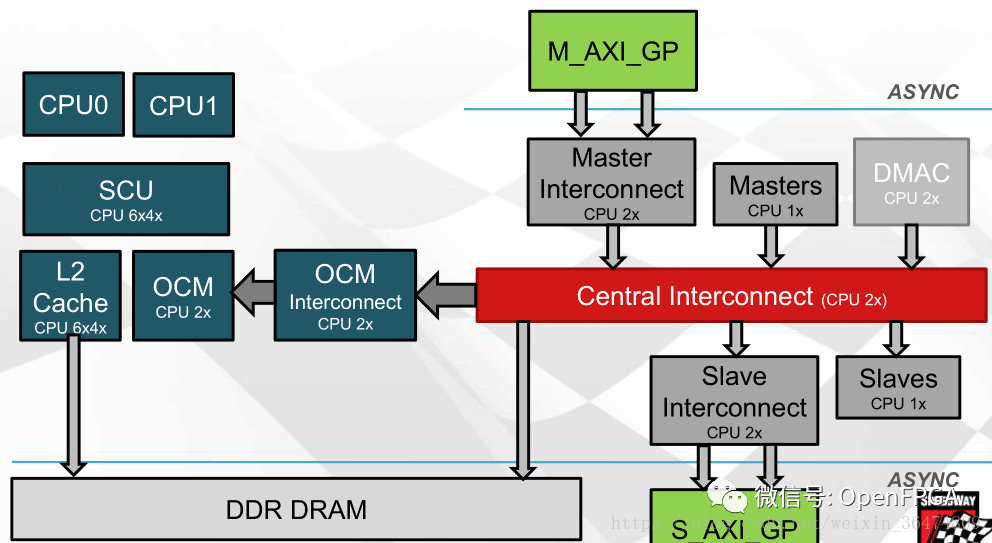

图4‑34 连接 PS 和 PL 的 AXI 互联和接口的构架

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口。

Xilinx提供的从AXI到AXI-Stream转换的IP核有:AXI-DMA,AXI-Datamover,AXI-FIFO-MM2S以及AXI-vDMA等

AXI-DMA:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换

AXI-FIFO-MM2S:实现从PS内存到PL通用传输通道AXI-GP<----->AXI-Stream的转换

AXI-Datamover:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换,只不过这次是完全由PL控制的,PS是完全被动的。

AXI-VDMA:实现从PS内存到PL高速传输高速通道AXI-HP<---->AXI-Stream的转换,只不过是专门针对视频、图像等二维数据的。

除了上面的还有一个AXI-CDMA IP核,这个是由PL完成的将数据从内存的一个位置搬移到另一个位置,无需CPU来插手。

上面的IP是完成总线协议转换,如果需要做某些处理(如变换、迭代、训练……),则需要生成一个自定义Stream类型IP,与上面的Stream接口连接起来,实现数据输入输出。用户的功能在自定义Stream类型IP中实现。

综上,在ZYNQ中DMA和AXI是不可分割的两者,所以介绍DMA也是必须的。

1.1.1DMA简介

DMA是一种内存访问技术,允许某些计算机内部的硬件子系统可以独立的直接读写内存,而不需要CPU介入处理,从而不需要CPU的大量中断负载,否则,CPU需要从来源把每一片段的数据复制到寄存器,然后在把他们再次写回到新的地方,在这个时间里,CPU就无法执行其他的任务。

DMA是一种快速数据传送方式,通常用来传送数据量较多的数据块。使用DMA时,CPU向DMA控制器发送一个存储器传输请求,这样当DMA控制器在传输的时候,CPU执行其他的操作,传输完成时DMA以中断的方式通知CPU。

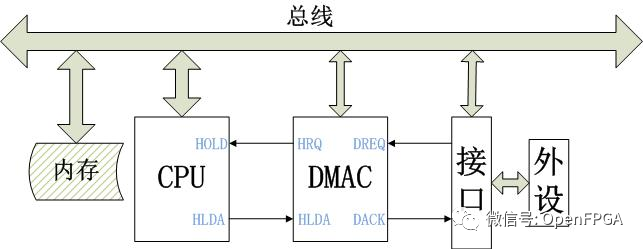

DMA传输过程的示意图为:

图4‑35 DMA传输过程的示意图

DMA的传输过程为:

1、为了配置用DMA传输数据到存储器,处理器(Cortex-A9)发出一条指令。

2、DMA控制器把数据从外设传输到存储器或者从存储器传输到存储器,从而较少CPU处理的事务量。

3、输出传输完成后,向CPU发出一个中断通知DMA传输可以关闭。

为了发起传输事务,DMA控制器必须得到以下信息:

(1)、源地址——数据被读出的地址

(2)、目的地址——数据被写入的地址

(3)、传输长度——应传输的字节数

我们可以理解,无论是程序控制方式还是中断控制方式,数据的传输都必须经过处理器。而在一个嵌入式微处理器为主控的应用系统中,当有大量数据在存储器和外设之间传输时,采用程序控制方式显然不合适,但是若采用中断控制方式,会造成中断次数过于频繁,不仅速度上不去,还需要处理器及时干预进行处理,大大降低了工作的效率。

然而,使用DMA的好处就是它不需要CPU的干预而直接服务外设,这样CPU就可以去处理别的事务,从而提高系统的效率,对于慢速设备,其作用只是降低CPU的使用率,但对于高速设备,它不只是降低CPU的使用率,而且能大大提高硬件设备的吞吐量。因为对于这种设备,CPU直接供应数据的速度太低。因CPU只能一个总线周期最多存取一次总线,而且对于处理器,它不能把内存中A地址的值直接搬到B地址。它只能先把A地址的值搬到一个寄存器,然后再从这个寄存器搬到B地址。也就是说,对于处理器,要花费两个总线周期才能将A地址的值送到B地址。而DMA就不同了,一般系统中的DMA都有突发(Burst)传输的能力,在这种模式下,DMA能一次传输几个甚至几十个字节的数据,所以使用DMA能使设备的吞吐能力大为增强。

鉴于上面的优势,系统中使用DMA是必要的,能够提高数据吞吐量,减轻了CPU的负担,使得整个系统的性能得到提高。

说了这么多优点,那么DMA缺点是什么呢?DMA传送期间CPU被挂起,部分或完全失去对系统总线的控制,这可能会影响CPU对中断请求的及时响应与处理。因此,在一些小系统或速度要求不高、数据传输量不大的系统中,一般并不用DMA方式。因为DMA允许外设直接访问内存,从而形成对总线的独占。这在实时性强的硬实时系统嵌入式开发中将会造成中断延时过长。

DMAC为DMA控制器

DMA传送虽然脱离CPU的控制,但并不是说DMA传送不需要进行控制和管理。通常是采用DMA控制器来取代CPU,负责DMA传送的全过程控制。目前DMA控制器都是可编程的大规模集成芯片。

图4‑36 DMAC结构

DMA控制器是内存储器同外设之间进行高速数据传送时的硬件控制威廉希尔官方网站 ,是一种实现直接数据传送的专用处理器,它必须能取代在程序控制传送中由CPU和软件所完成的各项功能。它的主要功能是:

(1)DMAC同外设之间有一对联络信号线--外设的DMA请求信号DREQ以及 DMAC向外设发出的DMA响应信号DACK;(如下图)

(2)DMAC在接收到DREQ后,同CPU之间也有一对联络信号线--DMAC向CPU 发出总线请求信号(HOLD或BUSRQ),CPU在当前总线周期结束后向DMAC发出总线响应信号(HLDA或BUSAK),DMAC接管对总线的控制权,进入DMA操作方式;

(3)能发出地址信息,对存储器寻址,并修改地址指针,DMAC内部必须有能自动加1或减1的地址寄存器;

(4)能决定传送的字节数,并能判断DMA传送是否结束。DMA内部必须有能自动减1的字计数寄存器,计数结束产生终止计数信号;

(5)能发出DMA结束信号,释放总线,使CPU恢复总线控制权;

(6)能发出读、写控制信号,包括存储器访问信号和I/O访问信号。DMAC内部必须有时序和读写控制逻辑。

图4‑37 DMAC在DMA中的作用示意图(一)

图4‑38 DMAC在DMA中的作用示意图(二)

责任编辑:xj

原文标题:ZYNQ中DMA与AXI4总线-DMA简介

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 0

-

Adam Taylor玩转MicroZed系列67:AXI DMA II2017-02-08 385

-

AXI4接口协议的基础知识2020-09-23 6065

-

一文详解ZYNQ中的DMA与AXI4总线2020-09-24 5303

-

Zynq中AXI4-Lite和AXI-Stream功能介绍2020-09-27 8900

-

Xilinx zynq AXI总线全面解读2020-12-04 7137

-

ZYNQ SOC案例开发:AXI DMA使用解析及环路测试2020-12-31 8654

-

深入AXI4总线一握手机制2021-03-17 890

-

深入 AXI4总线 (四):RAM 读取实战2022-02-07 686

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 8590

-

使用AXI4总线实现视频输入输出2022-10-11 5782

-

AXI3与AXI4写响应的依赖区别2023-03-30 1095

-

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】2023-06-21 2279

-

漫谈AMBA总线-AXI4协议的基本介绍2024-01-17 2401

-

SoC设计中总线协议AXI4与AXI3的主要区别详解2024-05-10 6698

全部0条评论

快来发表一下你的评论吧 !