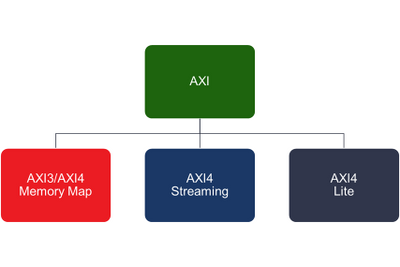

AXI-4 Memory Mapped也被称之为AXI-4 Full,它是AXI4接口协议的基础,其他AXI4接口是该接口的变形。总体而言,AXI-4 Memory Mapped由五个通道构成,如下图所示:写地址通道、写数据通道、写响应通道、读地址通道和读数据通道。

上图中的箭头方向表明了信号的流向(主到从或从到主)。例如:对于写通道,主设备把数据发送给从设备,同时从设备给主设备发送响应信号,表明数据交易的完成。对于读通道,从设备根据主设备提供的地址信息把数据发送给主设备。

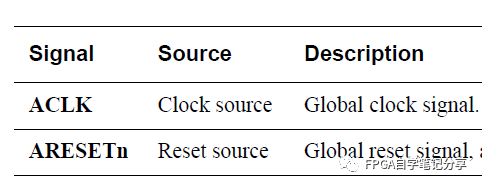

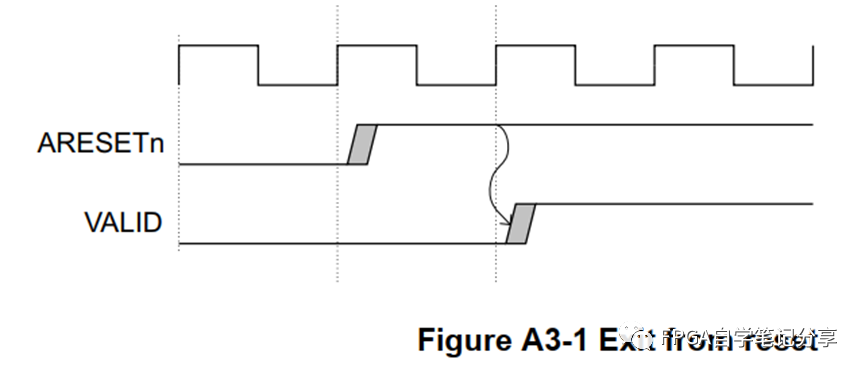

每个通道都有自己的VALID/READY握手信号对,如下图所示。只有当握手信号同时有效时,该通道其他信号才有效。

写地址通道

对于写地址通道,这里主要介绍以下几个信号,如下图所示。写地址通道的信号名称均以AW开头。从图中可以看到除AWREADY之外,其余信号均由主设备产生传递给从设备。AWADDR为写数据第一个Byte的地址,从设备会根据此值计算后续Byte地址。AWLEN+1即为突发长度,表明了发送数据的个数(不是Byte数)。

-

接口协议

+关注

关注

5文章

41浏览量

18539 -

AXI4

+关注

关注

0文章

20浏览量

8888

原文标题:深入理解AXI-4 Memory Mapped 接口协议

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何使用AXI VIP在AXI4(Full)主接口中执行验证和查找错误

看看在SpinalHDL中AXI4总线互联IP的设计

SoC Designer AXI4协议包的用户指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流协议断言用户指南

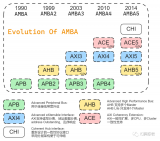

何谓 AXI?关于AXI3/AXI4的相关基础知识

AXI3与AXI4写响应的依赖区别

漫谈AMBA总线-AXI4协议的基本介绍

SoC设计中总线协议AXI4与AXI3的主要区别详解

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

AMBA AXI4接口协议概述

AXI4接口协议的基础知识

AXI4接口协议的基础知识

评论