Xilinx 7系列中FPGA架构丰富的时钟资源介绍

描述

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源是最佳的,然后通过使用适当的I/O和时钟缓冲器来访问这些时钟路由资源。该章节包括:

时钟缓冲选择考虑

时钟输入管脚

1.时钟缓冲器选择考虑

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG)是最常用的时钟布线资源。这些真正的全局时钟可以连接到器件的任何位置。但是在某些情况下,出于性能、功能或时钟资源可用性的原因,使用备用时钟缓冲器更为有利。最好在以下情况下使用BUFG:

设计或设计的一部分可以覆盖整个器件的大面积区域,功能的本地化是不可能的。

硬件功能块,如块RAM、DSP或集成IP,跨越多个时钟区域,级联或需要连接到不在附近的CLB。

同步(glitch free)或异步时钟切换,应用程序能够从停止的时钟切换或选择具有不同频率的时钟(例如,用于降低功耗)。

时钟使能(CE)功能可用于在非运行期间降低功率。然而,在大多数情况下,由于时序(CE延迟)的限制,CE不能够用于在时钟元件处模拟真实的CE逻辑功能。

CE功能可用于在器件启动后同步已初始化的时钟元件。

图1、串行LVDS ADC接口常见设计

BUFR和BUFIO组合的主要目的是支持源同步接口(如图1所示)。当一个接口被放置在一个区域中时,BUFIO对SelectIOs的高速侧进行时钟控制,BUFR以较低的速度将解串器/串行器侧时钟送入提供时钟域传输功能的FPGA逻辑中。对于需要更多逻辑和/或I/O的接口,BUFMR(BUFMRCE)用于将时钟域传输功能扩展到上面和下面的(above and below)时钟区域。当MMCM/PLL不能使用或不可用于分频功能时,需要与源同步I/O用例无关的分频时钟的某些类型的应用程序可以将BUFR用作简单的时钟分频器。在这种情况下,必须特别注意时序和偏移,因为这不是BUFR的主要目的。有关选择资源计时的更多信息,请参阅UG471,7系列FPGA SelectIO资源用户指南。

水平时钟缓冲器BUFH(BUFHCE)严格来说是一个区域资源,不能跨越上面或下面的时钟区域。与BUFR不同,BUFH没有分频时钟的能力。

BUFHs类似于全球时钟资源,只是在区域基础上跨越两个水平区域。

BUFHs能够作为MMCM/PLL的反馈,时钟插入延迟可以得到补偿。

当接口或逻辑云位于一个时钟区域或两个水平相邻的时钟区域时,BUFHs是首选的时钟资源。

BUFH还具有时钟使能引脚(BUFHCE),当逻辑或接口及其相关逻辑未激活时,可使用该引脚降低动态功耗。

时钟使能功能可在时钟周期的基础上提供门控时钟。

与全局时钟树类似,BUFH还可以连接到CLB(enable/reset)中的非时钟资源,具有更好的偏移特性。

BUFH也可用于同步启动时钟区域中时钟元件。

2.时钟输入规则

外部用户时钟必须通过称为clock-capable(CC)输入的差分时钟管脚对引入FPGA。时钟输入管脚支持对内部全局和区域时钟资源的专用高速访问。时钟输入管脚使用专用路由,必须用于时钟输入,以保证各种时钟的时序特征。使用本地互联的一般目的I/O不应用于时钟信号。

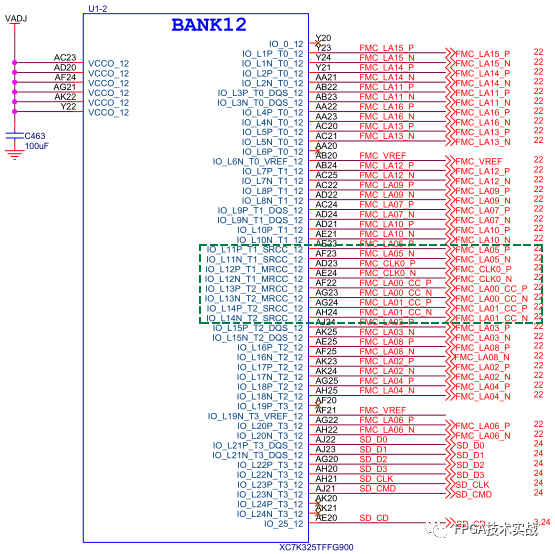

图2、_CC时钟管脚连接每个I/O Bank位于一个时钟区域,包括50个I/O引脚。在每个I/O bank中每个I/O组中的50个I/O管脚中,有4个支持时钟的输入管脚对(共8个管脚)。每个时钟输入:

可连接到PCB上的差分或单端时钟

可为任何I/O标准配置,包括差分I/O标准

有一个P-side(主)和一个N-side(从)

如果单端时钟连接到差分时钟管脚对的P侧,则N侧不能用作另一个单端时钟管脚,它只能用作用户I/O。时钟输入管脚在每个I/O Bank中有2个MRCCs和2个SRCCs对。SRCC访问单个时钟区域和全局时钟树,以及同一列中上下的其他CMTs。SRCC可以驱动:

同一时钟区域内的区域时钟线(BUFR、BUFH、BUFIO)。

同一时钟区域和相邻时钟区域的CMT。

位于器件的上/下半部分的全局时钟线(BUFG)。

MRCCs可以访问多个时钟区域和全局时钟树。MRCCs的功能与SRCCs相同,还可以驱动多时钟区域缓冲器(BUFMR)来访问多达三个时钟区域。如果不用作时钟,时钟输入管脚可以用作常规I/O。当用作常规I/O时,支持时钟的输入引脚可以配置为任何单端或差分I/O标准。时钟输入管脚可以连接到同一时钟区域的CMT,和该时钟区域的上下的CMT,但具有一定的限制。

2.1 单个时钟驱动单个CMT

当时钟输入驱动单个CMT时,时钟输入管脚和CMT(MMCM/PLL)必须在同一时钟区域。

2.2 单个时钟驱动多个CMTs

一个时钟输入可以驱动同一列中的其他CMT。在这种情况下,一个MMCM/PLL必须被放置在与时钟输入管脚相同的时钟区域中。在相邻区域放置附加的CMT是更为优化的,但是在同一列中,可以驱动比一个CMT更远的CMT。CMT中使用的资源必须相同,才能自动放置此配置而不使用CLOCK_DEDICATED_ROUTE约束。如果需要混合MMCMs/PLL,则应首先将其置于同一CMT中。如果有必要从不在同一时钟区域的时钟输入管脚驱动CMT,并且在与时钟输入管脚相同的时钟区域中没有MMCM/PLL,则必须设置属性CLOCK_DEDICATED_ROUTE = BACKBONE。在这种情况下,MMCM或PLL不能正确地将输出与输入时钟对齐,即存在时钟偏移。在同一列中专用资源驱动CMT是有限制的。一些Xilinx IP使用这些资源,从而使它们不可用于其他设计用途,并导致设计无法布线。如果到其他时钟区域的专用路由不可用,则将CLOCK_DEDICATED_ROUTE设置为FALSE将允许使用本地互连逻辑,尽管这会导致更长的无补偿延迟。如果由普通的IO管脚驱动全局时钟资源,比如BUFG或者MMCM,则CLOCK_DEDICATED_ROUTE = FALSE。

2.3 时钟输入管脚放置规则

在创建初始设计之前,手动选择支持时钟的输入引脚时,有两个主要考虑因素:

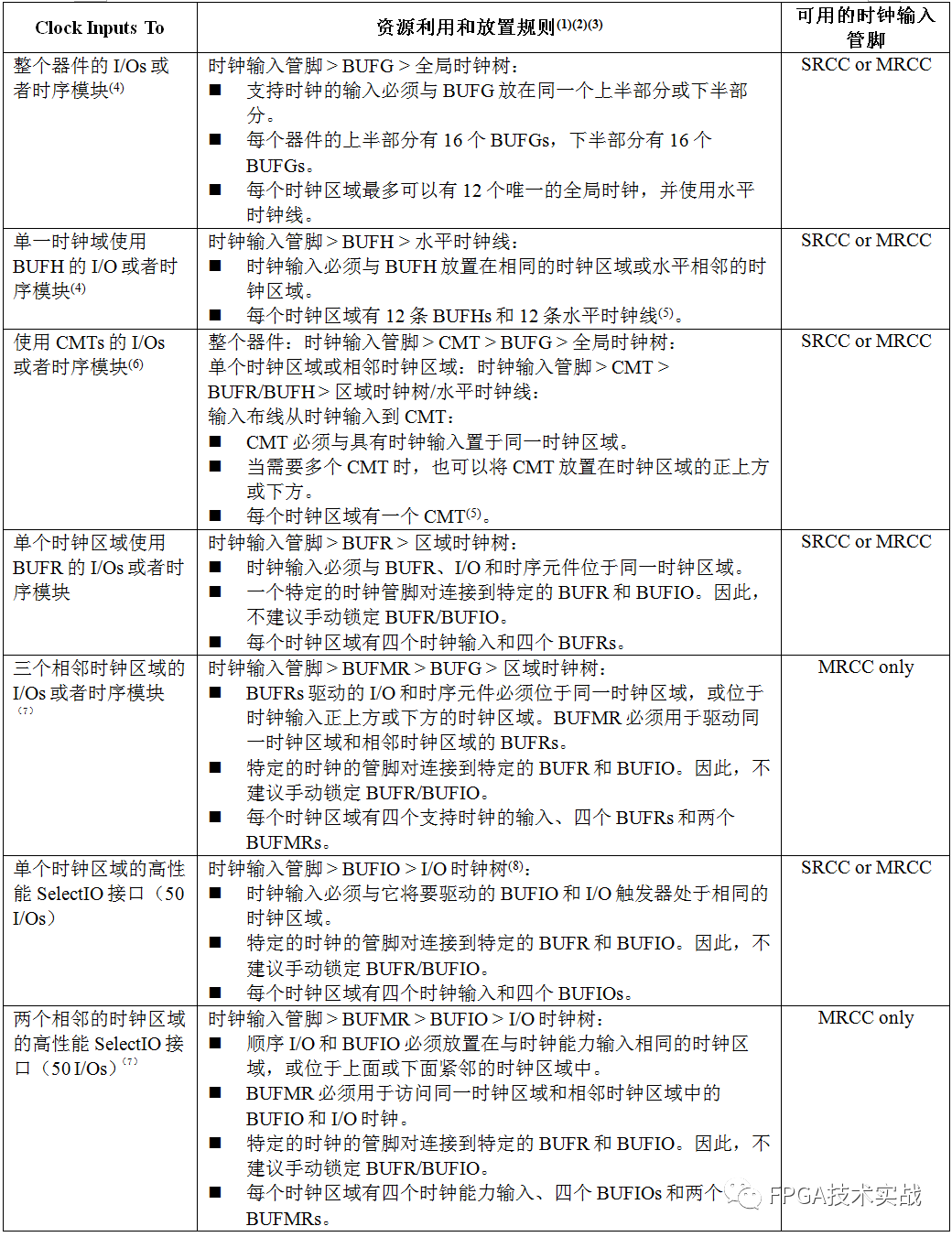

确保支持时钟输入可以连接到所需的时钟资源。表所示的布局规则确保连通性。

确保所需的时钟资源是可用的,并且没有被设计的另一部分使用。确保通过时钟输入管脚进入的外部时钟和来自IP的内部生成时钟不会在访问内部时钟网络时发生冲突,最好的方法是构建包含所需时钟网络和IP的初始设计,并通过实现工具运行它。这大大增加了检查和信心,即引脚不需要由于时钟原因而改变。

遵循表2-1所示的放置规则,以确保具有时钟输入引脚选择能够访问所需的内部时钟网络。每个I/O Bank位于在一个时钟区域中。注:通过确保正确选择具有时钟输入引脚的位置,避免昂贵的威廉希尔官方网站 板重新设计和差的时钟时序。

表1、时钟输入放置规则在相同的封装器件之间迁移时,将BUFG组织为16个top和16个bottom资源的上/下中心线可能相对于其他列发生了移动。具体地说,I/O列会更改与顶部/底部BUFGs的对齐方式。这会导致访问BUFG的时钟输入引脚的不同对齐方式。图1显示了使用XC7K325T和XC7K160T器件的中心对齐示例。在这种情况下,当从相同封装中的大器件移动到小器件时,中心线较低(相对于I/O列),或者从小器件移动到大器件时,中心线更高。如果时钟输入引脚被定位,设计可以是不可布线的。

图3、使用XC7K325T和XC7K160T器件的中心对齐示例当迁移到相同封装的一个较小的器件时,也可能会出现这样的情况:较大器件的南侧的所有BUFG都已被利用,而没有更多的BUFG可用。见UG475:7系列FPGA封装和引脚输出规范,用于BUFG和I/O组对准。另外,具有多个超级逻辑区域(SLR)的器件在同一个包中从单个SLR中的单片路径迁移时可能具有类似的限制。

原文标题:Xilinx 7系列FPGA架构之时钟资源(二)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

xilinx公司的7系列FPGA应用指南2012-08-07 2136

-

Xilinx 7 系列的时钟资源(1)2017-02-08 807

-

Xilinx全局时钟的使用和DCM模块的使用2017-11-22 10289

-

Xilinx 7系列FPGA介绍2020-11-13 15074

-

Xilinx 7系列FPGA时钟资源2020-12-10 940

-

Xilinx 7 系列FPGA中的Serdes总结2020-12-31 1473

-

Xilinx 7系列FPGA简介--选型参考2021-01-30 1992

-

Xilinx 7系列FPGA架构的区域时钟资源介绍2021-03-22 5147

-

FPGA架构中的全局时钟资源介绍2021-03-22 13199

-

Xilinx 7系列FPGA时钟和前几代有什么差异?2021-03-22 4941

-

Xilinx 7系列FPGA架构之时钟路由资源介绍2022-07-22 3039

-

Xilinx 7系列FPGA的时钟资源架构2022-07-28 1516

-

Xilinx FPGA时钟资源概述2023-07-24 908

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 2620

-

Xilinx 7系列FPGA中MMCM和PLL的区别2023-11-17 6867

全部0条评论

快来发表一下你的评论吧 !