在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。本文为您解惑......

2013-07-23 09:25:53 19707

19707

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 13866

13866

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。

2022-07-14 09:15:35 1538

1538 7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

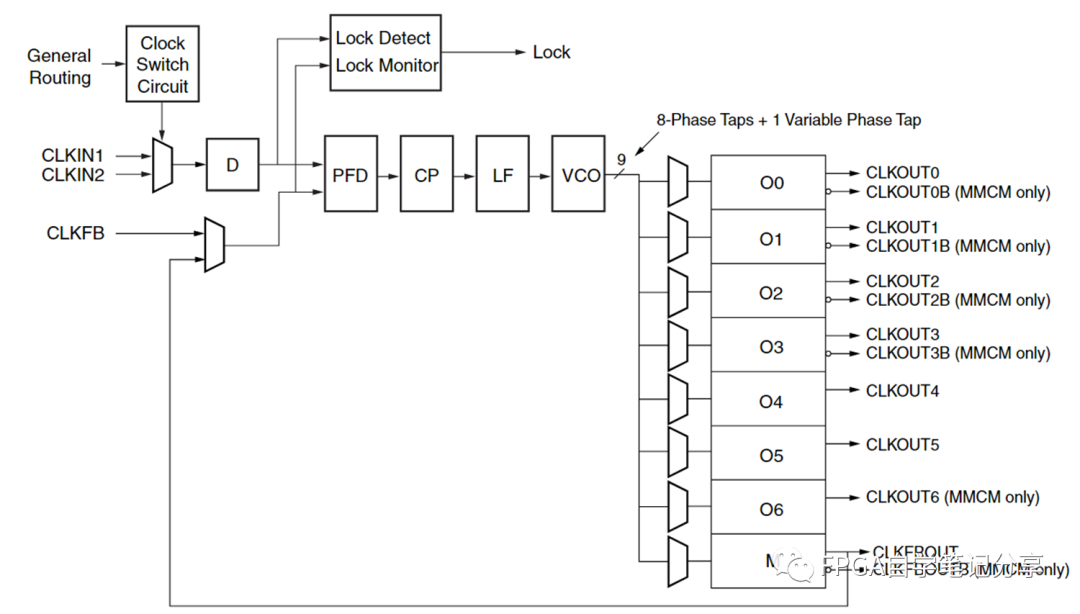

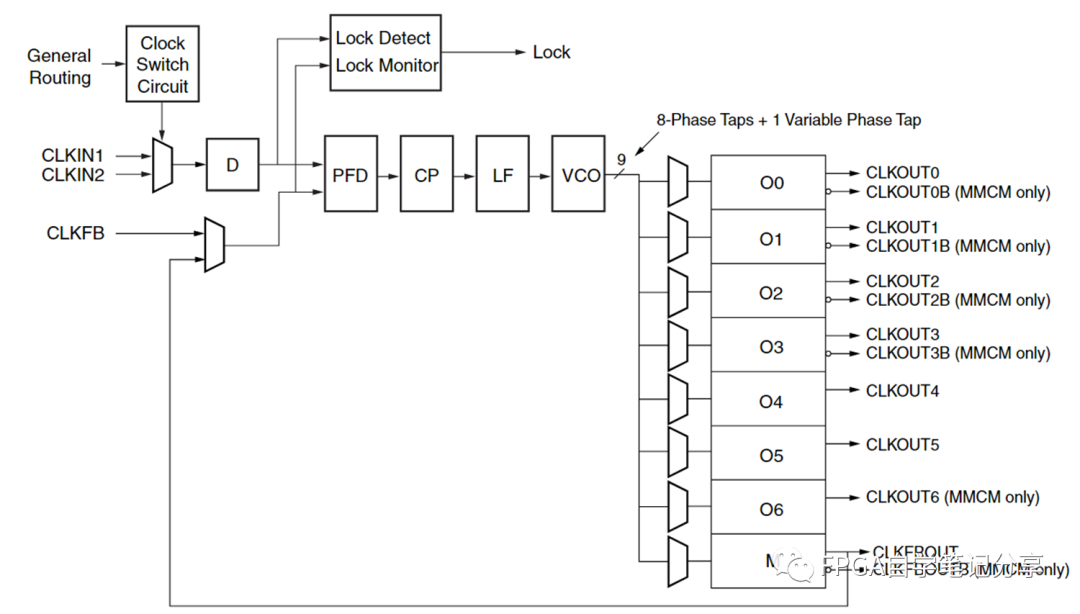

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 输入输出端口 从Implemented Design中可以看到FPGA中资源大致分布如下。中间蓝色是CLB可编程逻辑块、DSP或BRAM,两侧的彩色矩形块是I/O接口和收发器,划分的方块是不同的时钟域 Configurable Logic Block (CLB)可编程逻

2022-12-27 15:54:52 1788

1788 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

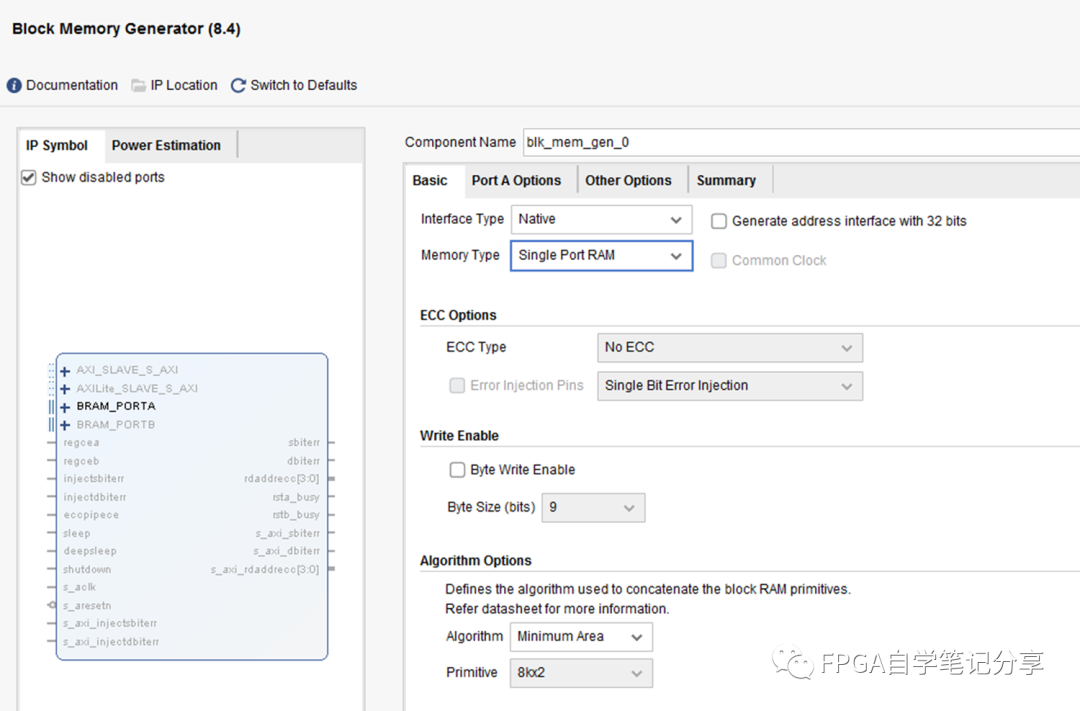

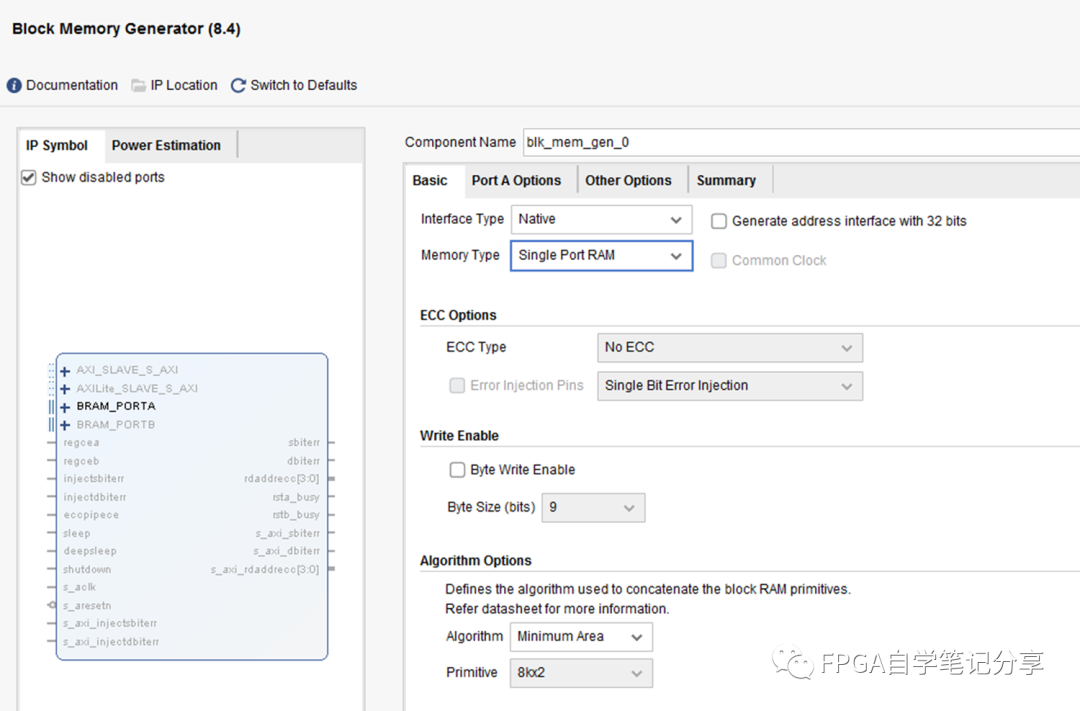

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

FPGA设计高级技巧Xilinx篇目录414.3 减少关键路径的逻辑级数.............................................404.2IF语句和Case语句速度

2012-08-11 11:43:17

XILINX FPGA 芯片整体架构是如何构成的?XILINX FPGA 芯片有哪些资源?

2021-10-29 06:26:23

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

`Xilinx FPGA入门连载23:PLL实例之功能简介特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 PLL概述PLL

2015-11-10 08:44:06

`Xilinx FPGA入门连载40:SRAM读写测试之设计概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能简介如图所示,本

2015-12-18 12:57:01

Xilinx FPGA入门连载43:FPGA片内ROM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-06 12:22:53

Xilinx FPGA入门连载47:FPGA片内RAM实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-01-20 12:28:28

Xilinx FPGA入门连载51:FPGA片内FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述该工程

2016-02-26 10:26:05

`Xilinx FPGA入门连载55:FPGA 片内异步FIFO实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入门连载59:FPGA 片内ROM FIFO RAM联合实例之功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s

2016-03-16 12:43:36

`Xilinx FPGA入门连载67:VGA概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1VGA概述VGA(Video

2016-04-08 09:55:22

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

指南 -- Modelsim仿真验证Lesson13 特权Xilinx FPGA SF-SP6入门指南 -- PWM蜂鸣器驱动之功能概述Lesson14 特权Xilinx FPGA SF-SP6入门指南

2015-07-22 11:49:20

⑴ 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)⑵ 如果,对内部特定资源,曾有

2012-03-08 11:03:49

`如题,打算拿手里的十万逻辑资源Altera板子交换Xilinx板子,现在只打算换Xilinx的FPGA的板子,可以是自己做的或者是其他,但一定要好使的!板子是自己设计的,也是自己焊接的,焊接的比较

2015-06-19 21:38:36

和原理11.1.1 时序分析的作用11.1.2 静态时序分析原理11.1.3 时序分析的基础知识11.2 Xilinx FPGA中的时钟资源11.2.1 全局时钟资源11.2.2 第二全局时钟资源

2012-04-24 09:23:33

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说

2020-04-25 07:00:00

RAM)的时延和抖动都为最小。为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8

2019-10-22 06:01:34

FPGA的特点及其发展趋势IP资源复用理念与IP Core设计基于Xilinx FPGA的嵌入式系统设计

2021-04-30 07:21:50

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。不过对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。

2019-09-18 08:26:21

已经检查过,我有正确的引脚从pcie插槽中点击100M refclk。我的问题 - 1)用于FPGA的xilinx gtx phy是否支持SSC时钟?2)如果我在主机端启用或取消了SSC时钟,那么我

2019-04-01 13:22:15

小弟最近在研究FPGA时钟资源的手册,遇到一个问题想请教各位大神。在Virtex6系列FPGA中,Bank分为top层和bottom层,请问我怎么查看一个Bank到底是在top层还是在bottom层

2015-02-10 10:30:25

DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟威廉希尔官方网站

是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 目前,大型设计一般推荐使用同步时序威廉希尔官方网站

。同步时序威廉希尔官方网站

基于时钟触发沿设计,对时钟的周期

2010-11-03 16:24:44 121

121 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时

2011-01-04 11:26:35 1991

1991 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA威廉希尔官方网站

原理与系统设计

2012-07-31 16:20:42 11268

11268

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义

2017-02-08 05:31:40 2048

2048

谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

1315 目前,大型设计一般推荐使用同步时序威廉希尔官方网站

。同步时序威廉希尔官方网站

基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-02-11 11:34:11 4223

4223 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

目前,大型设计一般推荐使用同步时序威廉希尔官方网站

。同步时序威廉希尔官方网站

基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2017-11-25 01:43:01 1411

1411 布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking资源,适合对FPGA设计有时序要求,却还没有足够了解的朋友。

2018-03-21 14:48:00 4672

4672

有些FPGA学习者,看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时钟管理单元。 1、DCM概述 DCM内部是DLL(Delay Lock Loop结构

2018-05-25 15:43:53 7884

7884

FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 1588

1588 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

本文档的主要内容详细介绍的是spartan-6 FPGA的时钟资源的用户指南资料免费下载。

2019-02-15 16:39:07 27

27 管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

2019-06-28 14:34:07 3703

3703 本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 14:49:00 24

24 区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。

FPGA时钟资源主要有三大类:时钟管理模、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA

2020-12-09 14:49:03 20

20 本文档的主要内容详细介绍的是FPGA的RAM存储资源详细资料说明包括了:1、 FPGA存储资源简介,2、 不同厂家的 Block RAM 布局,3、 块 RAM 和分布式 RAM 资源,4、 Xilinx Block RAM 架构及应用

2020-12-09 15:31:00 10

10 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达®-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-09 15:31:13 9

9 FPGA时钟资源主要有三大类 时钟管理模、时钟 IO 、时钟布线资源。

2020-12-09 18:14:00 13

13 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 本章介绍了高云半导体FPGA 产品的时钟资源,包括专用的时钟输入、缓冲区和布线资源。时钟的基础设施提供了一系列低电容、低偏移互连线,非常适合承载高频信号,最大限度地减少时钟偏差和提高性能,可应用于所有的时钟信号。

2020-12-10 14:20:13 9

9 本文档的主要内容详细介绍的是FPGA硬件基础之理解FPGA时钟资源的工程文件免费下载。

2020-12-10 14:20:11 6

6 本文档的主要内容详细介绍的是FPGA硬件基础之FPGA时钟资源的工程文件免费下载。

2020-12-10 15:00:29 15

15 xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

2020-12-29 16:59:33 12

12 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 SRL(移位寄存器)资源,在FPGA中都有,不过是叫不同的名字。Xilinx FPGA内部的LUT有个特殊功能,就是可以配置成可变长度SRL。

2020-12-31 16:45:35 8

8 引言:本文我们介绍区域时钟资源。区域时钟网络是独立于全局时钟的时钟网络。不像全局时钟,一个区域时钟信号(BUFR)的跨度被限制在一个时钟区域,一个I/O时钟信号驱动一个单一的Bank。这些网络对于

2021-03-22 09:47:30 4631

4631

引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们

2021-03-22 10:09:58 11527

11527

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 晶振是数字威廉希尔官方网站

设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。

2021-04-07 12:00:44 3914

3914

AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

1481 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 电子发烧友网站提供《Logos系列FPGA时钟资源(Clock)用户指南.pdf》资料免费下载

2022-09-26 10:15:21 1

1 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-04-07 09:42:57 594

594 如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量

2023-05-23 15:46:24 481

481

Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

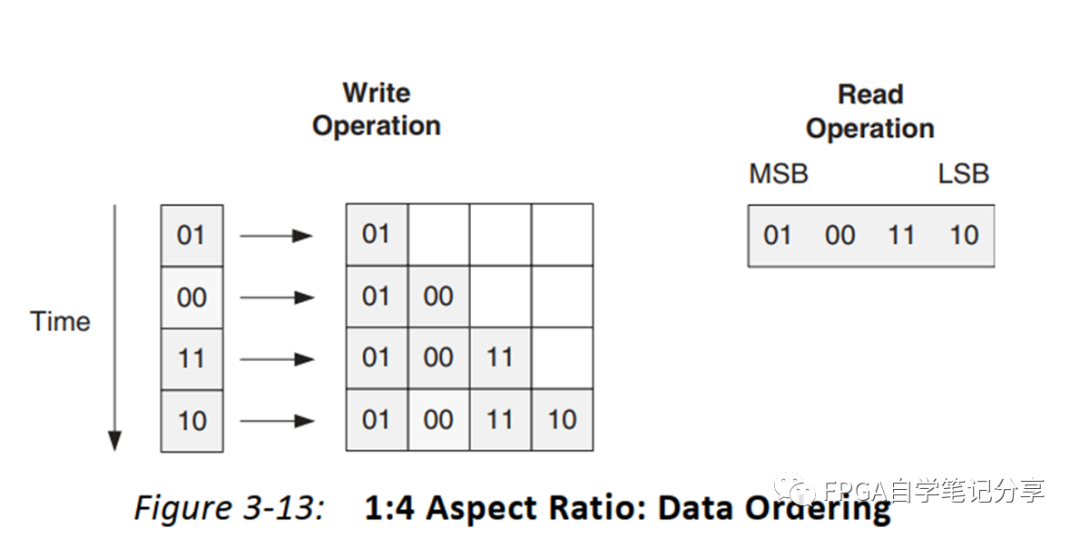

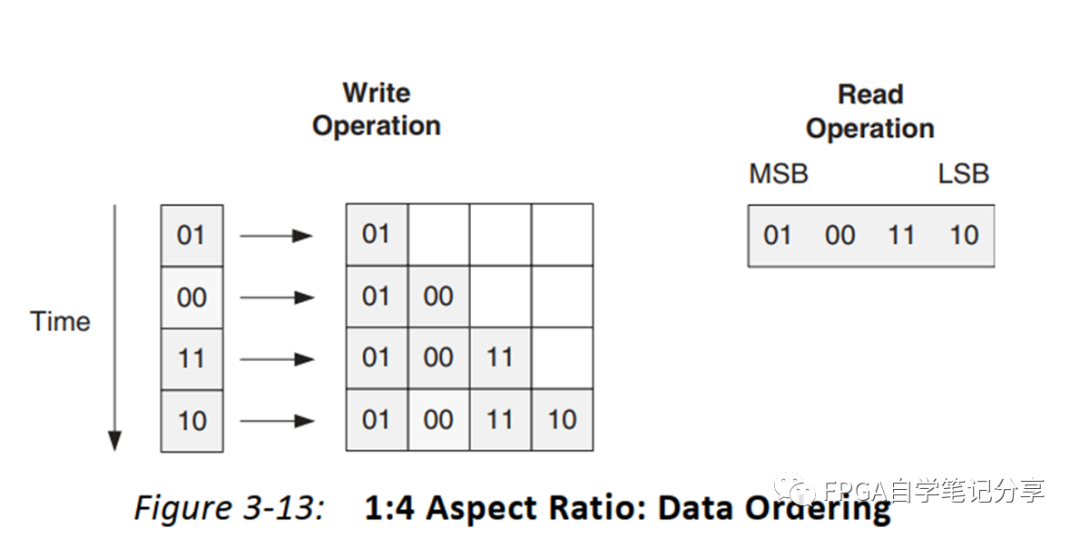

530 上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

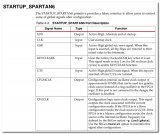

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的FPGA设计中或多或少都会用到。

2023-10-30 11:47:55 523

523

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论