在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 13866

13866

,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等威廉希尔官方网站

。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等威廉希尔官方网站

。对于GTX的发送端来说,结构如图

2020-11-20 11:27:39 5566

5566

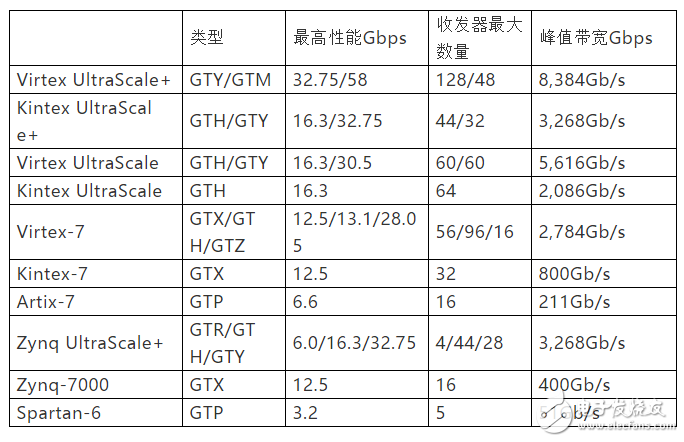

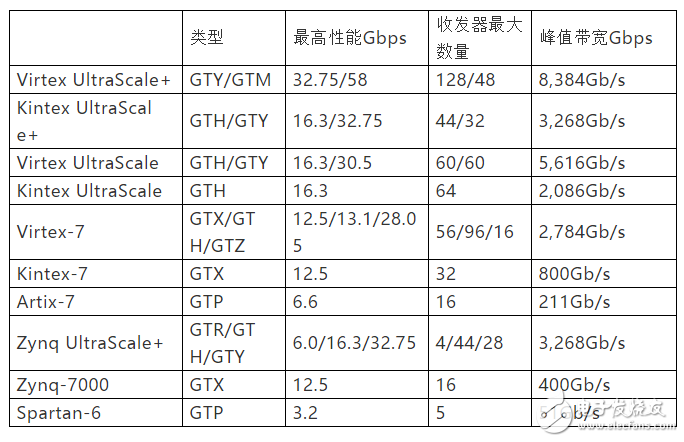

最大的收发器数量。 图1 Xilinx的7系列FPGA随着集成度的提高,其高速串行收发器不再独占一个单独的参考时钟,而是以Quad来对串行高速收发器进行分组,四个串行高速收发器和一个COMMOM(QPLL)组成一个Quad,每一个串行高速收发器称为一个Channel,以XC7K325T为例,GTX在F

2020-11-20 12:08:15 17712

17712

本文介绍Xilinx GT的一些概念,对GT没有概念但是有时间的童鞋推荐先看一下此文(Xilinx 7系列FPGA 高速收发器GTX/GTH的一些基本概念),补充一些基础概念。 随着高速数据传输

2020-12-15 15:54:09 8902

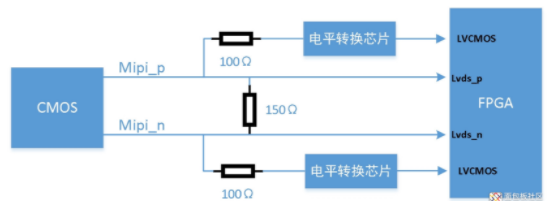

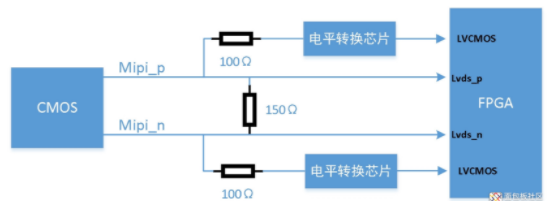

8902 作者:Hello,Panda 这次分享一个在Xilinx FPGA实现MIPI DPHY接口的案例(包括CIS协议层)。截止目前为止,Xilinx仅在Ultrascale+及其以上版本的FPGA

2021-01-28 14:11:41 11921

11921

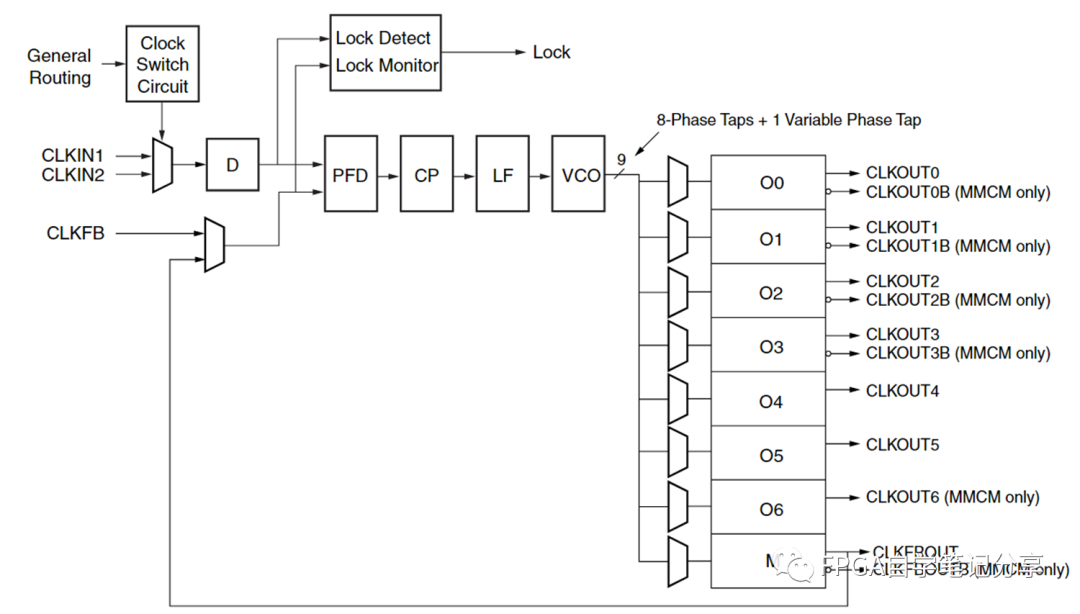

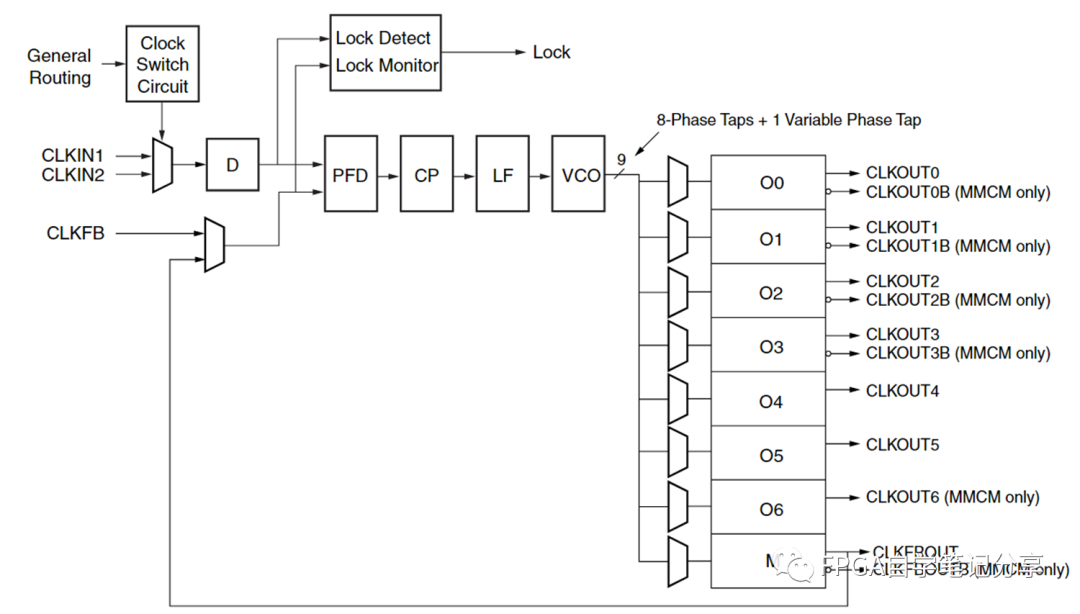

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 FPGA收发器GTX/GTH参考时钟接口提供两种连接方式:LVDS(如图1所示)和LVPECL(如图2所示)。我们在选择晶振时,至少要支持其中一种接口输出电平标准。图2所示的电阻值为一般推荐值,实际

2022-08-09 12:28:24 1703

1703 Xilinx FPGA的组成部分 本文是以Xilinx Kintex UltraScale+ 系列为参考所写,其他系列有所不同,可以参考相应的user guide文档。 Xilinx家的FPGA有这

2022-12-27 15:54:52 1788

1788 锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

2023-06-12 17:42:03 2883

2883

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序威廉希尔官方网站

。同步时序威廉希尔官方网站

基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

基于Xilinx FPGA V6 XC6VHX255T芯片的高速万兆网络光纤switch 平台一、板卡概述 本系统基于最先进的FPGA技术,构建一个高速数据传输验证系统,采用XilinxFPGA

2014-06-05 10:31:27

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

GTX、GTH等具体是什么就不多介绍了,网上有很多。写这个的目的,就是当收到FPGA板卡后,要判断本板的高速串行总线是否能够应用,那就需要做基本的功能测试。我们可以用xilinx提供的ibert进行

2021-07-02 08:00:00

课程以实际项目为背景,详细介绍XILINX 7系列FPGA硬件设计,项目案例板卡标准呢PCIE卡,FPGA采用Xilinx的XC7A100T-2FGG676I系列FPGA,具有超微体积、低功耗的特点

2021-11-17 23:12:06

本本将从常见的XILINX FPGA和Altera 两家FPGA的电源供电作如下介绍:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

`Xilinx FPGA无痛入门,海量教程免费下载 无私的特权同学为您送上85个课时的文档教程,35个经典例程,百度网盘可以免费下载:http://pan.baidu.com/s/1jGjAhEm

2015-07-22 11:49:20

我正在研究一种我喜欢Xilinx EVB KC705的设计。我尝试使用LPC FMC连接。 LPC中的GTX处于四通道117,而与LPC连接的ref时钟是四通道116 ref clock 1

2019-04-04 19:14:55

,这没有意义。在Xilinx的Aurora示例设计中,Xdc文件不限制GTX的引脚位置,但在综合和实现之后,反射时钟在右引脚中分配没有问题。所以我很困惑为什么我的设计无法正常工作。我想知道之前

2019-03-01 09:18:11

您好,我正在使用Plan Ahead 14.7和Virtex6 xc6vlx240tff1759-2目标FPGA。我的设备中有一个PCIe内核,它使用了FPGA中可用的24个GTX通道。我有5个通信

2020-06-17 07:46:51

你好,xilinx工程师2位文件可以一起下载到FPGA吗?这样做的目的是使用FMC板上的GTX。我希望将KC705的晶振时钟映射为FMC子板的refclk。所以我有2位文件:一个是IBERT,另一个

2019-04-10 10:44:04

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

我使用的是Xilinx的V5 FXT70T的开发板,用ISE生成的GTX,使用光纤模块实现在自发自收,但是在光纤模块(SFP)没有连接的情况下利用chipscope可以观察到有一路输出(与输入一致

2014-01-26 17:12:15

利用 IBERT 进行 GTX 信号眼图测试8.5.4.1 概述Vivado中提供了1种IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT我们可...

2021-07-20 07:28:23

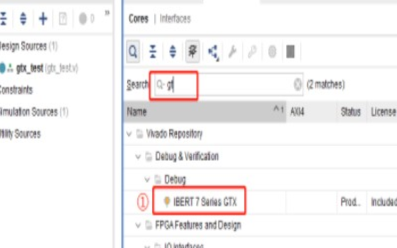

一、概述

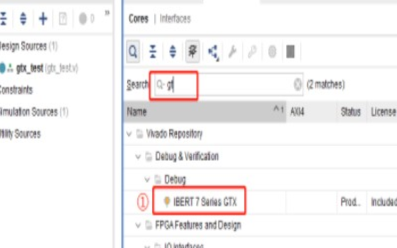

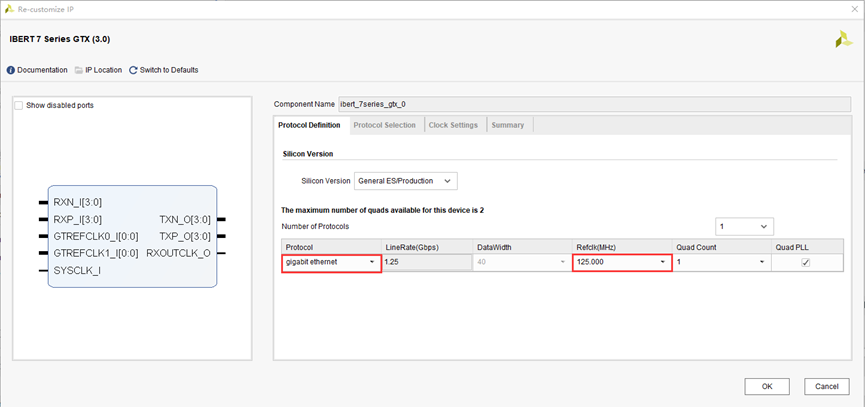

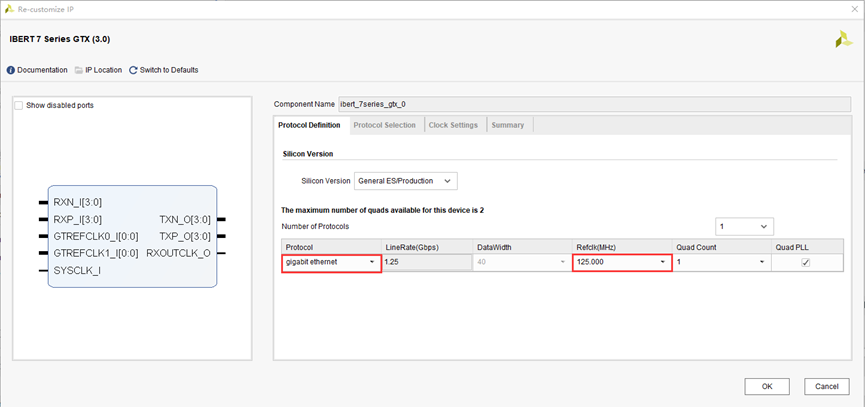

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问

2023-06-21 11:23:12

Xilinx FPGA上的JESD204B发送器和接收器框图。发送器/接收器通道实现加扰和链路层;8B/10B编码器/解码器和物理层在GTP/GTX/GTHGbit 收发器中实现。图4. 使用Xilinx

2018-10-16 06:02:44

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纤卡1. 板卡概述 板卡主芯片采用Xilinx公司的XC7K325T-2FFG900 FPGA

2015-01-28 15:48:55

你好,我在两个通过串行背板连接的Virtex 6 FPGA中实现了一个简单的4通道Aurora 8b / 10b内核。每个磁贴的专用GTX时钟是固定的 - 在FPGA0上为312.5Mhz,在

2020-06-18 10:21:39

你好!我试图在xc7k355t FPGA中实例化20个GTX收发器。所有20 GTX的核心配置都相同。在实施阶段发生以下错误:[放置30-640]放置检查:此设计需要比目标设备中更多

2020-08-20 13:39:54

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP产品介绍使用Xilinx的FPGA、SoC和ACAP进行设计和开发

2021-01-22 06:38:47

大家好 我正在尝试在FPGA V6之间建立通信链接。我正在关注“LogiCORE IP Virtex-6FPGA GTX收发器向导v1.9”文档。在测试示例中使用PCIeconnectors但我想

2020-05-19 07:35:21

本人从事FPGA研发工作多年,具有丰富的FPGA开发经验,,现寻这方面的兼职,可通过QQ:1196914075详谈;自我简单介绍:1. 对于xilinx和altera的FPGA芯片都比较了解;2.

2016-07-02 15:31:38

本帖最后由 scratdqy 于 2015-8-17 11:06 编辑

向各位大神求助GTX问题!!用xilinx的Vivado中的7 Series FPGAs Transceivers

2015-07-28 18:54:12

已经检查过,我有正确的引脚从pcie插槽中点击100M refclk。我的问题 - 1)用于FPGA的xilinx gtx phy是否支持SSC时钟?2)如果我在主机端启用或取消了SSC时钟,那么我

2019-04-01 13:22:15

XILINX应用程序,7系列FPGA收发器向导(2.5版)。核心配置如下: - 协议:XAUI - TX / RX线路速率= 3.125Gbps - TX / RX参考时钟= 125MHz

2020-07-19 09:01:44

生成了一个TX唯一的Aurora 8b10b内核(GTP),为Virtex7生成了一个仅限RX的Aurora 8b10b内核(GTX)。我的参考时钟是125MHz,而我的DRP / INIT时钟都是

2020-07-31 11:27:52

亲关于如何使用GTX生成PIPE接口PCIE PHY的以下主题,有没有人有答案?https://forums.xilinx.com/t5/7-Series-FPGA

2020-05-04 09:05:44

大家好,我使用IP CORE向导生成了两个GTX收发器。GTX0的线速为3.0 Gbps,参考时钟为375.0 MHz。GTX1的线速为1.5 Gbps,参考时钟为375.0 Mhz,尽管我也试过

2020-06-19 09:03:42

Virtex-6 FPGA GTX收发 User Guide:This document shows how to use the GTX transceivers in Virtex®

2009-12-31 17:05:28 25

25 十分钟学会Xilinx FPGA 设计

Xilinx FPGA设计基础系统地介绍了Xilinx公司FPGA的结构特点和相关开发软件的使用方法,详细描述了VHDL语言的语法和设计方法,并深入讨

2010-03-15 15:09:08 177

177 本书系统地论述了Xilinx FPGA开发方法、开发工具、实际案例及开发技巧,内容涵盖Xilinx器件概述、Verilog HDL开发基础与进阶、Xilinx FPGA威廉希尔官方网站

原理与系统设计

2012-07-31 16:20:42 11268

11268

本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 如果您希望进一步了解本公司 FPGA 如何在丰富多样的应用中获得用武之地,建议查阅下列手册。 XAPP1065:Spartan-6 FPGA 扩频时钟生成 http :/ /www.xilinx.com/support/documentat ion/application_notes/xap

2012-08-14 17:24:13 95

95 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(二)——Xilinx FPAG开发环境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 45

45 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义

2017-02-08 05:31:40 2048

2048

谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

1315 bstract: This reference design enables a complete solution for powering Xilinx Virtex-6 FPGA GTX

2017-04-05 10:15:57 17

17 文档内容包含基于Xilinx FPGA的开发板代码及原路图,供网友参考。

2017-09-01 11:09:24 20

20 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。 图1.Xilinx FPGA全局时钟分配

2017-11-22 07:09:36 8891

8891

之前用serdes一直都是跑的比较低速的应用,3.125Gbps,按照官方文档一步一步来都没出过什么问题,这次想验证一下K7系列GTX最高线速8Gbps,看看xilinx的FPGA是不是如官方文档所说。

2018-03-26 14:40:00 10190

10190 GTx接收和发送方向均由PCS和PMA两部分组成,PCS提供丰富的物理编码层特性,如8b/10b编码等;PMA部分为模拟威廉希尔官方网站

,提供高性能的串行接口特性,如预加重与均衡。

2018-06-29 08:47:00 10526

10526

FPGA本身是有专门的时钟cell的,以xilinx FPGA为例,就是primitive库中的BUFG。

2018-12-22 15:33:59 1588

1588 Xilinx GTX(12.5 Gb / s)收发器与SFP +和10G背板一起运行。

2018-11-30 06:36:00 9807

9807 Xilinx FPGA是支持OpenStack的第一个(也是目前唯一的)FPGA。

该视频快速介绍了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展台上运行每个演示,并使用OpenStack进行配置和管理。

2018-11-23 06:14:00 3322

3322 本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

2021-05-02 22:10:00 5587

5587

引言:本文我们介绍GTX/GTH收发器时钟架构应用,该文内容对进行PCIe和XAUI开发的FPGA逻辑设计人员具有实际参考价值,具体介绍: PCIe参考时钟设计 XAUI参考时钟设计 1.PCIe

2021-03-29 14:53:47 5441

5441

晶振是数字威廉希尔官方网站

设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。

2021-04-07 12:00:44 3914

3914

AD5933 pmod Xilinx FPGA参考设计

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA参考设计

2021-04-22 13:35:23 11

11 AD5628 pmod Xilinx FPGA参考设计

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA参考设计

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA参考设计

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA参考设计

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA参考设计

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA参考设计

2021-05-24 10:29:20 17

17 引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述 GTX/GTH收发器时钟

2021-11-06 19:51:00 35

35 所以本文首先介绍Example Design,然后再替换成我们自己的收发测试模块,对比印证学习,差不多就能勉强把GTX给玩起来了。

2022-03-01 17:39:12 6288

6288

作为一名初学者,也曾被GTX一堆信号搞得头晕脑胀,在学习了各位大佬的文章后,结合自己的理解和实践,整理这一系列快速上手的GTX使用教程。

2022-03-01 17:33:18 2607

2607

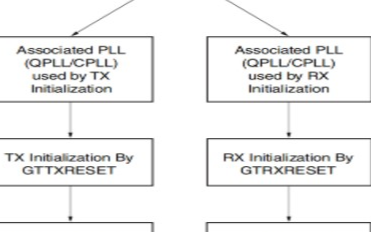

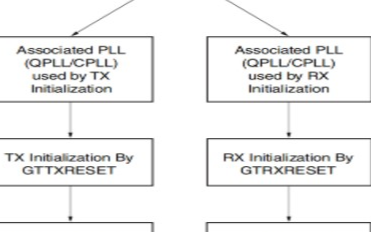

同时GTX复位也挺随意的,你想怎么复位都可以,支持整体复位,单个组件复位。我们也可以不复位,核不会因为我们没有进行软复位就不对核进行复位,在上电之后会自动进行一系列的复位,不随你的意志而转移。下面我们就来仔细研究研究GTX的复位吧!

2022-03-01 17:29:11 1462

1462

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH、GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

2022-03-01 17:17:20 3769

3769

Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 24

24 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

1481 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 本文介绍一个FPGA开源项目:基于IBERT的GTX数据传输测试。IBERT是指误码率测试,在Vivado软件中,IBERT 7 Series GTX IP核可用于对 Xilinx FPGA芯片

2023-08-31 11:45:30 1040

1040

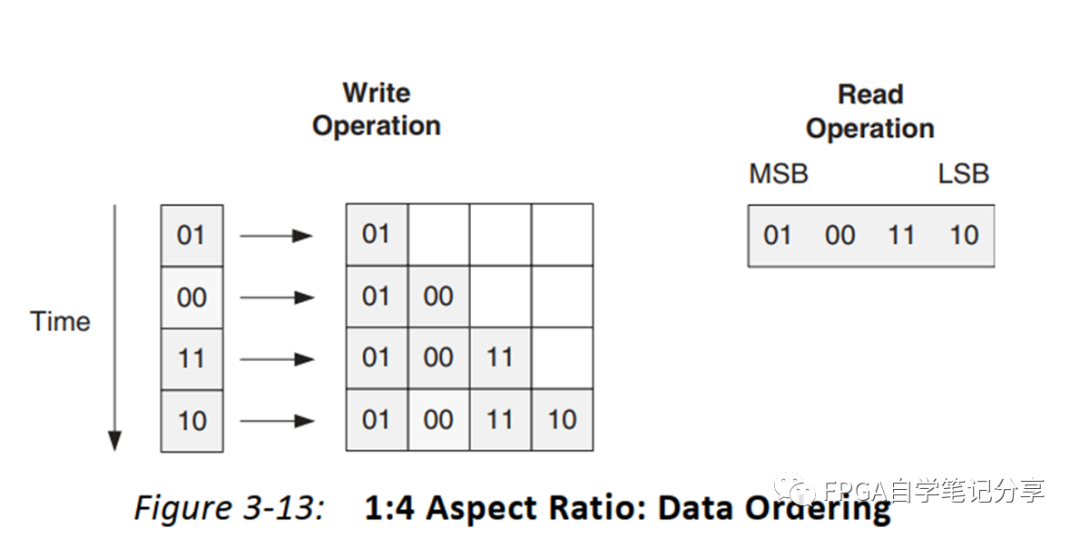

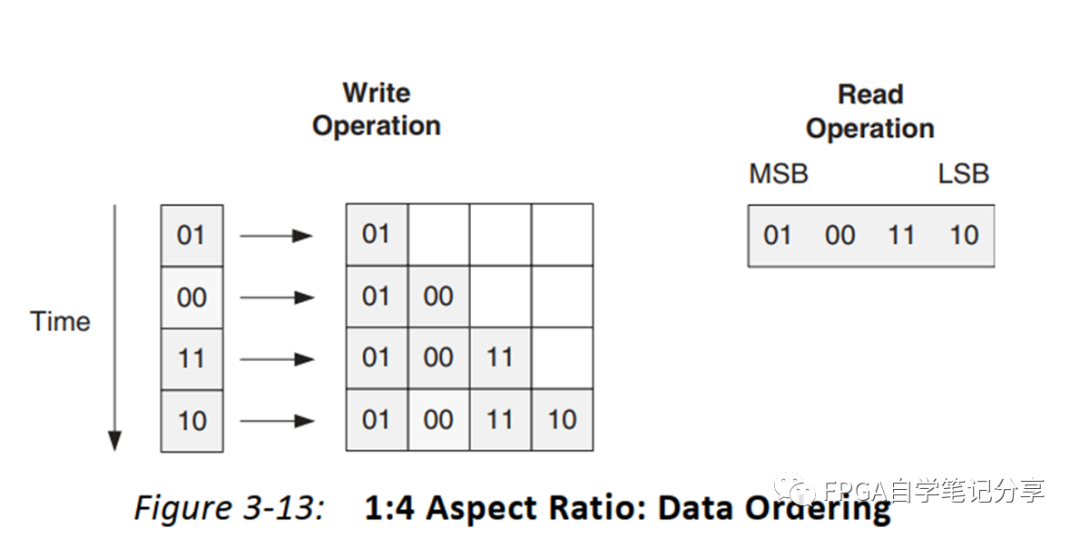

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子例化一个读数据位宽是写数据位宽两倍的FIFO,然后使用读时钟频率:写时钟频率=2:3,进行简单的FIFO跨时钟域操作。

2023-09-07 18:31:35 759

759

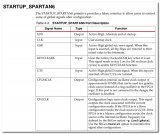

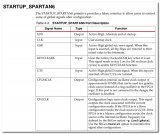

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论