Chiplet小芯片的时代机遇与趋势

描述

高性能计算(HPC)市场进入超预期的高速发展阶段,先进封装Advanced Packaging成为高性能运算芯片成功与否的关键技术。在第十四届中国集成威廉希尔官方网站 封测产业链创新发展高峰william hill官网 (CIPA 2022)“高峰william hill官网 ”上,矽品研发中心副总经理王愉博博士与产业探讨未来高性能计算的先进封装发展趋势。

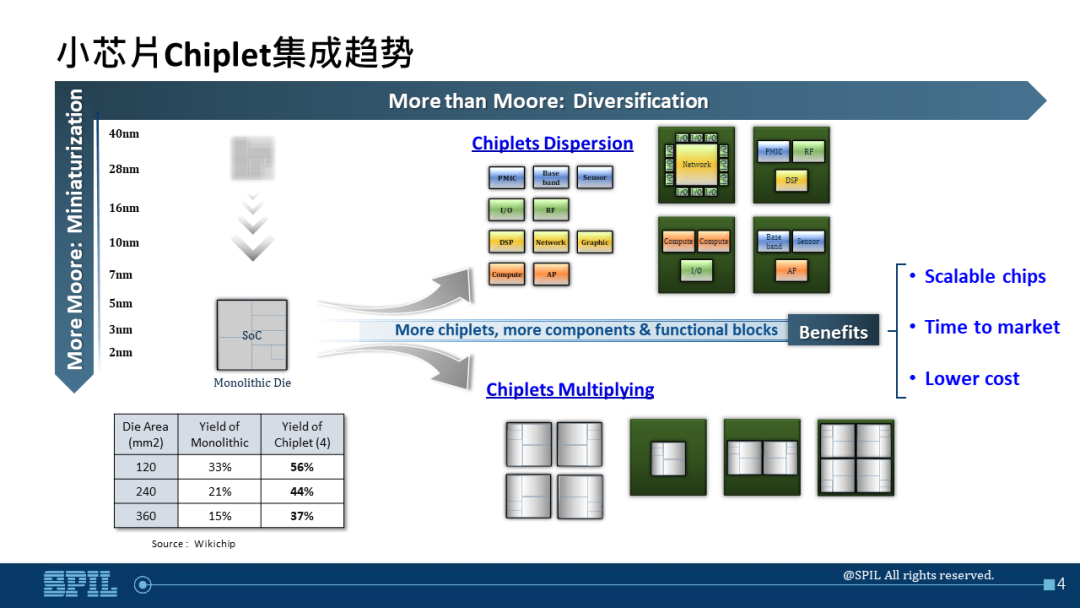

数据处理需求激增,AI算力对于高性能计算GPU的需求日趋增长,芯片上的晶体管数量也以十倍的成长率迅速增长。为了满足晶体管的数量,芯片的尺寸越来越大,但同时受限于radicle size而造成发展瓶颈。在摩尔定律趋缓,芯片的价格越来越高,良率因为芯片的尺寸增大而日益下降,小芯片Chiplet已成为先进封装发展的重要趋势。

王博士说明在最新一代Chiplet,依照不同的功能做区隔,使整体的速度效益达到明显的提升。或是利用封装体的形态把两个相同的芯片相互串联,发挥更高的效能,这种Chiplet表现方式可避免芯片因尺寸太大而造成晶圆厂制作的良率损失。无论Foundry或OSAT,都可以运用多种封装相结合的方式整合,包含2.5D/3D IC封装,以及FO-EB及FO-MCM封装等,王博士详细分析封装形态如何把Chiplet运用在未来高性能运算。

UCLe产业联盟

由日月光、AMD、Arm、Google Cloud、Intel、Meta、微软(Microsoft)、高通(Qualcomm)、三星(Samsung)和台积电(TSMC)等半导体业者共同组成UCIe(Universal Chiplet Interconnect Express)产业联盟持续推动芯片互连(die-to-die interconnect)技术标准化和促进开放式Chiplet生态系统,目前已有超过40家公司加入联盟,透过UCIe制定协定标准将可有效提高Chiplet生态系统整体效率,降低开发时间和成本。

日月光在封装和互连平台技术的专业知识,有助于确保UCIe提出的标准切实可行,并且在封装制造具有商业可行性和成本效益。

审核编辑:汤梓红

-

PCB行业在互联网时代的挑战和机遇2016-11-07 0

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 0

-

工业互联网平台的发展趋势和机遇2019-05-07 3130

-

Chiplet悄然兴起,面临的机遇与挑战2019-06-11 13304

-

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet2021-01-04 57953

-

芯原股份:正积极推进对Chiplet的布局2021-01-08 2878

-

半导体芯片先进封装——CHIPLET2022-10-06 24900

-

如何跑步进入Chiplet时代?2022-12-02 396

-

Chiplet是新蓝海,是国产设计大机遇2023-01-06 822

-

Chiplet和异构集成时代芯片测试的挑战与机遇2023-07-12 1915

-

Chiplet关键技术与挑战2023-07-17 1252

-

chiplet和cpo有什么区别?2023-08-25 2097

-

chiplet和cowos的关系2023-08-25 3488

-

Chiplet技术的发展现状和趋势2023-08-28 1319

-

Chiplet成大芯片设计主流方式,开启IP复用新模式2024-01-12 2116

全部0条评论

快来发表一下你的评论吧 !