时序分析命令set_clock_sense编程案例

编程语言及工具

描述

首先,什么是unate?Combinational Timing Arc 的Sense有三种,分别是

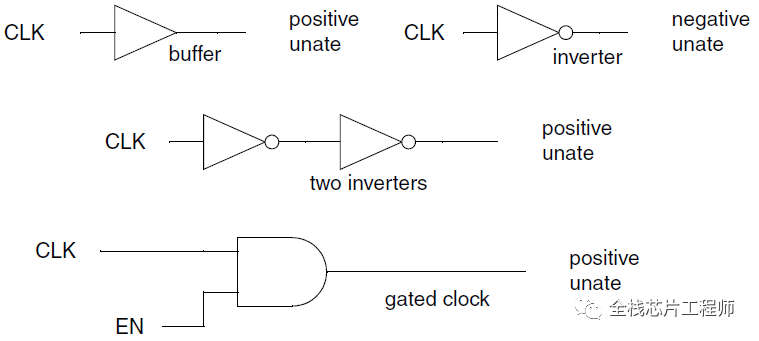

positive unate/non-inverting

rising edge的clock source引起register clock pin的rising edge。

negative unate/inverting

rising edge的clock source引起register clock pin的falling edge。

non-unate

non-unate的情况:

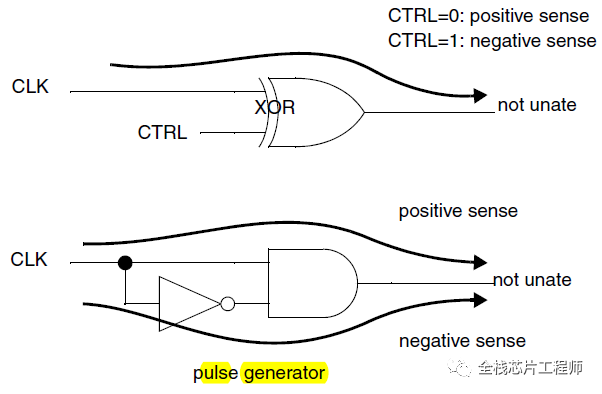

异或逻辑中:clock unate的极性跟另一个input有关,是一个non-unate的信号。

pulse generator的输出不是unate。

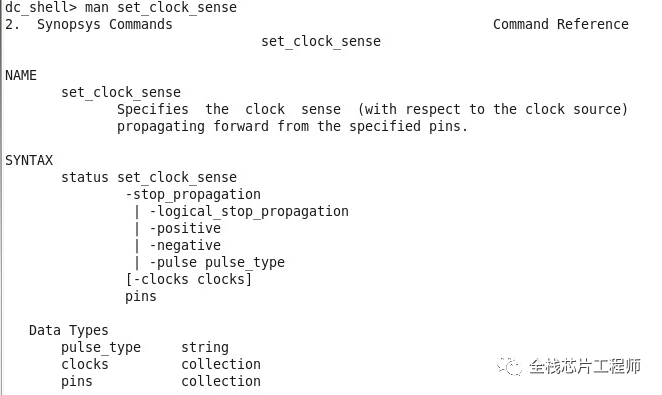

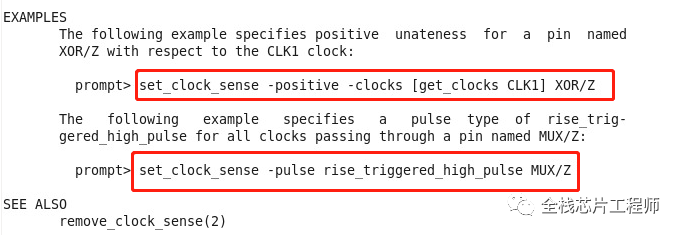

set_clock_sense

问:在non-unate的clock network中,怎么分析时钟?

答:可以通过命令set_clock_sense来设置需要分析的clock的sense。

比如:

set_clock_sense -stop_propagation:

表示时钟physically上不会进行propagate。

set_clock_sense -logical_stop_propagation:

表示clock可能会作为data继续进行propagate,但是不会作为clock进行分析。举个例子:

set_clock_sense -logical_stop_propagation -clocks CLK U3/A

注意:

The -logical_stop_propagation option is mutually exclusive with

the -positive, -negative, -stop_propagation, and -pulse options.

You must specify one of these options.

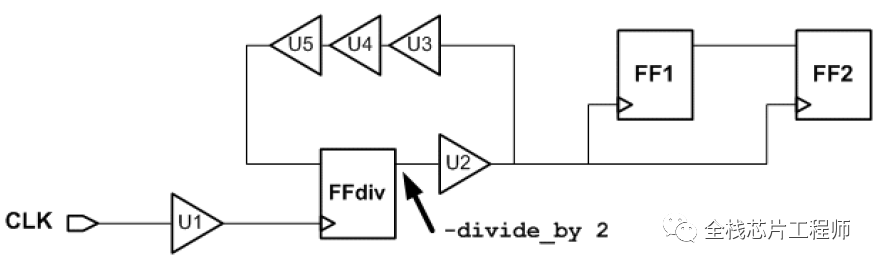

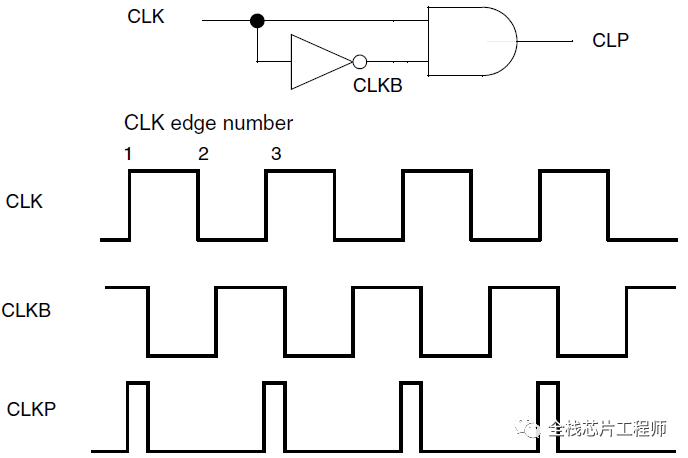

pulse clock

可以是pulse generator cell/create_generated_clock/set_clock_sense

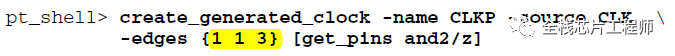

1、用create_generated_clock

-edge {1 1 3}表示第一个上升沿和下降沿都是1时刻,3时刻是下一个上升沿。

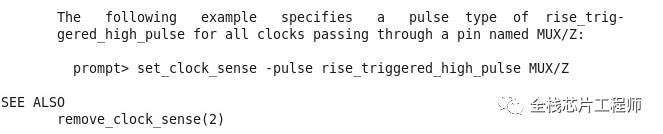

2、用set_clock_sense:

set_clock_sense -pulse rise_triggered_high_pulse and2/z

参考如下:

编辑:黄飞

-

DC学习(时序分析和命令)2021-11-09 204

-

时序约束 专版2013-05-16 0

-

时序约束之时钟组约束2018-09-21 0

-

时序约束之时序例外约束2018-09-21 0

-

tcl命令用于时序分析如何检查输入或输出的时间?2019-03-11 0

-

静态时序分析2023-04-20 0

-

使用时钟PLL的源同步系统时序分析2010-10-05 874

-

set_max_delay被覆盖的解决办法2020-09-07 9931

-

详细解析vivado约束时序路径分析问题2020-11-29 8717

-

这个set命令的这些功能你了解吗2022-11-25 467

-

Xilinx跨时钟域时序约束2022-12-12 2537

-

clock gate时序分析概念介绍2023-07-03 3037

-

时序分析基本概念介绍<Latency>2023-07-04 2448

-

时序分析基本概念介绍<generate clock>2023-07-06 2291

-

时序分析基本概念介绍<Virtual Clock>2023-07-07 1483

全部0条评论

快来发表一下你的评论吧 !