易于实现且全面的3D堆叠裸片器件测试方法

描述

当裸片尺寸无法继续扩大时,开发者开始考虑投入对 3D 堆叠裸片方法的研究。考虑用于 3D 封装的高端器件已经将当前的可测试性设计 (DFT) 解决方案推向了极限。

如果设计人员已经几乎无法平衡工具运行时间、片上面积需求、向量数量和测试时间,他们如何在 3D 器件上去实现 DFT 呢?

3D IC 测试简介

几种设计趋势相结合,显著增加了 IC 测试生成所需的计算资源。首先是设计规模和复杂性的增长。与此同时,可用于 2D 封装测试访问的 I/O 更少了。

这些因素也导致测试覆盖率、良率、功耗和互连测试要求承受巨大压力。3D 裸片堆叠和封装是改进系统级封装技术的重要一步。3D 裸片堆叠有多种方法,但它们的共同目标是使用尺寸更小且良率高的裸片进行垂直堆叠。这种策略缓解了大型 2D 或 2.5D 器件的许多测试挑战。

在对 3D 堆叠中组装的裸片进行晶圆探针测试时,建议采用高质量的已知良好裸片 (KGD) 测试。KGD 测试通常包括除裸片间互连测试以外的所有封装测试。

然后,封装测试需要进行裸片间 (D2D) 互连测试并重新运行 KGD 测试,以确保封装和组装期间没有引入任何缺陷。每个级别的 3D 测试都需要进行故障诊断,包括完整的封装级堆叠层诊断。

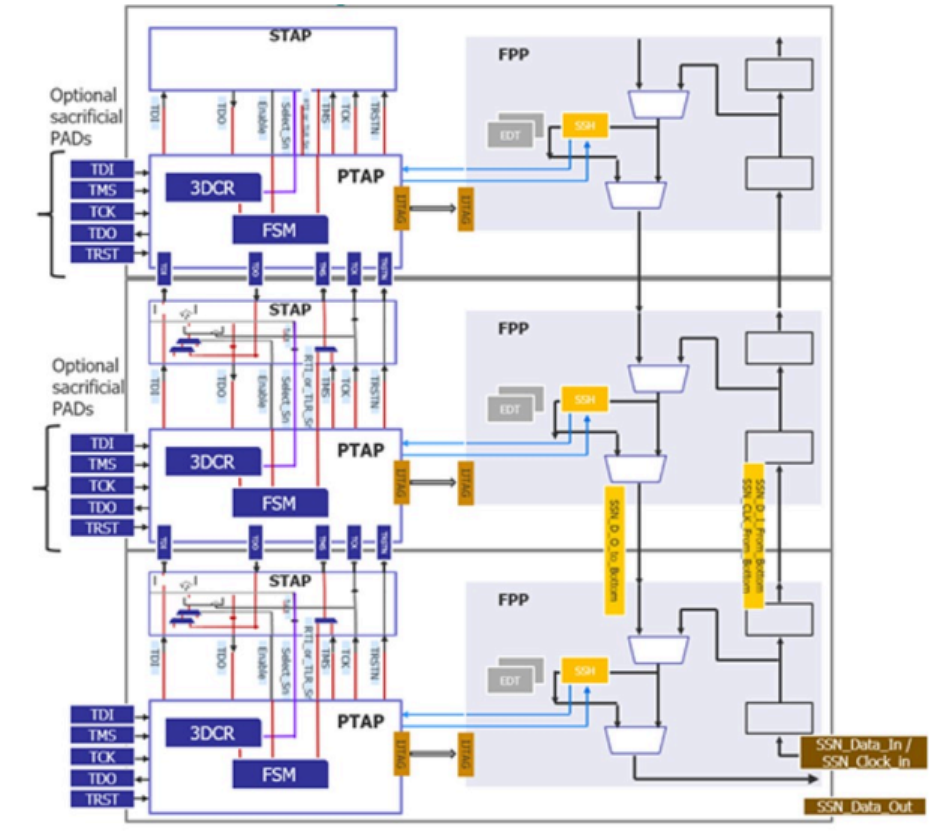

在本文中,我们详细介绍了一种灵活可扩展、易于实现且全面的 3D IC DFT 解决方案。

图 1:Tessent 3D DFT 解决方案概述

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

裸眼3D***领域开启新纪元2012-07-31 0

-

裸眼3D显示应用2022-11-07 0

-

解读裸眼3D技术2012-02-28 6854

-

裸眼3D详解2012-08-17 1252

-

裸眼3D:视觉盛宴何需眼镜2012-08-17 1089

-

最新裸眼3D技术揭秘2012-08-17 11130

-

裸眼3D立体显示技术详解2016-01-27 58002

-

裸眼3d技术的特征有哪些2017-11-10 5716

-

京东方推出裸眼3D产品 可实时转换2D和3D画面2018-01-11 2928

-

裸眼3d电视机多少钱2018-03-19 11854

-

国际大厂们之间的“3D堆叠大战”2020-01-28 3423

-

2.5 D和3D IC如何进行单个裸片测试2022-10-12 1291

-

2D/3D 热分析和三裸片堆叠设计实现2023-09-16 951

-

英伦科技裸眼3D平板有哪些方面的优势?2024-06-07 403

-

裸眼3D笔记本电脑——先进的光场裸眼3D技术2024-07-16 527

全部0条评论

快来发表一下你的评论吧 !