基于GaN的高效率1.6kW CrM图腾柱PFC参考设计TIDA-00961 FAQ

描述

高频临界模式 (CrM) 图腾柱功率因数校正 (PFC) 是一种使用 GaN 设计高密度功率解决方案的简便方法。TIDA-00961 参考设计使用 TI 的 600V GaN 功率级 LMG3410 和 TI 的 Piccolo™ F280049 控制器。功率级尺寸 65 x 40 x 40mm,功率密度大于 250W/inch3;在 230V 交流输入和满载情况下效率可达 98.7%;功率因数>0.99,输入电流THD小。此设计适用于多种空间有限的应用,如服务器、电信和工业电源等应用。同时硬件设计符合传导发射、浪涌和 EFT 要求,可帮助工程师实现 80+ Titanium 规格。

TIDA-00961为工业界提供了一套前沿的解决方案,本 FAQ 旨在解决大量工程师在学习本参考设计过程中遇到的常见问题。

1. TIDA-00961的控制程序获取途径?

TIDA-00961所有的资料(包括原理图和程序)已开放,可在DigitalPower SDK中获取,程序文件位置:

C:tic2000C2000Ware_DigitalPower_SDK_1_01_00_00solutionstida_00961f28004xpfc2philtrmttpl

DigitalPower SDK可通过官网下载安装,其中还包含所有芯片的参考例程、最新的参考设计源代码、powerSUITE设计工具等。(下载链接)

2. 参考方案的设计功率为1.6kW, 如果想应用于更高的功率场合,有什么建议?

TIDA-00961满载设计功率为1.6kW(high line 230V)、1.2kW( low line 110V),主要是考虑到GaN 半桥功率板的设计功率,同时由于CrM控制模式下峰值电流为平均电流的两倍,因此建议在CrM模式下,一个GaN 半桥功率板对应的设计功率为1kW,所以,本参考设计实际可工作在2kW的满载功率(已通过实际测试)。若想将本方案应用在更高功率的场合,例如3kW,可参考以下3种实现方式:

1) 采用多管并联方式,例如通过双管并联将功率回路上的GaN引入的导通损耗降为原来的一半,从而可在不变拓扑和控制方式基础上提高功率;

2) 增加交错并联的相数,例如,升级原两相交错拓扑为三相交错并联拓扑,同时在控制上,将其他两相的移相角度由1800改为1200和2400。

3) 目前方案采用的GaN是LMG3410(Rdson=70mΩ),下一代GaN Polaris 即将推出(预计2019年上半年,目前可联系TI 销售团队进行样片申请),其拥有更低的导通电阻(Rdson=50mΩ),单管能承担更大的功率,且与LMG3410管脚兼容,硬件拓扑和软件控制皆无需变动。因此,直接采用Polaris是提高系统功率的最简便方式。

3. 同样使用 GaN实现高效率的PFC参考设计PMP20873是基于CCM模式的,方案采用CrM控制是出于什么考虑?

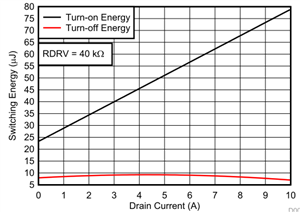

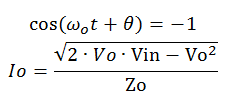

TI GaN LMG3410 避免了Si MOSFET的反向恢复问题,因而可用于实现图腾柱拓扑的CCM工作模式,可见参考设计PMP26873,但注意到该设计的开关频率为100kHz,如果想通过进一步提高开关频率来提升功率密度,CCM的工作模式将会遇到瓶颈。虽然GaN的开关损耗表现相比Si MOSFET 有优势,但具体来看(见图 1),在硬开关时其开通损耗比关断损耗高,一旦开关频率提高到几百或MHz,开关损耗的比重将大大提高。因此,通过采用CrM模式实现零电压开通(ZVS)为更高的开关频率和更高的功率密度提供了可能。

图 1 硬开关时GaN对应的开通损耗和关断损耗

4. 参考设计采用两相交错的拓扑的原因是什么?

1) 通过两相交错并联,系统的功率等级可以提升至原来的两倍

2) 相比于两相交错并联,同等功率的单相威廉希尔官方网站 在CRM模式下,电流有效值大,由于开关周期内的峰值电流为平均电流的两倍,因此电流波动大,必然会增加线路和器件的导通损耗。通过交错并联使得各相输入电流或各相输出电流的纹波相互抵消,大大改善了THD表现,对输入差模滤波器以及输出电容的大小要求降低了,同时纹波的减小也使得输入滤波器以及输出电容上的损耗减小。

5. 如何理解Phase shedding?

Phase shedding用于提高系统效率,当负载变小时(小于设定的电流阈值),使能Phase shedding关闭第二相,从而提高系统在轻载时的效率。值得注意的是,需控制Phase shedding使能的时刻发生在电压过零点的瞬间,此时环路中的能量最小,从而避免由于Phase shedding导致的电流的过冲或振荡现场。

6. 在程序中,当负载变大要加入第二相时,为什么要有gv_out = gv_out*(0.6)的处理?

0.6的系数处理上为了防止潜在的电压过冲问题。在轻载情况下只有一相工作,此时若负载增大至超过设定的阈值时,此时需要立即使能第二相,若此时第二相采用的占空比与第一相的前一时刻占空比一致,相当于产生两倍于之前的能量输出,由于此时负载只是小幅增大,因此将导致很大的输出电压过冲。因此,理论上公式中的系数应采用0.5,但考虑到实际负载仍在变大,采用0.6的系数较为合适。

7. 参考设计的PWM 频率最高达1.2MHz,主要靠什么保证?

3) 宽禁带半导体器件GaN使得MHz的开关频率成为可能,TI的 LMG3410内置驱动,最大程度上减小了环路寄生电感的影响,在高频开关动作下依然能保持很低的损耗。

4) 在如此高频的开关下实现系统的精准高效控制,依赖于TI的新一代C2000 MCU TMS320F28004x的优异计算能力。100MHz的主频,除了浮点运算单元(FPU),增加了三角函数运算单元(TMU),通过硬件加速,大大加快了除法、正余弦和均方根等复杂运算的速度,从而保证了在高频中断内环路控制、ZVS控制等算法的实现。同时,F28004x的Type 4 ePWM可实现占空比、周期、死区时间的高精度控制,在高频开关下保持控制的精确性和准确度。

8. 高频工作下两相交错的控制如何保证一致而不出错?

本参考设计采用新一代的C2000 MCU TMS320F28004x,最新的Type 4 ePWM引入了一次加载和全局加载功能,保证了占空比、相位等寄存器基于同一设定事件同时更新,可避免潜在的在多相控制应用中的相位控制出错问题。

9. 开关频率达到MHz,在EMI上是否有挑战?

相比传统的CCM模式下PFC应用场合,本参考设计的开关频率最高达到MHz,同时采用两相交错并联控制,理论上能大大减小差模滤波器的体积,但也注意到CrM模式是变频控制,对滤波器设计的要求会相应提高;另一方面,GaN LMG3410可通过调整外部电阻大小灵活调整dv/dt,有助于改善EMI问题。目前,本参考设计的开发板正计划交付EMI测试,我们会把测试结果尽快更新出来。

10. 程序中的controlISR 中断频率为50kHz,包含了大量运算,该中断运行后剩余多少时间?

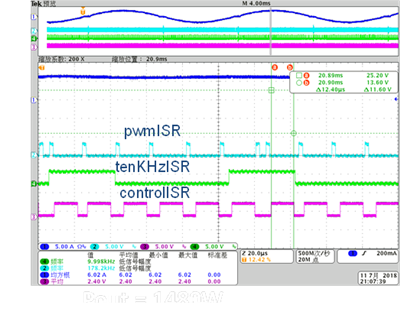

controlISR 中断主要用于电流环控制、锁相环的计算等,通过实际的测试获得该中断所需运行时间为12.4µs,CPU 带宽占用约为60%,见图 2。此外,控制程序还包含其他两个中断,分别是:频率为10kHz的tenKHzISR , 用于电压环和phase shedding处理,所需运行时间为20.8 µs;频率为PWM 频率的1/3 的pwmISR,用于ZVS 调整和移相同步控制,所需运行时间为2.04 µs。由此可知,得益于F28004x优异的计算能力,该控制系统的CPU 带宽占用率比较低,仍能为额外的用户功能提供足够的裕度。

图 2 系统中断运行所需时间

11. 原理图中没有OCP等保护威廉希尔官方网站 ,该保护功能怎么实现?

1) 本方案无需外部OCP威廉希尔官方网站 ,通过采样输入电流,直接利用F28004x片上的窗口比较器(CMPSS)同时实现对输入电流的正负半周的OCP,不需经过CPU的判断处理,通过硬件实现约60ns的快速保护能力。

2) 此外,TI GaN LMG3410内部集成了OCP、OTP等保护功能,若功率回路出现过流,LMG3410能够立刻关断实现保护功能。

12. 原理图中PFC的boost电感为15uH,怎么避免在输入电压过零点时刻的电流尖峰?

方案中的boost电感较小,即使很小的电压也会引起快速的电流变化,尤其在电压过零点时,易出现电流尖峰现象。因此,本设计在输入电压过零点时瞬间,由于采用软启动控制,通过判断输入电压的大小,利用状态机控制GaN和MOSFET的开关时序,消除了过零点的电流尖峰,进一步提升电流的THD。关于软启动的具体原理可参考TIDM-1007参考设计说明中的 2.4.4节

13. 一个开关周期内的功率管开通和关断时间如何决定?

本系统的控制模式基于恒导通时间模式,控制系统由输出电压外环和输入电流内环构成,开通时间Ton主要取决于电压环,同时引入电流内环做微调优化输入电流的THD。关断时间Toff根据伏秒平衡原理求得。

14. 硬件威廉希尔官方网站 中哪些是ZVS检测威廉希尔官方网站 的有效部分?

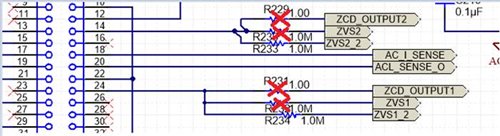

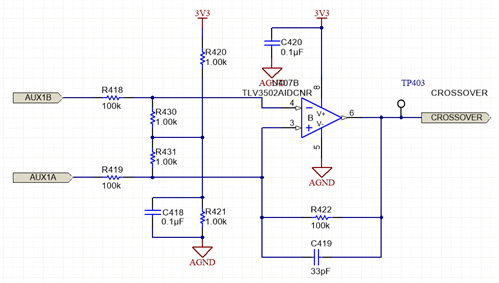

答:我们在设计的过程中曾采用了多种实现ZVS的方式,目前有效的ZVS检测信号为ZVS1_2和ZVS2_2。其中用于产生ZCD_OUTPUT1/2、ZVS1/2和CROSSOVER信号的威廉希尔官方网站 是冗余的,已经不再使用。

图 3 冗余威廉希尔官方网站

15. 参考设计中是如何实现ZVS的?

参考设计通过两种机制实现ZVS:调整开启主工作管前的死区时间和调整续流管的导通时间,具体如下:

1) 调整开启主工作管前的死区时间

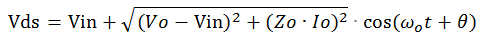

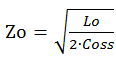

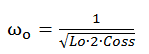

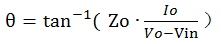

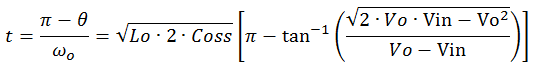

通过威廉希尔官方网站 分析可得,当续流管关闭,开启主工作管前,主工作管上的Vds电压满足:

其中,

当输入和输出电压满足Vin<0.5Vout时,在主开关管关断时,通过电感和开关管寄生电容的谐振,Vds可以到达0,从而可以自然实现零电压开通ZVS。当Vin>0.5Vout,Vds无法通过谐振到达0,若要实现全范围的ZVS,则需要加入额外的控制算法。具体思路为在电感电流下降到0之后,提供一段时间(死区时间)的负向电感电流Io,为谐振回路注入能量,使得Vds可以到达0。

在Vds降到0时,有

进一步求得死区时间,

另外,当Vin<0.5Vout时,对应的死区时间为

2) 调整续流管的导通时间toff_calc

通过外部ZVS检测威廉希尔官方网站 ,该威廉希尔官方网站 用于检测Vds的斜率(dv/dt),产生ZVS1_2作为F28004x片上的窗口比较器(CMPSS)的输入信号。如果主工作管开启时刻产生较大的ZVS1_2,则通过CMPSS判断出此时ZVS没有实现(zvs_lost = 1),因而需在下一个开关周期增加续流管的导通时间toff_calc;若判断此时实现了ZVS,则在下一个开关周期减小续流管的导通时间,避免引入过多的负向电流影响系统效率,因此,这是一种动态调整机制。此外,在程序计算toff_calc时,对于Vin>0.5Vout工况,toff_calc在伏秒平衡计算结果基础上,也加入一段与输入电压大小正相关的延时时间,具体可见acSine_diff的计算。

16. 主工作管关断到续流管开通的死区时间是固定的么?

该死区时间对应开关管的寄生电容和boost电感的谐振时间,在传统的模拟控制中,一般采用固定的死区时间设置,而在一个输入电压AC周期内,该谐振时间是变化的,因此,过长或过短的死区时间都不利于提高效率,同时易导致开关动作时机不合适引起的振荡问题。本设计采用自适应死区控制,每个开关周期内都采用死区时间 ,从而进一步提高系统效率。

17. 系统能在全范围内实现ZVS吗?

答:目前更新的程序中,可实现全范围ZVS控制的工况为:Vin有效值小于 210V。当

Vin有效值大于 210V时,目前没有根据ZVS检测调整续流管的导通时间(ZVS extension),当前代码用于V2版本硬件威廉希尔官方网站 ,未来会优化代码,使ZVS extension在V3版本威廉希尔官方网站 上可工作于210V以上。

18. 怎么理解SPLL_1PH_SOGI_FLL_run(&spll3,ac_vol_sensed),锁相环的用途是什么?

SPLL_1PH_SOGI_FLL_run作为C2000 官方库函数功能之一,可通过DigitalPower SDK进一步了解,具体用法和原理可参考文档《 Digital Power Library USER’S GUIDE》,文件位置C:tic2000C2000Ware_DigitalPower_SDK_1_01_00_00docs。

在本程序中,锁相环对输入电压进行频率和相位检测,目的在于:

1) 进行正负半周开状态切换的时刻判断;

2)在电压过零点时对开关信号进行软启动处理,使得过零点处的电流平缓过渡,避免电流毛刺的产生;

3)电压相位对应的正弦值用于计算电流环的电流给定值(ac_cur_ref_inst = ac_cur_ref*acSine ,ac_cur_ref为电压环的输出),用于电流环的准确跟踪;

19. 在程序中,控制电流环的语句gi_out=DCL_runPI_C1(&gi, SFRA_F_INJECT(ac_cur_ref_inst), ac_cur_sensed),其中SFRA_F_INJECT(ac_cur_ref_inst)怎么理解?

本控制程序内集成了Software Frequency Response Analyzer (SFRA)功能,工程师可直接利用本程序启用SFRA功能在线获得系统的环路带宽等参数,无需增加任何硬件设备。一旦使能SFRA功能,SFRA_F_INJECT(ac_cur_ref_inst)代表的信号为在ac_cur_ref_inst基础上叠加特定频率的小信号干扰量。值得注意的是,SFRA功能是服务于项目开发阶段的工具,一旦系统参数调试完毕,可去掉相应的SFRA内嵌代码,释放其占用的带宽,具体可见SFRA的具体使用说明。

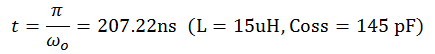

20. 为什么说明书给出的测试结果显示系统工作在Pout = 800W(Vin = 230V)附近时,THD值会跳变?

图 4 THD测试结果

由于该阶段会发生相切(phase shedding)到相加(2nd phase on)的变化,相加后每相所带的负载值变小为原单相运行时的一半。由于低负载时的THD要比高负载时差些,所以导致开启第二相时,THD的值会突然增加。

审核编辑:郭婷

-

图腾柱PFC就绪,你准备好了吗?2018-09-05 0

-

基于GaN的高效率CrM图腾柱PFC转换器包括BOM及层图2018-10-25 0

-

高频临界模式图腾柱PFC解决方案TIDA-00961 FAQ2019-03-07 0

-

1kW、80 Plus Titanium、GaN CCM 图腾柱无桥 PFC 和半桥 LLC 参考设计2020-06-22 0

-

开源咯~交错式 CCM 图腾柱无桥功率因数校正 (PFC) 设计方案2020-07-28 0

-

基于GaN的CrM模式的图腾柱无桥PFC参考方案的设计2022-01-20 0

-

基于 GaN 的交错式 CCM 图腾柱无桥 PFC 参考设计2022-04-12 0

-

图腾柱PFC介绍2022-11-17 0

-

使用C2000 MCU的双向高密度GaN CCM图腾柱PFC参考设计2023-01-17 0

-

基于GaN的高效率1.6kW CrM图腾柱PFC参考设计TIDA-00961 FAQ2021-11-10 1951

-

NCP1680图腾柱PFC CRM模式电感计算表2022-09-20 793

-

DSP控制 GAN图腾柱PFC LLC 1KW(含原理图和PCB和bom)2022-09-20 858

-

NCP1680 – CrM 图腾柱 PFC IC 技巧和窍门2022-11-15 606

-

CCM和CRM的图腾柱PFC哪个效率更高?2022-11-17 4249

-

高效氮化镓电源设计方案 GaN在基于图腾柱PFC的电源设计中实现高效率2023-08-01 2168

全部0条评论

快来发表一下你的评论吧 !