栅极驱动器以及SiC MOSFET栅极驱动

模拟技术

描述

碳化硅(SiC)MOSFET 的使用促使了多个应用的高效率电力输送,比如电动车快速充电、电源、可再生能源以及电网基础设施。虽然它们的表现比传统的硅(Si)MOSFET 和 IGBT 更为出色,但驱动方式却不尽相同,必须要在设计过程中进行缜密的思考。以下是一些 SiC 栅极驱动器的一些示例要求:

驱动供电电压包含开通的正压和关断的负压

共模瞬态抗扰度(CMTI)大于 100 kV/µs

最大工作绝缘电压可达 1700 V

驱动能力可达 10 A

传输延迟时间和频道不匹配时间小于 10 ns

主动米勒钳位

快速短路保护(SCP)(小于 1.8 µs)

** #1 **

对于 SiC MOSFET 的一般驱动考虑

鉴于这些要求,需要考虑几个栅极驱动器技术。磁耦合驱动器是一个相对成熟的技术,但是在磁场应用中也会成为一个令人关切的问题。电容耦合驱动器具备来自高电压应力和改进后对外部磁场抗扰度的出色保护,同时以最低的延迟提供非常迅捷的开关。但是,这项技术仍然容易受高电场应用问题的影响。作为更为传统的绝缘方式、光耦合非常有效并可提供出色的瞬变和噪音保护,但是由于曝光增加和 LED 特性,随着时间推进会逐渐减弱。

随着系统功率和频率增加,栅极驱动功率要求也会提高。设计人员应确保驱动器具备足够的驱动能力保证 MOSFET 完全导通。保持栅极驱动器内部 FET RDS(on) 处于低位以及更高的电流输送和更快的开关速度,但是总驱动平均功率要求取决于开关频率、总栅极电荷(以及任何其置于栅极上的电容)、栅极电压摆动以及并联 SiC MOSFET 的数量或 P =(Freq x Qg x Vgs(total) x N)。其中 P 是平均功率,Freq 是开关频率,Qg 是总栅极电荷,Vgs(total) 是总栅极电压摆动,N 是并联数量。

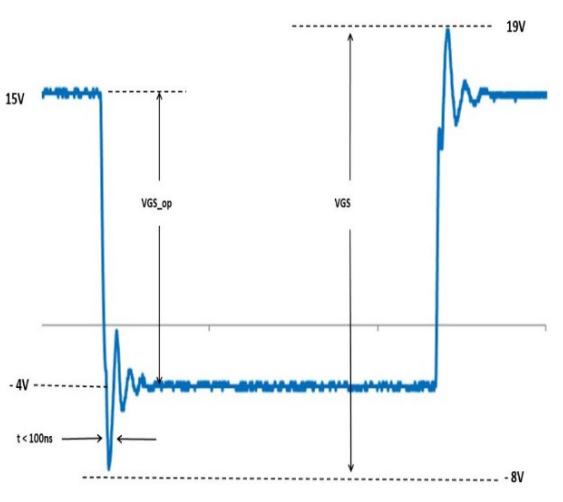

开关时往往存在振荡和过冲,正如图 1 当中所示的那样,所以需要特别关注器件的最大 VGS 额定值。对于开通/关断时的驱动电源电压选择,推荐(15 V, - 3 V)以确保安全运行和长期可靠性。驱动电压可以接受 ± 5% 的公差。对于带有相对紧凑反馈控制的或带有线性稳压的辅助电源,± 5% 甚至 ± 2% 的公差是可以实现的。

▲ 图 1:开关时显示典型栅极驱动器电压特点图

SiC MOSFET 比 Si MOSFET 开关速度更快,所以 SiC 栅极驱动器的设计要求能够承受更高 dV/dt 是非常关键的,因为这会对 MOSFET 造成振荡和损坏。在硬开关应用中,SiC MOSFET 能够产生超过 150 V / ns 的 dV/dt,所以推荐使用带有高 CMTI 额定值的驱动器。

** #2 **

一些 PCB 布局建议及技巧

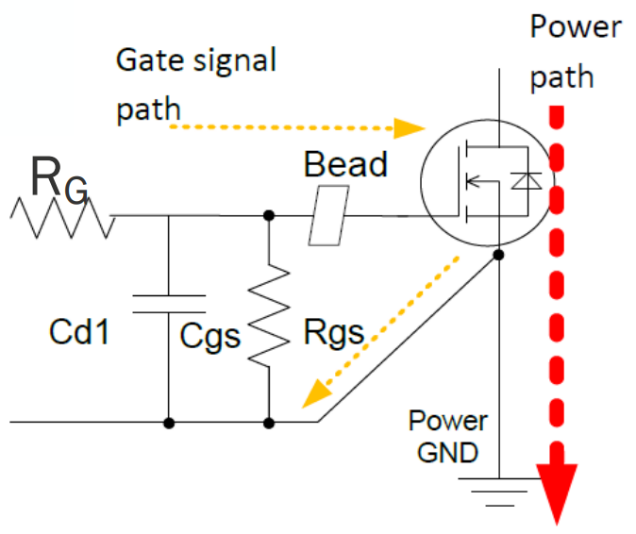

对称的 PCB 布局对于并联应用时降低驱动环路内的环流而言非常关键。另外,保证驱动回路和功率回路分开可防止串扰,而增加抑制效应(如栅极电阻器和铁氧体磁珠)可以减小栅极振荡。置于 MOSFET 栅极和源极之间的小型电容(100 pF 到 1 nF)可为高频噪声电流提供低阻抗路径(见图 2)。

▲ 图 2:SiC MOSFET 抑制噪音和栅极震荡演示

以下是需要考虑的一些附加布局相关的事项:

- 保证栅极驱动回路和功率环路分开,尽量不要有任何交叠。

- 由于 SiC 系统中的高 di/dt 和 dV/dt,寄生电感和电容能够对性能和开关行为产生巨大影响。对降低寄生效应的一些建议:

- 当选用插件封装 MOSFET 时尽量使用最短的引脚长度;

- 减小驱动芯片到 MOSFET 的距离;

- 在母线和功率地之间放置低阻抗的薄膜电容或者瓷片电容;

- 对于直流总线,使用较大的铺铜面积;

- 避免开关节点和母线以及其他敏感信号的交叠;

- 让高频率磁性材料远离敏感信号;

- 让功率环路和栅极驱动器信号分开。

- 开关节点上的电容会增加损耗。

- 总线环路中的电感增加关闭时的电压过冲。

- 栅极回路中的电感和电容降低开关速度和驱动电压的控制。

- 并联应用电感或电容的不同会导致不平衡。

** #3 **

并联 MOSFET 可提升设计的功率

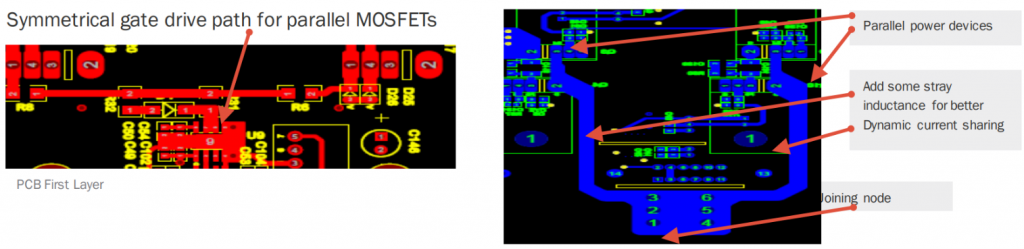

并联 MOSFET 促使大功率设计成为现实(比如交错并联升压转换器)。当用一个驱动器驱动并联 MOSFET 时,它们的栅极不应直接连在一起,而是将外置的驱动电阻单独应用到每个 SiC MOSFET 的栅极。杂散电感(范围介于 1 到 15 nH 之间)也可产生不平衡的震荡电压,但是增加栅极电阻和增加铁氧体磁珠可以增加抑制效应,以帮助降低震荡和开关损耗。并且在每个 SiC MOSFET 的驱动回路的 Kelvin source 添加一个 1 Ω 电阻器可以大幅降低任何可能流动的高峰值电流,以及作为到 VGS 的自动反馈(见图 3)。

▲ 图 3:通过增加的栅极和源极电阻器来驱动并联 SiC MOSFET

当使用模块时,一些相同规则仍旧适用。当对模块进行并联时,设计人员可在分享的栅极驱动器和单独的栅极驱动器之间进行选择。分享栅极驱动器有助于消除不同驱动器之间的不匹配问题,但是很难对栅极驱动器进行对称布局,特别是对超过两个并联模块而言。

图 4 显示的是布局并联 MOSFET 驱动器板的一些布局示例。

▲ 图 4:并联 MOSFET 设计的 PCB 布局示例

** #4 **

负驱动电压保证更安全的运行并改善抗干扰度

通常情况下,MOSFET 在 0 V 时完全关闭。增加负栅极偏压会改善抗干扰度并避免在桥式威廉希尔官方网站 应用中出现误开通,但是对于单端型功率转换器,比如反激式、升压或降压转换器,可以接受使用 0 V 关断电压。当使用图腾柱拓扑时,高 dV/dt 和 di/dt 通常会导致串扰并能在栅极生成振荡的电压尖峰,因此负电压关断(比如 - 4 V)能防止误开通,同时保证最大允许负压 - 8 V 有足够的余量。如果 PCB 布局已得到优化,只要没有误开通,负栅极偏压可以接近 - 3 V 或 - 2 V(依次降低该偏压可以降低体二极管的正向电压)。

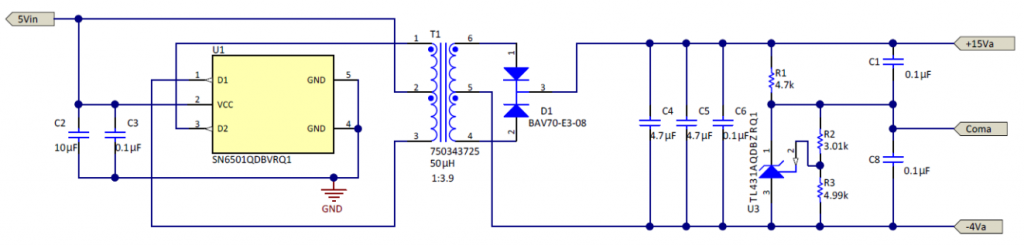

正、负栅极驱动电压解决方案可通过多种方式完成。例如,专用 15 V / - 3 V 集成电源组件可以帮助降低部件数量,而在一个稳定的 18 V 输出后加上电阻器和齐纳二极管生成 - 3 V 可以提供更多的灵活性。另一个方案是使用带有内置 DC/DC 控制器的栅极驱动器 IC,比如 Si8281。最后,通过使用推挽威廉希尔官方网站 ,比如来自德州仪器的 TIDA-01605,你可以定制你自己的完整解决方案(见图 5)。

**▲ 图 5:利用 TIDA-01605 的推挽威廉希尔官方网站 来生成 **

用于 MOSFET 驱动器的 15 V / - 4 V

当 MOSFET 关断时,在图腾柱半桥设计中增加主动米勒钳位可以大幅降低串扰(对于在 400 VDC 下使用 C3M0060065J 的对比,见 图 6)。为实现更好的钳位效果,驱动器须尽量接近 MOSFET,这样杂散电感就会达到最小化。

**▲ 图 6:无米勒钳位(左)和有米勒钳位(右)的 **

MOSFET 驱动器对比

** #5 **

其他推荐测试和微调

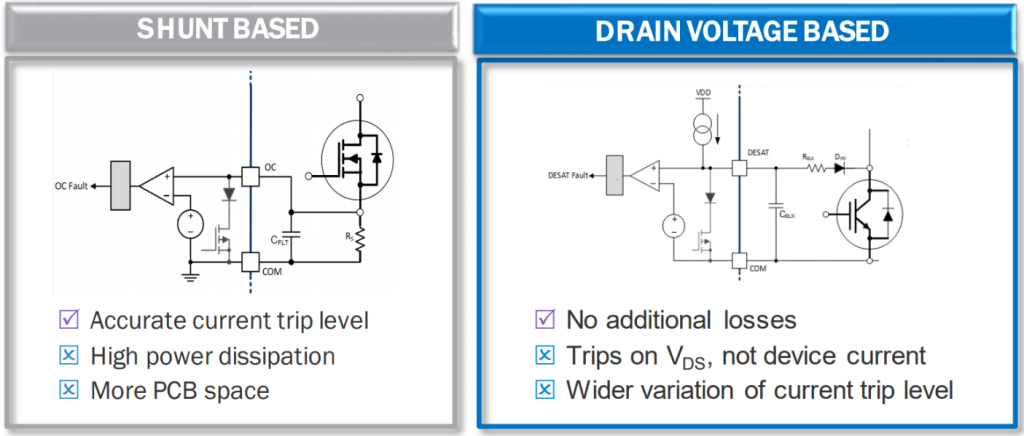

保护你的设计免受过载电流(或短路)的影响是一个必须要考虑的问题,相较于电流分流器,大部分设计人员还是倾向于采用“退饱和”方式。虽然电流分流器能提供更精确的断路电平,但它消耗了很多电力,同时需要大量的 PCB 空间。因此电流分流器更多用于需要准确的电流保护点的低功率应用。对于 SiC 来说,去饱和机制表现出色,因为它没有引入额外的损耗并能够用于大功率载荷/模块。图 7 显示了用于 SiC MOSFET 的基于分流器和基于漏极电压短路保护设计之间的差异。

▲ 图 7:用于 SiC MOSFET 的基于分流短路保护和漏极电压短路保护之间的对比

短路保护的设计非常重要,但是微调切断参数却非常棘手。设计人员须充分保护 SiC MOSFET,同时不允许任何误动作。“去饱和”电压水平须基于 MOSFET 的 RDS(on),连同最坏情况下的条件,包括高温、峰值电流和 RDS(on) 最大值进行选择。应基于开关过渡时间和抗干扰度来选择去饱和检测时间,同时须考虑最坏情况下的条件,比如低电流以及大电流波动。为确保 SiC 裸片无有害效应,Wolfspeed 推荐以下保守建议: 打开后检测时间为 250 - 500 ns,在检测后软停机持续时间为 400 - 1,500 ns,短路持续时间不超过 1 - 1.5 µs。

在大部分 SiC 模块中,当器件仍处于波动(小于1 ms)且未饱和时,须检测短路故障。不同于 IGBT,SiC 器件的故障可能必须在短路电流到达峰值之前才能检测到。可进行破坏测试来检验这个特性,比如图 8 中所示的测试示例。这项测试包含 ADuM4177 栅极驱动器和 CAB450M12XM3 SiC 模块(额定值为1,200 V / 450 A)。故障应在 550 ns 内得到检测并在之后 360 ns 内停机。

▲ 图 8:驱动器和 SiC MOSFET 破坏短路测试

** #6 **

总结

综上所述,SiC 技术使高效率和高功率密度系统成为现实,但须通过多个策略进行驱动。栅极驱动器须具备足够的驱动能力来降低损耗,且在足够高的开关频率下运行时,它必须具备高 CMTI、最低的寄生电感以及优化的去饱和检测和软停机特性。当布局 PCB 时,减小驱动回路寄生电感以防止串扰,同时使用被动组件,如电容和铁氧体磁珠也可有效抑制干扰。同时对于并联应用时,单独的栅极电阻及对称的 PCB 布局能保证均流。

-

ADI隔离栅极驱动器和WOLFSPEED SiC MOSFET2021-05-27 1060

-

Littelfuse宣布推出IX4352NE低侧SiC MOSFET和IGBT栅极驱动器2024-05-23 803

-

汽车类双通道SiC MOSFET栅极驱动器包括BOM及层图2018-10-16 0

-

SiC功率模块的栅极驱动其12018-11-30 0

-

栅极驱动器是什么2021-01-27 0

-

为SiC mosfet选择栅极驱动IC时的关键参数2023-06-16 0

-

最实用的栅极驱动芯片选型指南2019-01-29 28788

-

用于SiC MOSFET的栅极驱动器2022-08-03 1892

-

隔离式栅极驱动器:什么、为什么以及如何2023-01-30 1787

-

MOSFET和IGBT栅极驱动器威廉希尔官方网站 学习笔记之栅极驱动参考2023-02-23 627

-

SiC MOSFET栅极驱动威廉希尔官方网站 的优化方案2023-08-03 1404

-

如何为SiC MOSFET选择合适的栅极驱动器2023-10-09 769

-

隔离式栅极驱动器的演变(IGBT/SiC/GaN)2023-12-18 539

-

Littelfuse发布IX4352NE低侧SiC MOSFET和IGBT栅极驱动器2024-05-23 740

-

栅极驱动器芯片的原理是什么2024-06-10 1563

全部0条评论

快来发表一下你的评论吧 !