浅析芯片沉积工艺

电子说

描述

在了解芯片沉积工艺之前,先要阐述下薄膜(thin film)的概念。 薄膜材料是厚度介于单原子到几毫米间的薄金属或有机物层 。

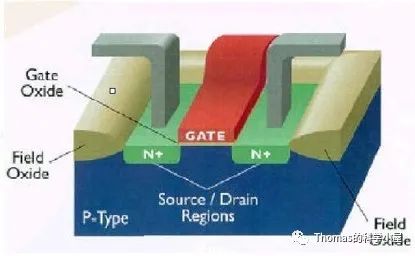

在芯片进行光刻、刻蚀之前,需要沉积一层薄膜。这层薄膜可能是各种化合物外延,多晶硅栅极,金属层导体等等。 通过对这层薄膜的光刻、刻蚀,才能雕刻出逻辑威廉希尔官方网站 的沟槽,从而装上各种导体和绝缘体,以来形成逻辑威廉希尔官方网站 的连接 。(下图是NMOS立体示意图)

沉积工艺

沉积又叫做淀积,一般通过物理方法在晶圆表面喷上去或者通过化学方法在晶圆上长出来 。沉积工艺非常直观,将晶圆基底投入沉积设备中,待形成充分的薄膜后,清理残余的部分就可以进入下一道工序。

由于市场对电子产品的性能和低电耗的要求越来越高,薄膜沉积也变得越来越复杂。不同于在表面刷一层漆那样简单,在硅片或晶圆上沉积一层,往往是纳米级别的薄膜,致密性和均匀性也有着极高的要求。

沉积工艺也可分为化学气相沉积(CVD,Chemical Vapor Deposition)和物理气相沉积(PVD,Physical Vapor Deposition)。

CVD的优点是速率快,由于在晶圆表面发生化学反应,拥有优秀的台阶覆盖率。但是缺点也很明显,产生副产物废弃。PVD的优点是无副产物,沉积薄膜的纯度高,因此多用于纯净物的金属布线 。

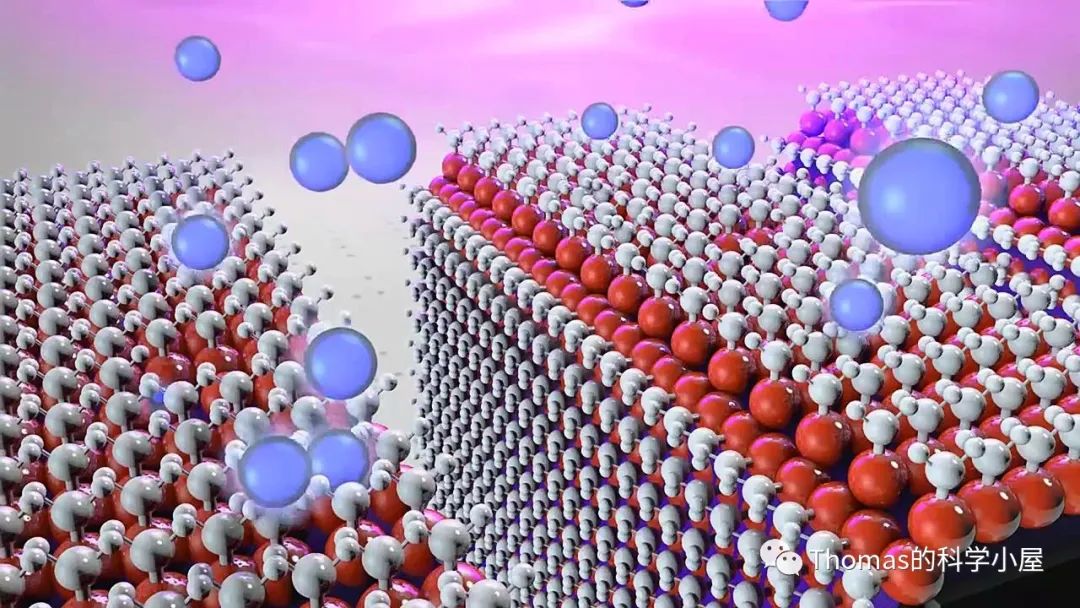

还有一种特殊的沉积方式,即原子层沉积(ALD,Atomic Layer Deposition)。原子层沉积与普通的化学沉积又相似之处,但是又有不同的生长方式。 ALD最大优势在于沉积层极其均匀的厚度和优异的台阶覆盖率 。(下图为ALD示意图)

物理气相沉积

物理气相沉积是指在真空条件下采用物理方法将材料源(固体或液体)表面气化成气态原子或分子,或部分电离成离子,并通过低压电气(或等离子体)过程,在基体表面沉积具有某种特殊功能的薄膜的技术 。(下图是溅射镀膜的原理图)

早在20世纪初,PVD技术就有应用。在进入半导体发展黄金期,工程师们发现PVD沉积温度低且可控制在500摄氏度以下,受到了业界的青睐。

在此前,由于温度低于大部分工件的回火温度,对工件的强度和韧性没有影响,PVD技术被应用于高精度刀具,磨具和摩擦磨损件的最终处理工艺。目前, PVD用于半导体制造领域逻辑和储存器上制造超薄,超纯金属和过渡金属氮化物薄膜 。

总结

在早期半导体发展的历程中,物理气相沉积发挥了巨大的作用。随着半导体微细化趋势,尤其是智能手机的崛起,让化学气相沉积和原子层沉积,得到了极大的研究和发展。

- 相关推荐

- 逻辑威廉希尔官方网站

- PVD

- 储存器

- CVD

- NMOS管

-

德国KEP 厂VOD工艺设备浅析2009-05-26 563

-

MEMS与传统CMOS刻蚀与沉积工艺的关系2020-09-01 3906

-

MEMS与传统CMOS刻蚀及沉积工艺的关系2022-12-13 2263

-

浅析换热器内漏的原因及处理工艺2022-02-11 705

-

外延沉积前原位工艺清洗的效果2022-04-12 856

-

化学气相沉积工艺(Chemical Vapor Deposition,CVD)2022-11-04 11637

-

半导体设备行业跟踪报告:ALD技术进行薄膜沉积工艺优势2023-02-16 885

-

基于PVD 薄膜沉积工艺2023-05-26 3430

-

半导体前端工艺之沉积工艺2023-06-29 1525

-

详解半导体前端工艺之沉积工艺2023-07-02 3003

-

半导体前端工艺:沉积——“更小、更多”,微细化的关键2023-08-17 1009

-

化学气相沉积与物理气相沉积的差异2023-12-26 1289

-

硅的形态与沉积方式2024-01-22 2949

-

一文详解半导体薄膜沉积工艺2024-10-31 628

-

选择性沉积技术介绍2024-12-07 233

全部0条评论

快来发表一下你的评论吧 !