MOSFET场效应晶体管设计基础

模拟技术

描述

基本结构(0和1的定义)

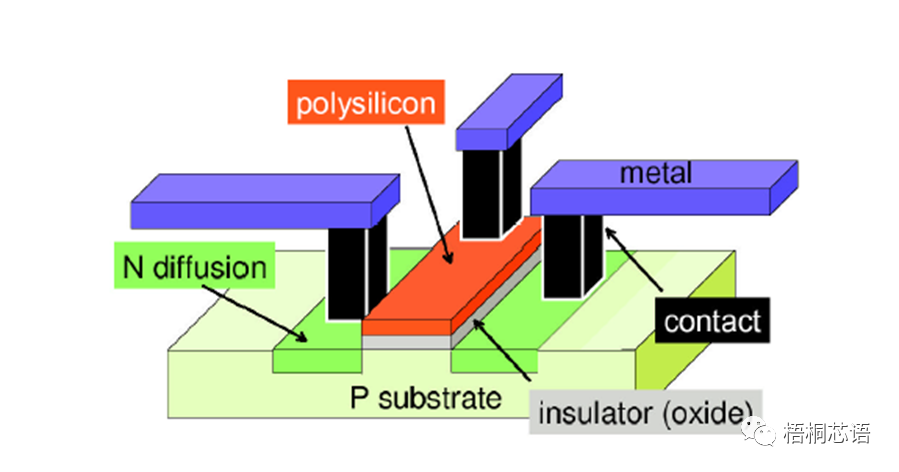

MOSFET是金属氧化物半导体场效应晶体管(Metallic Oxide Semiconductor Field Effect Transistor)的简称,有时候我们也会简写成MOS。下面是一个典型的MOSFET结构。

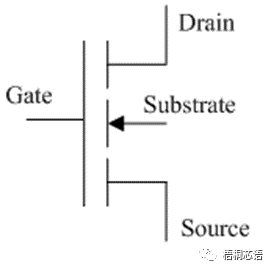

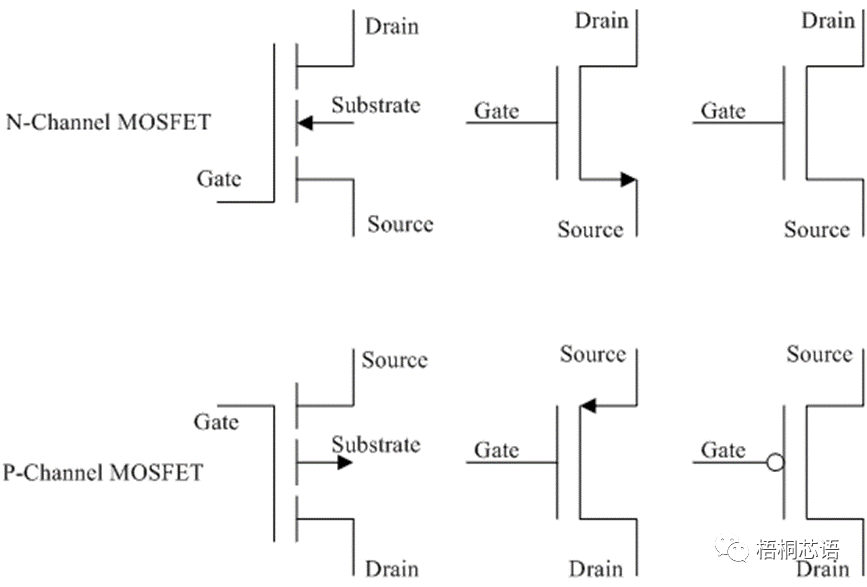

所有MOSFET都有4个端口,栅极(Gate)、漏极(Drain)、源极(Source)以及衬底(Substrate)。一般来说衬底与源极可以连在一起,或接近于一个电势,所以画图时,我们有时候会省去衬底。

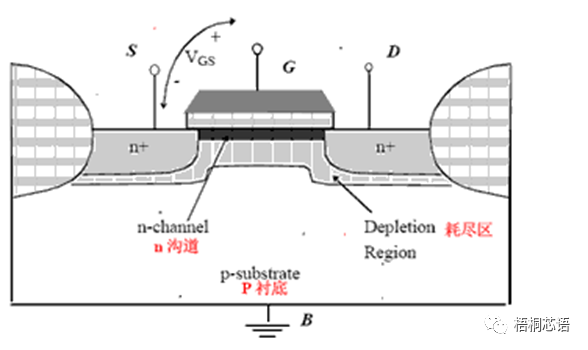

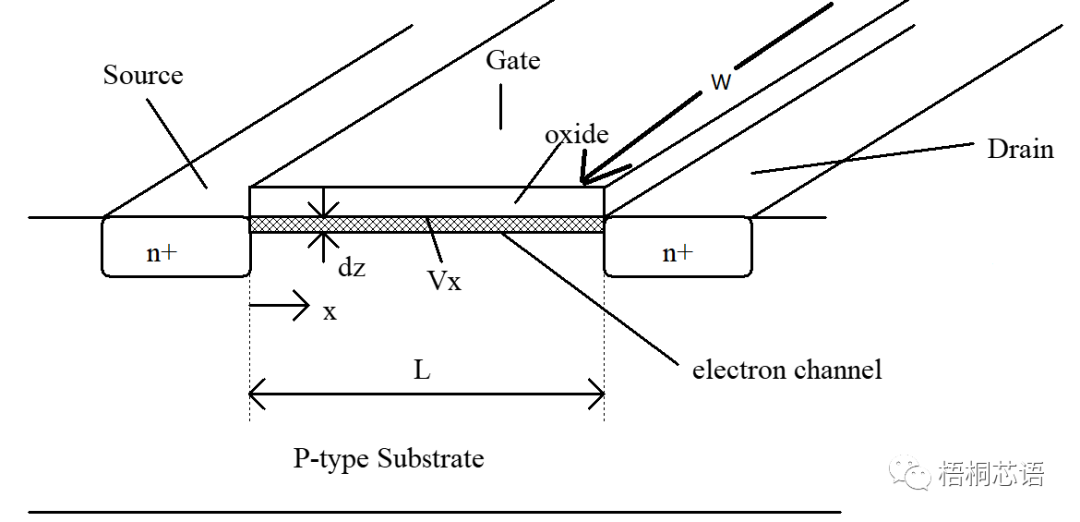

以上晶体管的剖面图,MOS晶体管的源和漏从结构上是对称的,由所接的电压决定是源还是漏。栅下面源和漏之间的地方称为沟道,源和漏之间的距离为沟道的长度(L,channel length),而与长度对应的另一边则称为沟道的宽度(W,channel width)。假设NMOS晶体管的源接地,漏接高电平,当栅电压在某个值(VT)以下,源和漏之间的沟道没有电流,晶体管不导通。当栅电压在某个值(VT)以上,源和漏之间的沟道反型,源区的电子被漏极的正电吸引产生电流,晶体管导通,电流从漏极流向源极。某个值(VT)则被称为阈值电压(Threshould Voltage)。

从MOS晶体管的工作原理看,通过控制栅极电压,可以打开或关闭漏极与源极之间的电流通道,这就是MOS管的开关特性。而数字威廉希尔官方网站 的逻辑0与逻辑1的转换,也就可以利用这个开关特性来实现了。

一般来说我们将分别将接在栅极(Gate)、漏极(Drain)和源极(Source)的电压称为VG、VD以及VS。漏极与源极的电压差叫做VDS,栅极与源极的电压差叫做VGS。

NMOS与PMOS

根据注入掺杂不同,可以分为NMOS和PMOS。如果掺杂后为n+的器件,导通后主要以电子流动产生电流沟道,所以被称为n-channel mosfet,简称NMOS。如果掺杂后为p+的器件,导通后主要以空穴流动产生电流沟道,所以被称为p-channel mosfet,简称PMOS。

在画威廉希尔官方网站 时,有很多种表示方式,都没有错。

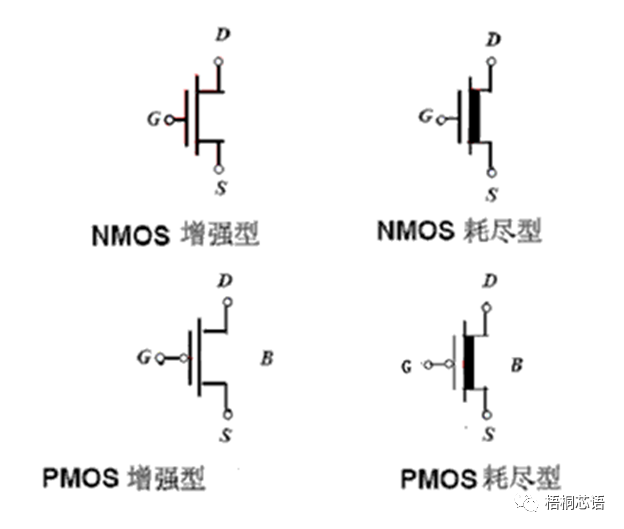

增强型MOSFET和耗尽型MOSFET

MOSFET实际上还可以分成增强型和耗尽型。

NMOS 晶体管增强型VT>0,而耗尽型VT<0。同样,PMOS 晶体管增强型VT<0,而耗尽型VT>0。

对于数字威廉希尔官方网站 设计工程师来说,基本上都是使用增强型MOSFET,耗尽型的MOSFET在早期的NMOS威廉希尔官方网站 结构有用到,现在在CMOS数字集成威廉希尔官方网站 设计中基本不会用了。所以本文中提到的MOSFET,只要不强调,就都是增强型MOSFET。

MOSFET的基本特性:输出特性曲线

与双极性(Bipolar)器件(如TTL)的电流控制电压不同,MOSFET的特点是利用电压控制电流,这也是数字威廉希尔官方网站 设计中比较容易把握的因素之一,如果定义高电平为逻辑1,地电平为逻辑0,那么就可以利用MOSFET的特性,来管理威廉希尔官方网站 中各节点的逻辑转换了。

但如果我们只知道MOSFET的开关特性,那么实际设计威廉希尔官方网站 时,就不会很好的理解功耗、面积和性能(PPA)之间的关系。所以作为一个数字威廉希尔官方网站 设计工程师,最好还是了解一下MOSFET的输出特性曲线图,也就是电压控制电流的基本原理。

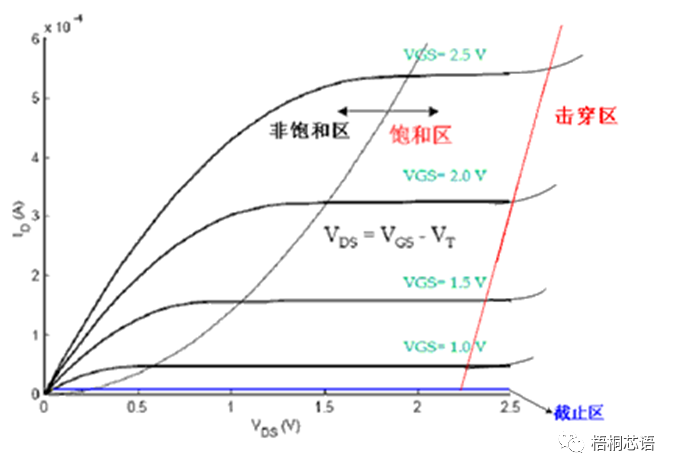

这里先看NMOS的输出特性曲线图,横轴是漏极与源极之间的压差VDS,纵轴是漏极流向源极的电流ID,不同的曲线表示不同VGS(栅极与源极的压差)的输出特性曲线。可以看到,MOSFET的工作区域可以分为截止区(off region)、非饱和区或线性区(un-satuation or linear region)、饱和区(satuation region)以及击穿区(Breakdown region)。

无论VDS是多少,只要VGS

当VGS>=VT时,沟道产生,如果此时VDS

当VGS>=VT时,沟道产生,同时VDS>=VGS-VT,那么随着VDS的增加,沟道内的电流ID,基本不会再随之增加,处于饱和状态,所以这个区域被称之为饱和区。

当VDS大于源漏的击穿电压时,器件发生击穿,则进入击穿区。

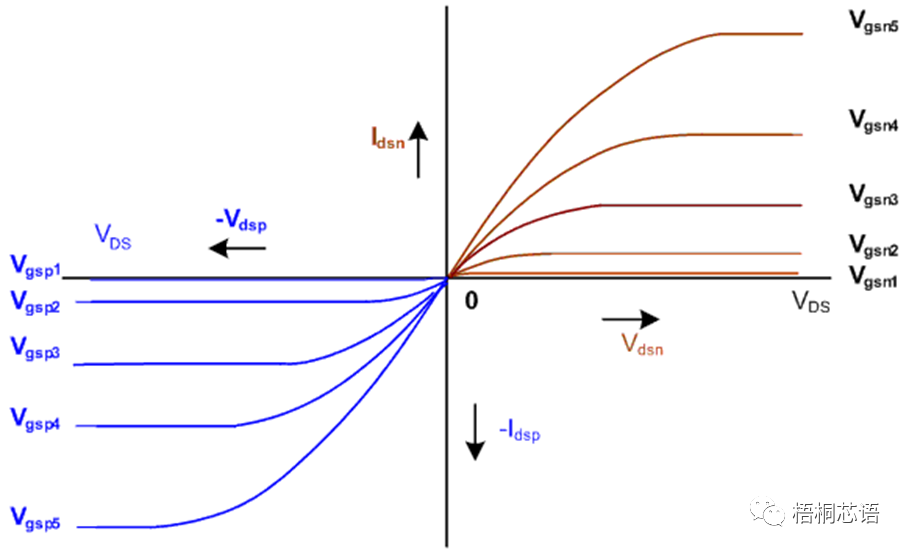

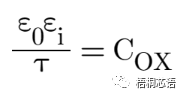

PMOS与NMOS的传输特性曲线类似,但正好落在第三象限,也就是电压及电流的的方向刚好相反:

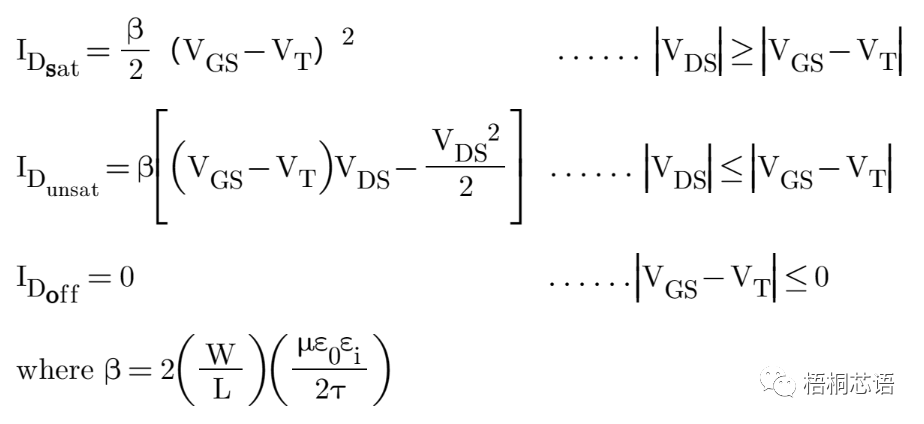

以上曲线满足的公式如下,其中因为PMOS的电流和电压刚好为负数,其实只要取绝对值就可以了:

公式中:

ε0表示真空介质电容率,8.85e-14f/cm

εi表示栅介质相对介电常数

τ表示栅介质厚度

由这三个参数组成的Cox表示为单位面积栅氧化层电容,对于同一工艺来说,是基本不变的。

W表示MOSFET的沟道宽度,L表示MOSFET的沟道长度。所以要提高驱动电流,无论是饱和还是不饱和状态下,一个较大的宽长比是非常重要的。这就像过马路,假设每个人(电子/空穴)过马路的速度一样,那么马路两边的距离(channel length)越短单位时间内能过马路的人就越多。同样的,如果马路越宽(channel width),同时过马路的人越多,单位时间内能够通过马路的人也就越多了越多。

罗马字母μ,表示电子或空穴迁移率(mobility)。需要注意的是,NMOS是电子的迁移率,而PMOS是空穴的迁移率,一般来说在同一个工艺下,NMOS的电子迁移率是PMOS的空穴迁移率的2~3倍,这个数据比较重要,将直接影响后续门威廉希尔官方网站 的设计。

MOSFET的电阻特性

电阻特性可以看成输入电压与电流之间的比值变化,因此对于一个MOSFET来说,输入电压即为VGS,如果将VS看成0V,则VG为输入电压,电阻特性可以看作VG与电流的关系,比方说如下威廉希尔官方网站 为VGS=VDS,则,所以VG与ID之间的曲线关系画在威廉希尔官方网站 边上:

也因此MOSFET可以被看成是一个Active Resistance(动态电阻)。

道法自然,追求平衡

数字威廉希尔官方网站 设计工程师,基本上掌握MOSFET的输出特性传输曲线及其公式中各参数的比例,就可以了,不是一定要非常了解其原理。

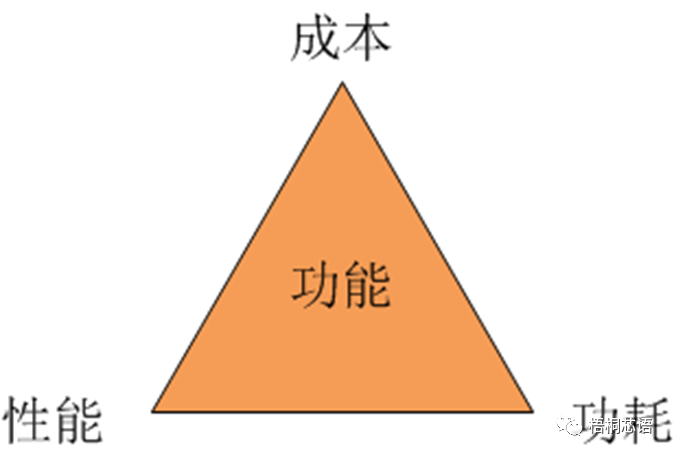

因为电流的大小,决定了电容充电的速度,也就是逻辑电平翻转的速度,当然也就决定了威廉希尔官方网站 工作频率的高低。同时电流越大,则威廉希尔官方网站 运行过程中产生的功耗越大。所以如果希望通过增加宽长比来获得更高的工作频率和性能,势必增加功耗与面积。

另一个方面,从公式看来,对电容充放电时,MOSFET基本处于饱和区,供电电压的降低,是减少功耗非常有效的方法,但由于VT大体不变,所以电流的降低又会进一步影响工作频率。

由此可见,在芯片设计中我们会有一个定律,那就是当功能不变的情况下,成本、性能和功耗(PPA)会相互制约,此消彼长。所以一个好的数字集成威廉希尔官方网站 工程师,不会追求极致,而是根据应用需要,选择往三角形的那一边偏移,寻求一个平衡点。这与道是一致的。

摩尔定律带来了什么?

摩尔定律直接的表现,就是工艺尺寸的优化,从0.18um,到0.13um,到90nm,到65(后来又shrink到55nm),再往后,一直到当前的3nm(实际沟道长度据说还是5nm)。

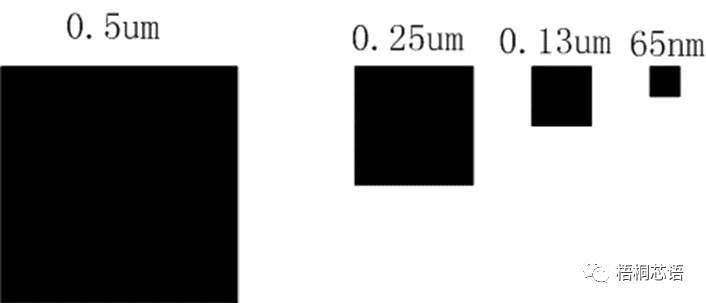

首先由工艺尺寸优化带来的最明显的变化,就是当功能不变时,MOS尺寸减小,面积减少,成本得到优化,单位面积上晶体管数量也就可以增加了:

一般来说,每一个世代(generation)的最小线条尺寸,都是上一个世代的70%,比如0.18um是0.25um的70%,65nm是90nm的70%,这样做从面积上说,刚好是上一个世代的50%,也就是缩小一半。这就是代工厂每18个月要更新一个世代的原因,为了满足摩尔定律。

回到尺寸减小带来的面积减小。由于线条尺寸越来越小,沟道长度(channel length)也越来越小,氧化层厚度降低,由此带来一个问题,那就是击穿电压也降低了,为此只能降低供电电压(VDS和VGS降低)。虽然VT也随着降低,但仍然是影响工作频率的主要因素。当然动态功耗得到优化。

其次,氧化层厚度减小,会带来越来越大的漏电电流,为了控制漏电电流,还是需要调整器件结构,提高VT。降低供电,提高VT,再次降低的工作频率,只得通过增加宽长比,用面积换取一定的性能。

不可否认,半导体制造工艺尺寸的降低,跟摩尔定律说的差不多,会带来面积的减少,性能的提高,但并不是线性的。随着线条越来越小,摩尔定律也逐步不听使唤,就算减少线条尺寸,但带来的收益并不是很高,同时还增加了大量的制造成本。所以业界逐步以应用更新替代摩尔定律,号称more than moore或者advanced moore,且一次又一次的被重新定义。

本文的限制

本文中的公式和大部分介绍,都是基于尺寸较大的工艺制程,且使用简单模型。实际设计中,还有很多需要考虑的问题,只是大方向不变。

随着工艺制程的进化,22nm以下,从16nm开始,MOSFET结构就从平面结构转向纵向结构了,本文只是通过传统的平面结构MOS管,做科普,这对于初入设计的前端工程师来说,已经可以用了。

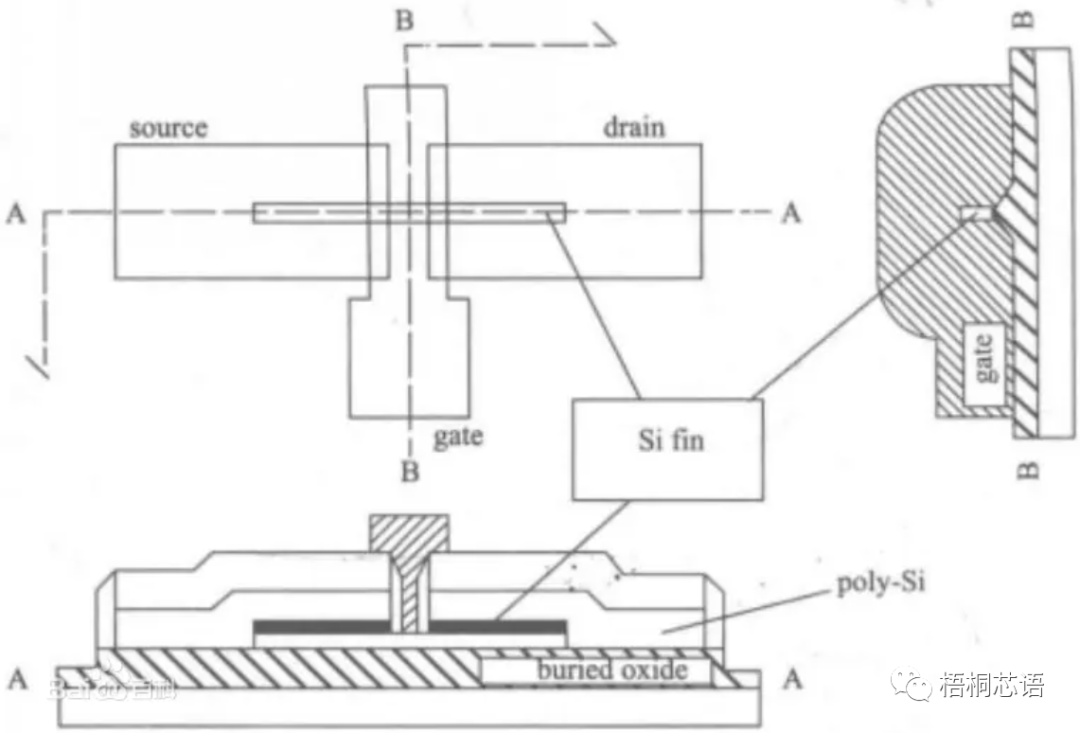

FinFET

FinFET全称Fin Field-Effect Transistor,中文名叫鳍式场效应晶体管,是一种新的互补式金氧半导体晶体管。FinFET命名根据晶体管的形状与鱼鳍的相似性。

FinFET从16nm工艺开始出现,是一种纵向结构器件,与平面器件不同的是,栅极在两边夹住晶体管,使得沟道长度不变的情况下,沟道宽度增加了一倍,且从生产工艺上,更容易控制尺寸,规避了平面结构制造工艺上的缺陷。

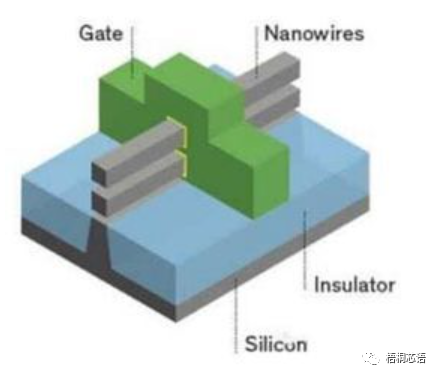

GAAFET

GAAFET是(Gate-all-around FETs)采用的是纳米线沟道设计,沟道整个外轮廓都被栅极完全包裹,代表栅极对沟道的控制性更好。相比之下,传统的FinFET 沟道仅3 面被栅极包围。GAAFET 架构的晶体管提供比FinFET 更好的静电特性,可满足某些栅极宽度的需求。这主要表现在同等尺寸结构下,GAA 的沟道控制能力强化,尺寸可以进一步微缩。

现在主要在3nm工艺下使用。

实际上GAAFET 有两种结构,一种是使用纳米线(Nanowire)作为电子晶体管鳍片的常见 GAAFET;另一种则是以纳米片(Nanosheet)形式出现的较厚鳍片的多桥通道场效应管 MBCFET,这两种方式都差不多。

其中 MBCFET 相比纳米线技术拥有更大的栅极接触面积,从而在性能、功耗控制上会更加出色。传统的 GAAFET 工艺采用三层纳米线来构造晶体管,栅极比较薄,而MBCFET工艺使用纳米片构造晶体管,可以提供更低的工作电压、更高的电流效率(即驱动电流能力)和高度的设计灵活性。虽然MBCFET易于生产,且能承载更大电流,但栅控能力不够纳米线强。

现在国内在立体结构器件制造工艺上与国外还有较大的差距,而从16nm到3nm还有4个世代,如果按照摩尔定律来算,理想状态下,我们想达到国外的3nm工艺量产,还要6年。这6年,国外的技术又会发展到哪里?

全部0条评论

快来发表一下你的评论吧 !