什么是FPGA?FPGA现场可编程门阵列的综合指南

可编程逻辑

描述

什么是FPGA?

现场可编程门阵列 (FPGA) 是可以在制造后进行编程和重新编程以实现数字逻辑功能的半导体器件。FPGA 通过提供可配置为执行各种任务的可编程硬件块和互连,提供了实现数字威廉希尔官方网站 的独特方法。

FPGA 的组件

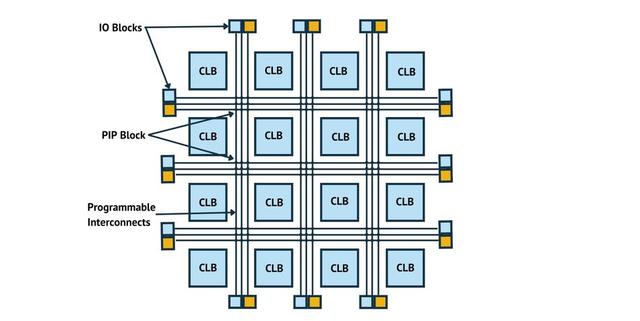

FPGA(现场可编程门阵列)由多个关键组件组成,这些组件协同工作以实现定制数字威廉希尔官方网站 的实现和配置。FPGA 的主要组件有:

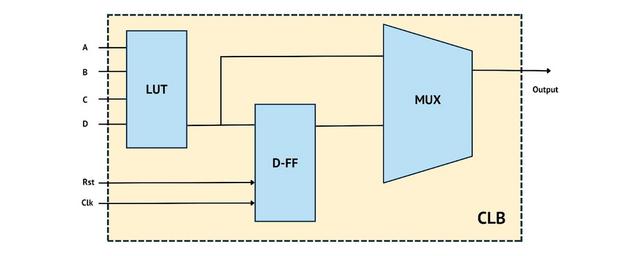

- 可配置逻辑块 (CLB): 这些是 FPGA 的基本构建块,包含查找表 (LUT)、触发器,有时还包含专用算术单元。CLB 可配置为执行各种组合和顺序逻辑功能。

- **可编程互连点 (PIP): **这些是连接 CLB 和 FPGA 内其他组件的可编程开关和接线资源。PIP 允许芯片上不同元件之间的信号灵活路由和互连。从本质上讲,晶体管是 FPGA 的基本构建模块,形成 CLB 和 PIP。

- **输入/输出块 (IOB): **这些是 FPGA 与外部设备或板上其他组件之间的接口点。IOB 可配置为支持各种信号标准和协议,使 FPGA 能够与各种外设进行通信。

- **Block RAM (BRAM): **这是 FPGA 上可用的片上存储器,用于存储数据和实现存储器功能。BRAM 比片外存储器更快,并且可以以更低的延迟进行访问。

- **数字信号处理 (DSP) 块: **这些是专门用于高速执行算术运算(例如乘法和累加)的专用硬件块。DSP 模块通常用于信号处理和滤波应用。

- **时钟管理资源: **包括锁相环 (PLL) 和数字时钟管理器 (DCM),用于在 FPGA 内生成、分配和管理时钟信号。这些资源有助于保持整个设备的精确定时和同步。

- **配置存储器: **这是存储配置比特流的闪存,它对FPGA进行编程以实现所需的数字威廉希尔官方网站 。比特流在启动时或需要重新编程时加载到 FPGA 中。

传统上,代码被编写并编译成在处理器上运行的指令。然而,对于 FPGA,可以使用硬件描述语言 (HDL) 以不同的方式编写代码。然后,该代码被合成到物理硬件模块中,可以将其配置为直接在 FPGA 上执行所需的逻辑功能。FPGA 中的硬件模块由寄存器和各种类型的逻辑门组成,例如 AND、OR、NOR、NOT、XOR 和 XNOR 门。这些门可以组合起来创建复杂的数字威廉希尔官方网站 。

FPGA 灵活性的关键在于使用查找表 (LUT) 来实现逻辑门。这些逻辑块之间的互连也是可编程的,允许灵活的信号布线和路由。通过使这些 LUT 可编程并使用可重新配置的交换结构连接它们,FPGA 可以定制来执行各种任务。通过提供可以运行用户所需的任何代码的单一设备,FPGA 已在从原型设计到高性能计算的各种应用中变得流行。

HDL 语言:VHDL 和 Verilog

硬件描述语言 (HDL) 用于描述高抽象级别的数字威廉希尔官方网站 。FPGA 设计中使用的两种主要 HDL 是 VHDL 和 Verilog。

- **VHDL: **VHDL(VHSIC 硬件描述语言)是一种强类型、详细的语言,提供高级抽象,使编写复杂设计变得更加容易。它广泛应用于欧洲以及航空航天和国防等行业。

- Verilog: Verilog 是一种更简洁的、类似 C 的语言,在美国和商业领域很流行。与 VHDL 相比,它的抽象级别较低,这使得复杂设计更具挑战性,但也可以更好地控制设计。

这两种语言都有其优点和缺点,VHDL 和 Verilog 之间的选择通常取决于个人喜好或行业标准。

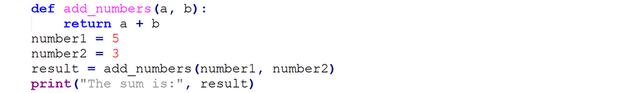

为了更好地理解其中的差异,让我们看一下将两个数字相加的 Python 代码:

在Python中,代码是用高级语言编写的,该语言抽象了底层硬件的细节。函数 add_numbers 接受两个输入参数 a 和 b,并返回它们的和。该代码由处理加法运算的处理器执行。

现在,让我们看一下将两个数字相加的简单 Verilog 代码:

在此 Verilog 代码中,我们定义了一个名为 Adder 的模块,该模块具有两条 4 位输入线 A 和 B,以及一条 4 位输出线 Sum。该代码描述了使用分配语句将两个数字相加的数字威廉希尔官方网站 的行为,该分配语句利用 FPGA 的可编程逻辑资源直接在硬件中执行。结果是设计用于将两个 4 位数字相加的定制威廉希尔官方网站 。

两种方法之间的主要区别在于,Python 代码由处理器顺序执行,而 Verilog 代码描述了使用 FPGA 直接在硬件中实现的数字威廉希尔官方网站 。这意味着基于 FPGA 的加法器可以并行执行加法运算,并且与执行 Python 代码的处理器相比,速度通常更快。然而,Python提供了更多的灵活性和易用性,而Verilog则需要对数字威廉希尔官方网站 设计和FPGA资源有更深入的了解。

FPGA的优点

与其他技术相比,FPGA 具有多项优势,包括:

- 灵活性: FPGA可以重新编程以实现不同的功能,使其适合广泛的应用。

- **快速原型设计: **FPGA 允许设计人员快速测试和迭代其设计,从而缩短上市时间。

- 并行性: FPGA 可以同时执行多个任务,这可以提高某些应用的性能。

- **定制: **FPGA 可以创建满足特定要求的专用硬件,通常可以优化性能并降低功耗。

- **可重新配置性: **FPGA 可以在现场重新配置,从而无需更换整个硬件即可进行更新、错误修复或功能添加。

- **更低的 NRE 成本: **FPGA 开发不需要与定制 ASIC 设计相关的高额一次性工程 (NRE) 成本,这使得它们更适合小规模生产或概念验证项目。

- **可扩展性: **FPGA 设计可以根据要求轻松扩展或缩小,从而实现高效的资源利用和经济高效的解决方案。

- **安全性: **FPGA 可以通过基于硬件的加密和安全启动功能提供更高的安全性,与基于软件的实现相比,这些功能更难以篡改。

- **模拟和数字接口: **FPGA 可以与各种模拟和数字外设连接,从而简化系统集成并允许不同组件之间的无缝通信。

- **寿命长: **基于 FPGA 的设计通常比 ASIC 具有更长的寿命,因为它们可以更新和重新编程以适应不断发展的标准和技术。

- 设计重用: IP 核和之前开发的 FPGA 设计可以轻松重用并集成到新项目中,从而减少开发时间和工作量。

FPGA的缺点

与 ASIC 和微控制器等其他技术相比,FPGA 有一些缺点。一些缺点包括:

- 成本: FPGA 可能比微控制器或 ASIC 更昂贵,特别是对于大批量生产。对于大批量来说,FPGA 的单位成本通常高于 ASIC 或微控制器。

- **功耗: **FPGA 通常比 ASIC 和微控制器消耗更多的功耗,这可能是功耗敏感应用中的一个问题。

- 设计复杂性: FPGA 的设计过程可能比微控制器更复杂,需要硬件设计、HDL、综合和布局布线工具方面的专业知识。

- **性能限制: **虽然 FPGA 提供并行性并且可以为某些任务提供高性能,但对于某些应用,它们可能不如 ASIC 快,因为 ASIC 是针对特定用途定制设计的,并且可以针对性能进行高度优化。

- **尺寸: **FPGA 可能比同等的 ASIC 或微控制器更大,因为它们包含用于可编程性和重新配置的额外资源。

- **配置时间: **FPGA 需要在启动时进行配置,这可能会导致启动时间比 ASIC 和微控制器更长。

FPGA、ASIC、PLD、微控制器

FPGA、专用集成威廉希尔官方网站 (ASIC)、可编程逻辑器件(PLD)和微控制器都是用于实现数字逻辑功能的技术,但它们在各个方面有所不同。让我们对这些技术进行比较和对比:

- **FPGA: **如前所述,FPGA 是可重新编程的,因此适合广泛的应用。它们提供高性能和并行性,但与 ASIC、PLD 和微控制器相比更昂贵且耗电。

- **ASIC: **ASIC 是针对特定应用定制的,可优化性能和功耗。然而,它们的前期成本高、开发时间长,并且缺乏 FPGA 和 PLD 的灵活性,因此适合大批量生产。

- **PLD: **PLD包括复杂可编程逻辑器件(CPLD)和简单可编程逻辑器件(SPLD),是类似于FPGA的可重构硬件,但复杂性较低,资源较少。它们非常适合更简单的数字设计,并且可以提供比 FPGA 更低的成本和功耗,但可能缺乏 FPGA 对于更复杂应用的性能和灵活性。

- **微控制器: **微控制器是具有集成内存、处理和输入/输出功能的通用计算设备。它们通常比 FPGA 和 PLD 速度慢且并行性较差,但更便宜、功耗更低并且更易于开发。

总之,FPGA 提供灵活性和并行性,ASIC 提供优化的性能和功耗,PLD 提供简单性和成本效益,而微控制器经济高效且易于开发。技术的选择取决于应用的具体要求以及性能、功耗、开发时间和成本之间所需的权衡。

FPGA 设计流程和方法

在本节中,我们将探讨 FPGA 设计流程,包括设计流程、硬件描述语言、寄存器传输级 (RTL) 设计、综合、实现以及测试和调试。

设计流程概述

FPGA 设计流程由几个步骤组成,指导设计人员从概念到功能齐全的 FPGA 实现。这些步骤包括:

- 设计输入: 设计人员使用 VHDL 或 Verilog 等 HDL 创建所需数字威廉希尔官方网站 的高级表示。

- **RTL 设计和仿真: **HDL 代码被转换为 RTL 表示,然后进行仿真以验证功能和性能。

- 综合: RTL 设计被转换为门级网表,即使用门和触发器的数字威廉希尔官方网站 的表示。

- **实现: **门级网表映射到 FPGA 的资源,包括 CLB、DSP 切片和可编程互连。此步骤包括布局布线和比特流生成。

- **测试和调试: **使用仿真工具、测试平台或目标硬件对 FPGA 器件进行测试和调试,以确保正确的功能和性能。

在整个设计流程中,使用各种工具和软件来促进 FPGA 设计的设计、仿真、综合和实现。

RTL 设计与仿真

RTL 设计是数字威廉希尔官方网站 的中间表示形式,重点关注寄存器之间的数据流以及对该数据执行的操作。RTL 仿真用于在进入综合和实现阶段之前验证设计的功能和性能。

常见的RTL仿真工具包括ModelSim、XSIM和VCS。这些工具允许设计人员执行功能和时序仿真,这有助于在设计过程的早期识别和修复设计错误和性能瓶颈。

综合与实施

在综合阶段,RTL 设计被转换为门级网表,它代表使用门和触发器的数字威廉希尔官方网站 。此过程涉及优化面积、速度和功耗的设计。常见的综合工具包括 Xilinx Vivado、Intel Quartus 和 Synopsys Design Compiler。

实现阶段涉及将门级网表映射到 FPGA 的资源,例如 CLB、DSP 切片和可编程互连。此步骤包括布局布线(确定 FPGA 上设计元素的物理位置)和比特流生成(创建配置 FPGA 的二进制文件)。实现工具包括 Xilinx Vivado 和 Intel Quartus。EDA(电子设计自动化)工具在 FPGA 设计流程中发挥着关键作用,可协助设计人员完成所有任务,包括综合、布局、布线和验证。

测试和调试 FPGA 设计

测试和调试是 FPGA 设计过程中的关键步骤,确保设计正确运行并满足性能要求。常见的测试方法包括:

- **仿真: **使用仿真工具在虚拟环境中测试设计,从而实现更快、更可控的测试。

- **在线测试: **在测试平台或目标硬件上测试 FPGA 设计,通常使用逻辑分析仪或示波器来监控信号并识别问题。

调试 FPGA 设计涉及识别和修复与功能、性能和资源使用相关的问题。调试的最佳实践包括:

- 使用描述性信号和变量名称来提高代码可读性。

- 采用模块化设计方法,将设计分解为更小、更易于管理的组件。

- 利用仿真工具和在线测试来识别和隔离问题。

通过遵循 FPGA 设计流程并采用测试和调试的最佳实践,设计人员可以创建满足其特定应用要求的高质量 FPGA 设计。

FPGA 设计实例和应用

在本节中,我们将探讨 FPGA 设计的各种示例和应用。

使用 FPGA 的数字信号处理 (DSP)

DSP 是对数字信号(例如音频、视频或传感器数据)的处理和分析。由于其并行性和灵活性,FPGA 非常适合 DSP 任务。基于 FPGA 的 DSP 应用的一些示例包括:

- **音频处理: **FPGA 可用于音频效果、均衡、降噪和压缩。

- **图像处理: **FPGA 可以执行实时图像处理任务,例如边缘检测、滤波和对象识别。

- **软件定义无线电 (SDR): **FPGA 可用于实现各种无线电通信协议,从而实现高度可定制和适应性强的无线电系统。

基于 FPGA 的人工智能 (AI) 机器学习 (ML)

FPGA 在 AI 和 ML 应用中发挥着重要作用,具有低延迟、高吞吐量和能源效率等优势。基于 FPGA 的机器学习和人工智能项目的一些示例包括:

- 深度学习加速器: 与传统的基于CPU和GPU的解决方案相比,FPGA可用于加速深度神经网络的训练和推理,提高性能并降低功耗。

- 边缘人工智能: FPGA 支持边缘人工智能处理,减少数据传输到云端的需求,并提高隐私性和安全性。

- **定制 AI 硬件: **FPGA 允许实施针对特定应用量身定制的定制 AI 算法,从而优化性能和功效。

网络和通信中的 FPGA

FPGA 广泛应用于网络和通信系统,具有高性能、灵活性和适应性。基于 FPGA 的网络和通信项目的一些示例包括:

- **网络交换机和路由器: **FPGA可用于实现高性能、低延迟的以太网交换机和路由器,实现更快、更高效的数据传输。

- **光通信: **FPGA可用于光通信系统,例如密集波分复用(DWDM),以实现高速数据传输和信号处理。

- **无线通信:**FPGA可用于实现各种无线通信协议,例如5G、Wi-Fi和蓝牙,从而实现可定制和适应性强的通信系统。

总之,FPGA 是多功能且功能强大的设备,可用于从数字信号处理到机器学习和网络的广泛应用,其中微处理器的功能可能超出所需。通过利用 FPGA 的独特功能,设计人员可以为各种行业和用例创建创新的高性能解决方案。

FPGA 设计最佳实践

在本节中,我们将讨论 FPGA 设计的一般最佳实践,重点关注代码可读性、模块化以及优化性能、功耗和资源使用设计的技术。

代码可读性和模块化

保持代码可读性和模块化对于高效 FPGA 设计至关重要。通过遵循这些实践,您可以提高设计的可维护性和可扩展性:

- **描述性命名: **为信号、变量和模块使用有意义的名称,使代码更易于理解。

- **注释: **包括注释来解释代码的目的和功能,特别是对于复杂或不明显的操作。

- 模块化: 将您的设计分解为更小、更易于管理的模块或组件。这种方法使调试、维护和重用代码变得更加容易。

优化 FPGA 设计的性能、功耗和资源使用

优化 FPGA 设计可以帮助您在性能、功耗和资源使用之间实现所需的平衡。一些优化技术包括:

- **流水线: **将复杂的操作分解为较小的阶段并并行处理它们,以提高吞吐量并减少延迟。

- **资源共享: **重复使用硬件资源(例如乘法器、转换器或内存块)进行多个操作,以节省面积和功耗。

- **时钟门控: **禁用设计中未使用或空闲部分的时钟域信号,以降低动态功耗。

除了这些技术之外,请务必利用综合和实现工具(例如 Xilinx Vivado 和 Intel Quartus)提供的优化功能。这些工具可以帮助您根据特定的设计要求和限制获得最佳的结果。

通过遵循 FPGA 设计的最佳实践并采用优化技术,您可以创建满足特定应用需求的高质量、高效的设计。

常见问题 (FAQ)

- 使用 FPGA 的主要优点是什么?

FPGA 提供灵活性、可重编程性、并行性和快速原型设计功能,使其适合广泛的应用。 - 如何为我的项目选择合适的 FPGA?

为您的项目选择 FPGA 时,请考虑 FPGA 系列、FPGA 供应商、资源要求、性能需求和成本等因素。 - 我可以将 FPGA 用于机器学习和 AI 应用吗?

是的,FPGA 可用于机器学习和人工智能应用,提供低延迟、高吞吐量和能源效率。 - VHDL 和 Verilog 之间有什么区别?

VHDL 是一种强类型、冗长的语言,具有较高的抽象级别,而 Verilog 是一种更简洁、类似 C 的语言,具有较低的抽象级别。VHDL 和 Verilog 之间的选择通常取决于个人喜好或行业标准。 - 开始 FPGA 设计需要哪些工具和软件?

要开始 FPGA 设计,您需要 HDL 编辑器、仿真工具(例如 ModelSim、XSIM)、综合工具(例如 Xilinx Vivado、Intel Quartus)和实现工具(例如 Xilinx Vivado、Intel Quartus)。

结论

在这本综合指南中,我们探讨了 FPGA 设计的基础知识、设计流程、各种应用以及创建高效、高质量设计的最佳实践。通过了解 FPGA 的工作原理并利用其提供的独特功能,设计人员可以为各种行业和用例创建创新的解决方案。

-

FPGA为现场可编程门阵列,通过编程改变硬件的结构2013-10-05 0

-

现场可编程门阵列2015-03-13 0

-

现场可编程门阵列有哪些应用?2019-08-06 0

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 0

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 0

-

XC5VLX85-1FF676C现场可编程门阵列2021-04-26 0

-

XC6SLX75T-2CSG484I现场可编程门阵列2021-04-26 0

-

XC7A200T-2FFV1156I现场可编程门阵列2021-04-26 0

-

FPGA-现场可编程门阵列2021-07-30 0

-

现场可编程门阵列的结构与设计2009-07-07 1511

-

现场可编程门阵列的供电原理及应用2010-03-17 1498

-

现场可编程门阵列(FPGA)——知识专题2011-09-08 3119

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 908

-

FPGA现场可编程门阵列的综合指南2023-12-07 698

-

现场可编程门阵列设计流程2024-03-16 1952

全部0条评论

快来发表一下你的评论吧 !