Xilinx FPGA从spi flash启动配置数据时的地址问题

描述

FPGA上电(Master)

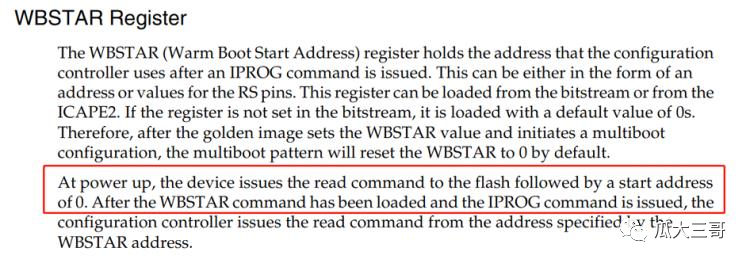

fpga 上电时,默认是从 flash 的 0x00 地址开始读数据。如 UG470 文档 page144 描述

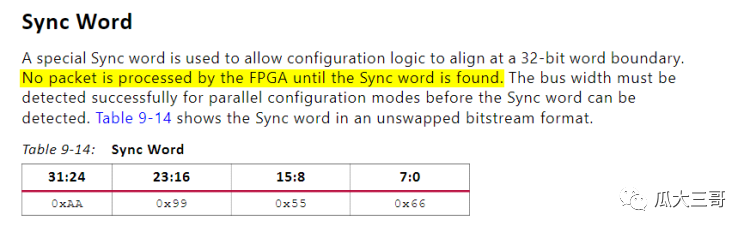

fpga 会从 0 开始读,地址不断自增,直到读取到有效的同步字 sync word(0xAA995566),才认为接下来的内容是一个有效的 bin 文件内容的开始。读到有效 sync word 后不会再继续读搜寻其他的 bin 文件。如 UG470 文档 page81 描述:

几种情况

只有一个 bit 文件,使用如下命令将该 bit 文件写出转换为 mcs 文件,并烧入 spi flash 中。

write_cfgmem -format mcs -interface spix4 -size 8 -loadbit {up

0x400000 ./soc_top.bit} -file soc_top_0x400000.mcs -force

该 bit 文件在 flash 中存放的起始地址是 0x400000 ,上电 fpga 能正常启动,因为前部分的地址 0x000000-0x400000 之间都是无效数据, fpga 从 0x000000 地址开始读,没有有效的 sync word ,读地址不断增加,直到 0x400000 地址才会读到同步字,然后就能正常的从 0x400000 开始配置。

有两个 bit 文件,使用该命令转换为一个 mcs 文件

write_cfgmem -format mcs -interface spix4 -size 8 -loadbit {up 0x000000 ./design1.bit

up 0x400000 ./design2.bit} -file mixed.mcs -force

第一个 bit 文件放在 0x000000 地址,第二个放在 0x400000 地址,烧写 flash ,上电后 fpga 从 deign1.bit

启动,因为第一个 bit 在前面, fpga 上电后从 0x000000 地址开始读,会先读到 deign1.bit ,然后成功地从deign1.bit 初始化。

若把 mcs 文件中关于 deign1.bit 的 FDRI data 的内容手动改为其他值,使得配置的时候会出现 CRC 校验错误, deign2.bit 相关的内容不变,烧写进flash,上电, FPGA 无法正常配置数据,既不会从deign1.bit启动,也不能从deign2.bit 启动,这是因为第一个bit在前面, fpga 上电后从 0x000000 地址开始读,会先读到 deign1.bit ,然后从 deign1.bit 开始初始化,但是会发生CRC错误,然后又fallback 回 0 地址读,依然是读到 design1.bit 的数据,还是 CRC 错误,最后发生配置失败。

若只把 mcs 文件中关于 deign1.bit 的 sync word 的内容手动改为其他值,比如 0xAA997866 ,deign2.bit 相关的内容不变,烧写进 flash 上电, FPGA 成功从 deign2.bit 启动。这是因为第一个 bit 在前面, fpga 上电后从0x000000 地址开始读,读到 deign1.bit 的 sync word 为 0xAA997866 时,发现不是有效的 sync word ,不会判断接下来的内容是属于一个有效的配置文件,于是继续自增地址往上读,直到读到 0x400000 地址后面,成功读到 design2.bit 的 sync word ,发现有效,然后从 deign2.bit 开始初始化。这样就跳过了前面 deign1.bit 的内容。

bitstream 约束

对bit流进行压缩

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

打开看门狗功能

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

如果加载 Update_Image 配置文件失败后,没有返回加载 Golden_Image ,则会根据指定的时间启动看门狗,强制返回加载 Golden_Image 。

生成 bit 文件的头部添加 IPROG 命令和设置 WBSTAR 的命令

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x0400000 [current_design]

配置时执行到 IPROG 命令后,会直接跳转到指定的地址中继续执行配置。可用于 Golden_Image 中设置为跳转到 Update_Image 启动。其实加不加这个约束,生成的bit流中的头部,都会有 IPROG 和设置 WBSTAR 的相关命令的占位空间,只是不加该约束时, IPROG 的位置会由 000000 替代, NOP 指令,只是空的占位符;而写 WBSTAR 寄存器的指令依然存在,但是写 WBSTAR 的值却是 0 。

-

FX3从SPI启动并配置FPGA如何分离SPI闪存2018-11-29 0

-

解析FPGA从SPI Flash启动配置数据时的地址问题2022-07-15 3899

-

怎样从SPI FLASH加载FPGA程序2016-04-29 0

-

怎么使用SPI闪存启动选项实现FPGA配置文件的故障安全升级?2019-05-30 0

-

FX3从SPI启动并配置FPGA2019-06-19 0

-

在BPI快速模式下配置FPGA无法从Flash启动的解决办法?2020-06-04 0

-

如何确定SPI Flash中FPGA配置的大小2020-06-09 0

-

可以从Virtex 6控制Xilinx Platform Flash XL?2020-06-16 0

-

使用高速SPI Nor Flash的FPGA配置2020-09-18 0

-

SPI方式FPGA配置和SPI flash编程2011-05-16 963

-

基于SPI FLASH的FPGA多重配置2014-01-24 14778

-

Xilinx7系列基于PCIe的设计如何满足PCIe启动时间的要求2017-02-07 3566

-

FPGA配置– 使用JTAG是如何烧写SPI/BPI Flash的?2017-02-08 8345

-

基于FPGA 的SPI Flash 控制器设计及验证2017-11-22 13437

-

采用Xilinx FPGA的AFE79xx SPI启动指南2024-11-15 94

全部0条评论

快来发表一下你的评论吧 !