如何在FPGA中实现随机数发生器

描述

分享如何在Xilinx Breadboardable Spartan-7 FPGA, CMOD S7中实现4位伪随机数发生器(PRNGs)。

现场可编程门阵列(FPGA)是一种高度可配置的集成威廉希尔官方网站 ,它使开发者能够测试和重写程序以执行各种功能。它在原型设计、测试数字威廉希尔官方网站 和实现生产中的定制数字系统方面很受欢迎。

该领域涉及但不限于:

数字信号处理

-实现滤波器、变换和信号发生器

-示例应用:音频、视频处理、通信系统和雷达处理。

机器学习(ML)和人工智能(AI)

-实现定制的ML和AI算法,如CNN

-示例应用:计算机视觉、自然语言处理和语音识别

通信系统和数据存储中的加密安全

-实现加密算法,如AES、DES和RSA

-示例应用:安全通信系统和数据存储

工业控制系统

-在各种工业中实现定制的控制系统:机器人、自动化和过程控制

-示例应用:自主车辆控制系统和智能电网控制系统

航空航天和国防

-实现定制的数字系统,具有高性能、低功耗和抗辐射能力

-示例应用:雷达处理和制导系统

1、 问题陈述

虽然随机性是安全网络物理系统(CPS)的一个重要组成部分,但如何在FPGA中实现随机数发生器呢?

今天分享一下关于如何在Xilinx Breadboardable Spartan-7 FPGA, CMOD S7中实现4位伪随机数发生器(PRNGs)。

请注意,PRNGs与真随机数发生器不同。PRNGs可能在输出中存在偏差或模式,因此应结合其他安全措施使用,如安全的密钥管理实践和强大的加密算法,以保护目标系统。

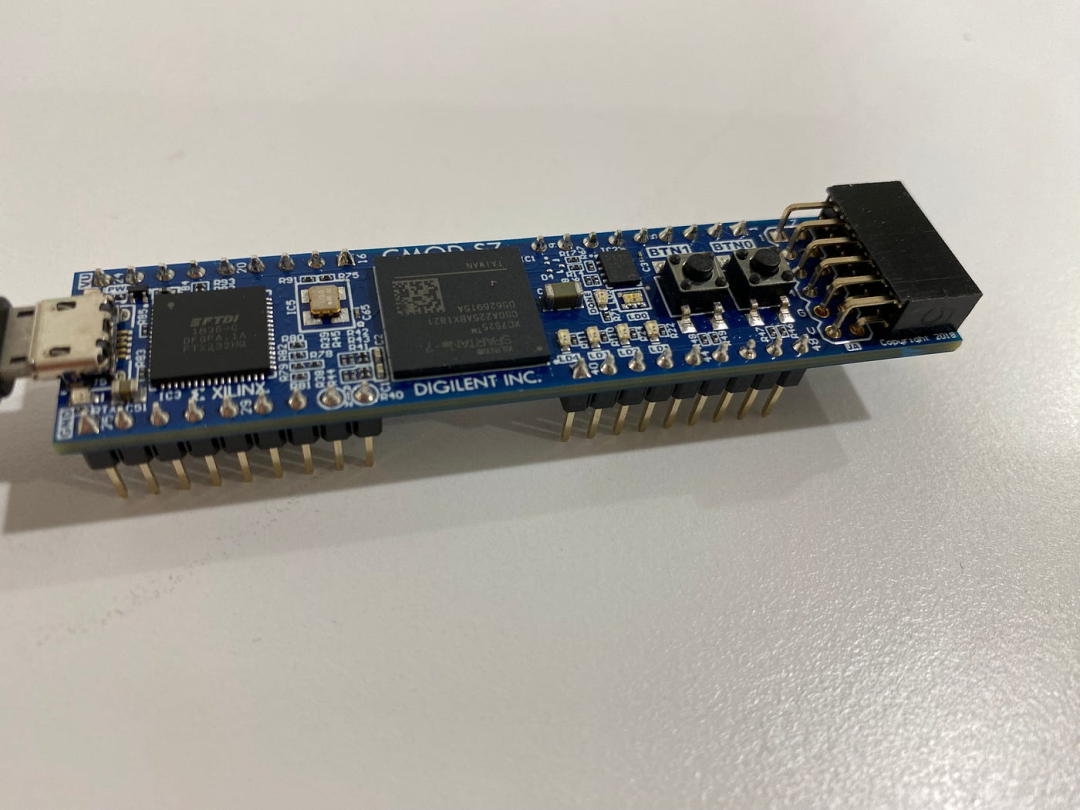

CMOD S7的近景

CMOD S7的近景

下面是用Verilog语言编写的程序,使用了Vivado软件。在这个程序中,主要有3个主要功能:

这个程序使用计数器来确定1秒的间隔

这个程序在反馈中进行LFSR操作,并计算4位lfsr_reg

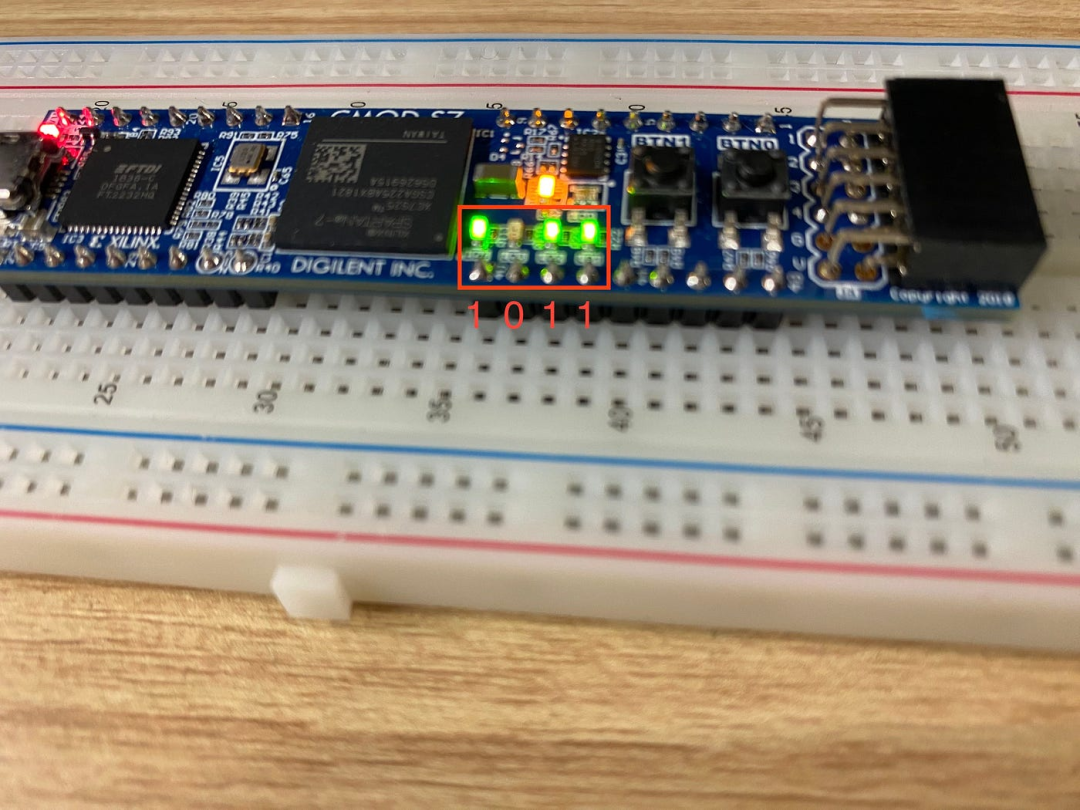

这个程序以二进制格式输出随机数,用LED灯显示,范围从0 ~ 15。下图显示为1011,即十进制的11。

随机数的一个输出。二进制的1011是十进制的11

随机数的一个输出。二进制的1011是十进制的11

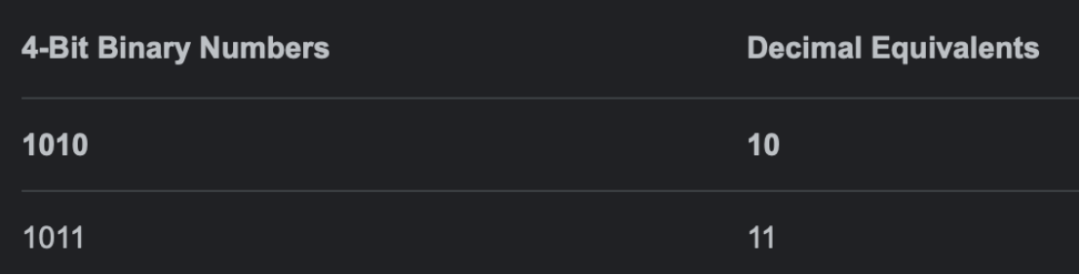

4位二进制数转换为十进制。

4位二进制数转换为十进制。

下面是用Verilog语言实现4位LFSR的源代码。

我们定义了一个名为“DELAY”的常量,其十进制值为12000000,以匹配默认时钟运行在12 MHz

clog2(12000000)=24

// 因为默认时钟运行在12 MHz

`define DELAY 1_200_000_0 // 1秒

module lfsr(

input clk,

output reg [3:0] LED

);

reg [3:0] lfsr_reg;

reg [$clog2(`DELAY) - 1:0] counter = 0;

wire feedback;

assign feedback = ~(lfsr_reg[3] ^ lfsr_reg[2]);

always @(posedge clk)

begin

if ( counter == `DELAY - 1 )

begin

counter <= 0; // 复位计数器

lfsr_reg <= {lfsr_reg[2:0], feedback}; // 更新LFSR // 反馈位在第3和第2位,向左移位

LED = lfsr_reg;

end

else

counter <= counter + 1; // 增加计数器

end

Cmod-S7–25-Master.xdc的示例内容,其中定义了设计约束,如引脚分配、时钟约束和I/O时序参数,这些参数在实现阶段使用。

## This file is a general .xdc for the Cmod S7-25 Rev. B

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## 12 MHz System Clock

set_property -dict { PACKAGE_PIN M9 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L13P_T2_MRCC_14 Sch=gclk

create_clock -add -name sys_clk_pin -period 83.33 -waveform {0 41.66} [get_ports { clk }];

## 4 LEDs

set_property -dict { PACKAGE_PIN E2 IOSTANDARD LVCMOS33 } [get_ports { LED[0] }]; #IO_L8P_T1_34 Sch=led[1]

set_property -dict { PACKAGE_PIN K1 IOSTANDARD LVCMOS33 } [get_ports { LED[1] }]; #IO_L16P_T2_34 Sch=led[2]

set_property -dict { PACKAGE_PIN J1 IOSTANDARD LVCMOS33 } [get_ports { LED[2] }]; #IO_L16N_T2_34 Sch=led[3]

set_property -dict { PACKAGE_PIN E1 IOSTANDARD LVCMOS33 } [get_ports { LED[3] }]; #IO_L8N_T1_34 Sch=led[4]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

2、演示

3 、结论

从综合报告中可以看出,这个程序只占用了FPGA中0.05%的LUT滑块。我们可以在这个CMOD S7中实现更多有趣的功能,充分利用资源。

来源: 本文转载自Java学研大本营公众号

-

【assingle分享】labview随机数发生器2011-04-07 0

-

【总结】LabVIEW随机数发生器2015-01-30 0

-

怎么设计基于USB和FPGA的随机数发生器验证平台?2019-08-27 0

-

请问随机数发生器的主要特性和功能以及如何操作?2020-11-13 0

-

随机数发生器的相关资料分享2022-02-14 0

-

学习笔记 | 基于FPGA的伪随机数发生器(附代码)2023-04-21 0

-

用振荡器采样随机数发生器保证网络SoC设计加密算法的安全性2009-12-26 1080

-

基于FPGA的真随机数发生器设计2011-05-30 1265

-

真随机数发生器的容差分析2011-06-10 1079

-

利用FPGA的自身特性实现随机数发生器2017-02-11 13154

-

PIC32系列参考手册之加密引擎和随机数发生器(RNG)2018-06-05 1262

-

基于FPGA的伪随机数发生器设计方案2021-06-28 4706

-

【STM32】随机数发生器详解2021-12-08 884

-

FPGA的伪随机数发生器学习介绍2023-09-12 1571

-

基于多级反馈环形振荡器的真随机数发生器设计2023-09-14 344

全部0条评论

快来发表一下你的评论吧 !