英伟达AI加速器新蓝图:集成硅光子I/O,3D垂直堆叠 DRAM 内存

电子说

1.3w人已加入

描述

来源:TECHPOWERUP

2024 IEEE IEDM 会议目前正在美国加州旧金山举行。据分析师 Ian Cutress 在其社交平台上发布的动态,英伟达在本次学术会议上分享了有关未来 AI 加速器设计的愿景。

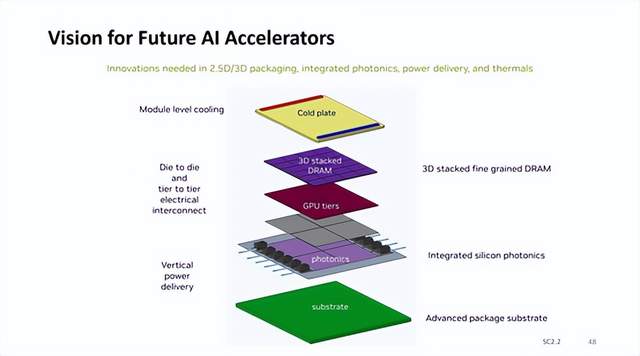

英伟达认为未来整个 AI 加速器复合体将位于大面积先进封装基板之上,采用垂直供电,集成硅光子 I/O 器件,GPU 采用多模块设计,3D 垂直堆叠 DRAM 内存,并在模块内直接整合冷板。

在英伟达给出的模型中,每个 AI 加速器复合体包含 4 个 GPU 模块,每个 GPU 模块与 6 个小型 DRAM 内存模块垂直连接并与 3 组硅光子 I/O 器件配对。

硅光子 I/O 可实现超越现有电气 I/O 的带宽与能效表现,是目前先进工艺的重要发展方向;3D 垂直堆叠的 DRAM 内存较目前的 2.5D HBM 方案拥有更低信号传输距离,有益于 I/O 引脚的增加和每引脚速率的提升;垂直集成更多器件导致发热提升,模块整合冷板可提升解热能力。

热管理是另一个关键考虑因素。多层 GPU 设计带来了复杂的冷却挑战,而目前的技术无法充分解决这一问题。NVIDIA 承认,在将 DRAM 堆叠在逻辑上的概念成为现实之前,材料科学必须取得重大进展。该公司正在探索创新解决方案,包括实施芯片内冷却系统,例如使用专用冷板进行模块级冷却。这种设计的商业化还需要一段时间,Ian Cutress 博士等分析师预测,采用这种技术的产品可能会在 2028-2030 年左右上市。

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

进一步解读英伟达 Blackwell 架构、NVlink及GB200 超级芯片2024-05-13 0

-

找不到3d硬件加速器怎么办2019-08-21 0

-

英伟达DPU的过“芯”之处2022-03-29 0

-

TSMC 和 Cadence 合作开发3D-IC参考流程以实现真正的3D堆叠2013-09-26 1442

-

为了延长DRAM存储器寿命 必须短时间内采用3D DRAM2017-03-17 3072

-

基于Hadoop的I/O硬件压缩加速器2017-11-27 750

-

英伟达再出新研究成果 可以渲染合成交互式3D环境的AI技术2018-12-12 964

-

硅3D集成技术解决方案在传感器应用中的主要挑战2020-01-16 1016

-

硅3D集成技术全面解析2020-04-10 2600

-

浅谈400层以上堆叠的3D NAND的技术2023-06-15 2209

-

技术资讯 I 3D-IC 中 硅通孔TSV 的设计与制造2022-11-17 1461

-

英伟达、AMD在2024年继续全力冲刺人工智能加速器市场2024-01-08 1214

-

三星2025年后将首家进入3D DRAM内存时代2024-04-01 591

-

SK海力士5层堆叠3D DRAM制造良率已达56.1%2024-06-27 632

-

英伟达加速认证三星AI内存芯片2024-11-25 243

全部0条评论

快来发表一下你的评论吧 !