ad7656中文资料汇总(ad7656引脚图及功能_内部结构及应用威廉希尔官方网站 )

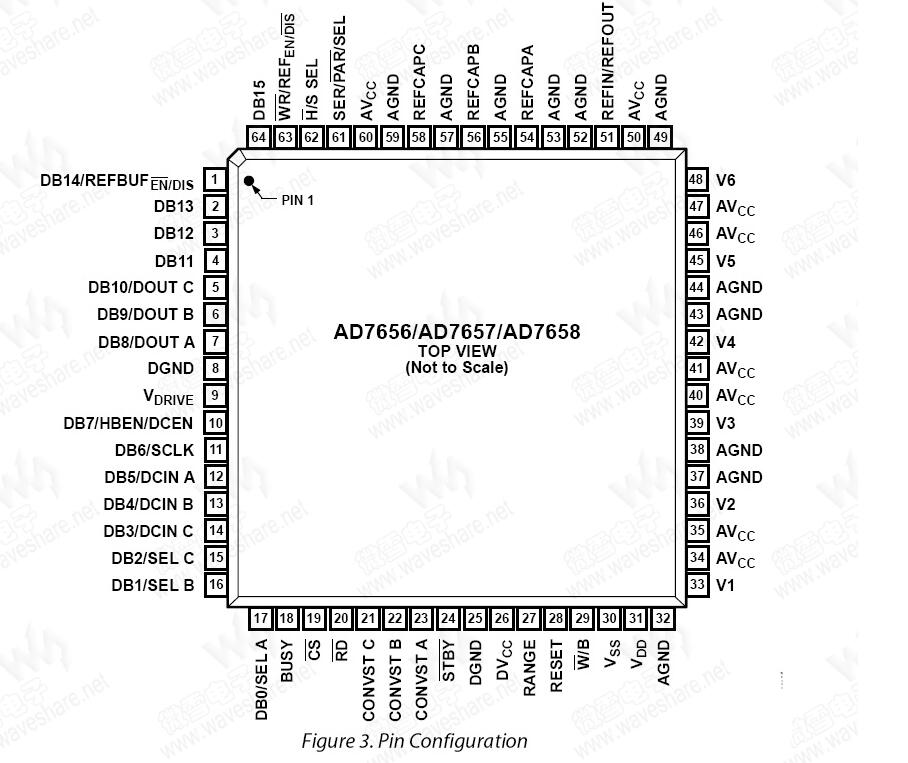

芯片引脚图

描述

AD7656性能概述

AD7656具有最大4 LSBS INL和每通道达250kSPS的采样率,并且在片内包含一个2.5V内部基准电压源和基准缓冲器。该器件仅有典型值160mW的功耗,比最接近的同类双极性输入ADC的功耗降低了60% 。

AD7656包含一个低噪声、宽带采样保持放大器(T/H),以便处理输入频率高达8MHz的信号。该AD7656还具有高速并行和串行接口,可以与微处理器(mcu)或数字信号处理器(DSP)连接。AD7656在串行接口方式下,能提供一个菊花链连接方式,以便把多个ADC连接到一个串行接口上。

AD7656采用具有ADI专利技术的iCMOS(工业CMOS)工艺。iCMOS 工艺是一种高压半导体工艺与亚微米CMOS(互补金属氧化物半导体)和互补双极型工艺相结合的制造上艺。它能开发出承受30V电源电压的多种高性能模拟IC,并且其小封装尺寸是任何其他同类高电压IC都未曾达到的。与使用传统CMOS工艺的模拟IC不同,iCMOS器件能承受高电源电压,同时提高性能、显著降低功耗和缩小封装尺寸。AD7656是使用该种工艺设计制造的产品,所以非常适合在继电保护、电机控制等工业领域使用。

AD7656特性

6个独立16位ADC

6个真双极性模拟输入

引脚/软件可选范围:±10V、±5V

高吞吐量:每通道250kSPS

额定电压(AVcc):4.75V至5.25V

低功耗:160mW(250kSPS,5V电源)

宽输入带宽:86dB信噪比(SNR)(输入频率50kHz时)

片内基准电压及缓冲

并行和串行接口

高速串行接口:SPI/QSPI/µWire/DSP兼容

无流水线延迟

待机模式:最大5µA

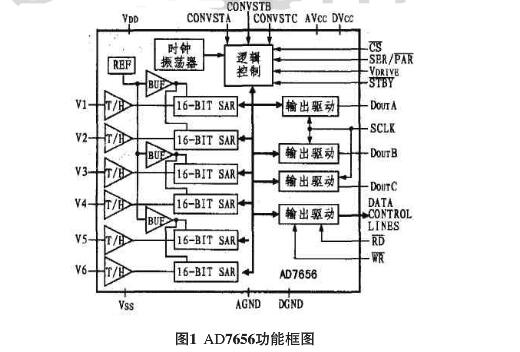

ad7656内部框图

AD7656工作原理

AD7656足具有独立的六通道逐次逼近型(SAR)的模数转换器,转换处理和数据的精度是通过CONVST信号和一个内部晶振控制的。3个CONVST管脚允许3路ADC对独立同步采样。当3个CONVST管脚连接到一起时,就可以进行6个通道的同步采样。 AD7656具有高速的并行和串行接口,允许其与Microprocessors和DSP进行接口。当使用串行接口模式时,AD7656具有的菊花链特性允许多个ADC和一个串行接口连接。由于在电力继电保护产品中以并行接口连接设计为主,所以下面将以并行接口的连接方式介绍其工作原理。

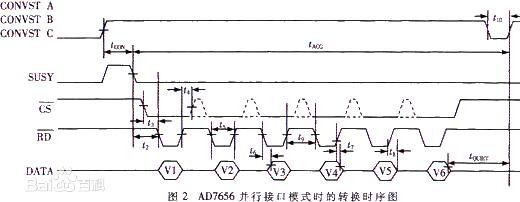

AD7656在并行接口方式下的工作时序图

首先,通过MCU或DSP控制CONVST管脚启动转换,并保持该信号为高电平。AD7656启动转换信号后会自动输出BUSY信号,BUSY信号下降沿时,代表转换已经全部完成。

此时,AD7656内部的6个寄存器中已经保存了转换的数据,然后通过控制片选CS和读RD信号依次顺序读出6个通道AD转换值。 读出AD转换值后,改变CONVST为低电平信号。注意在设计时,一定要保证AD转换过程中CONVST管脚保持高电平。

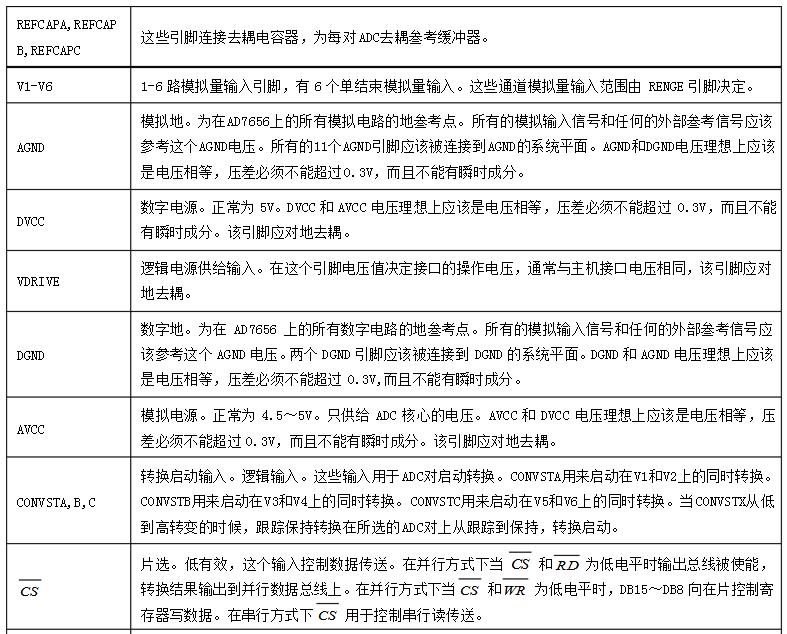

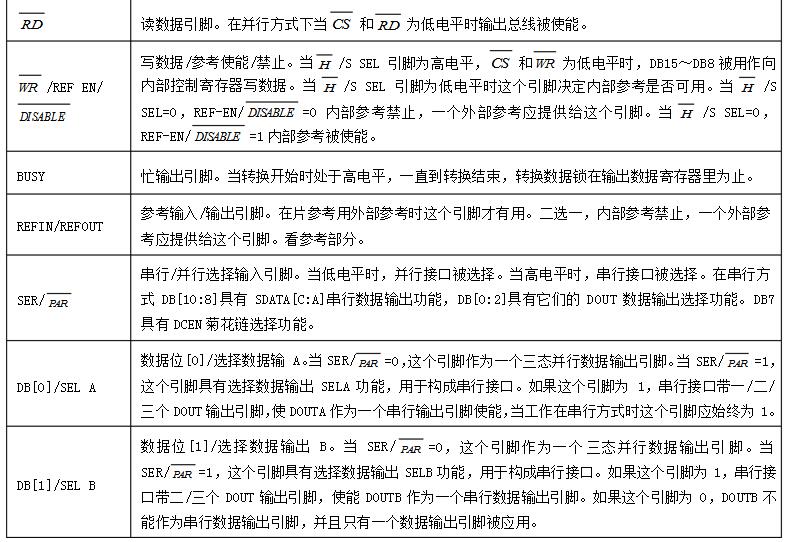

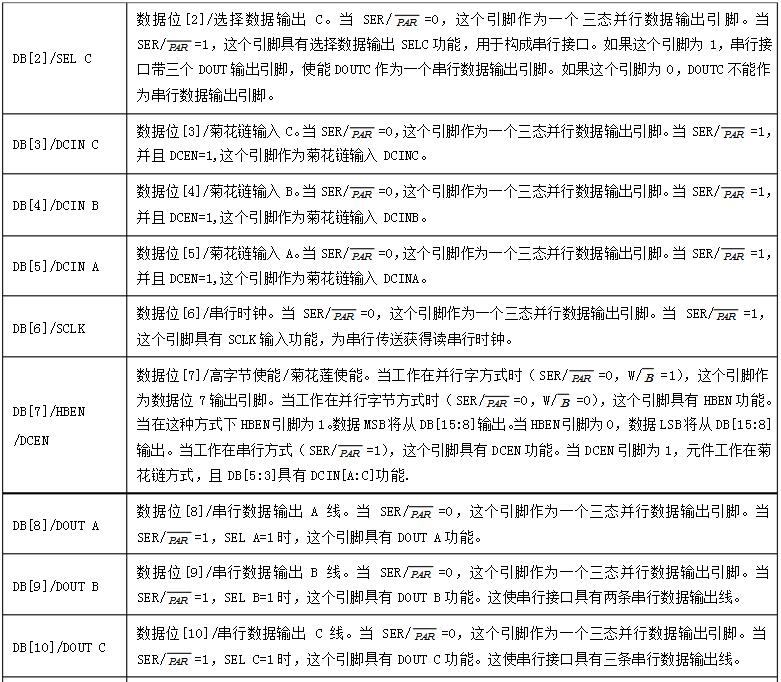

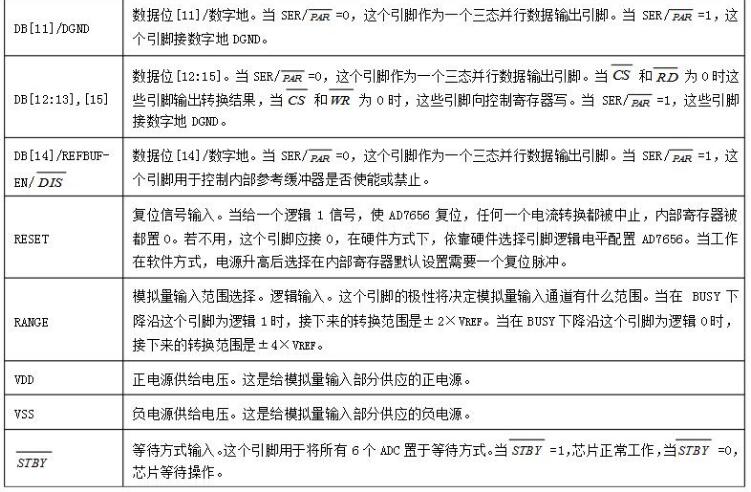

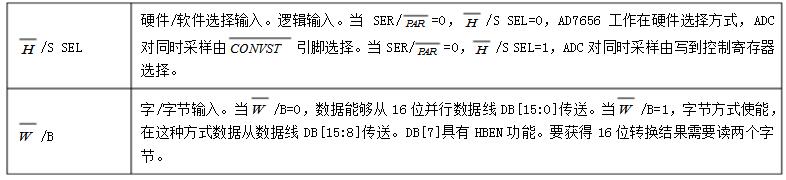

AD7656引脚图及功能

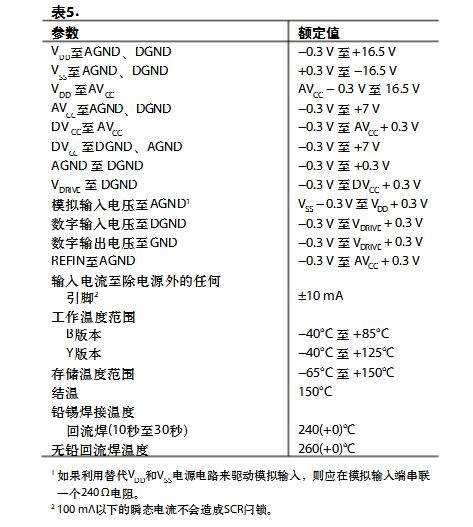

ad7656绝对最大值

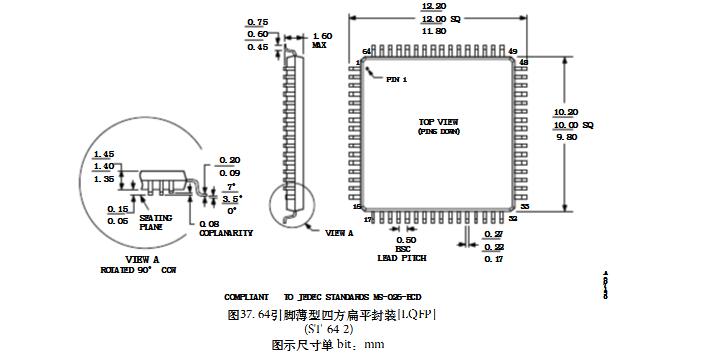

ad7656外形尺寸

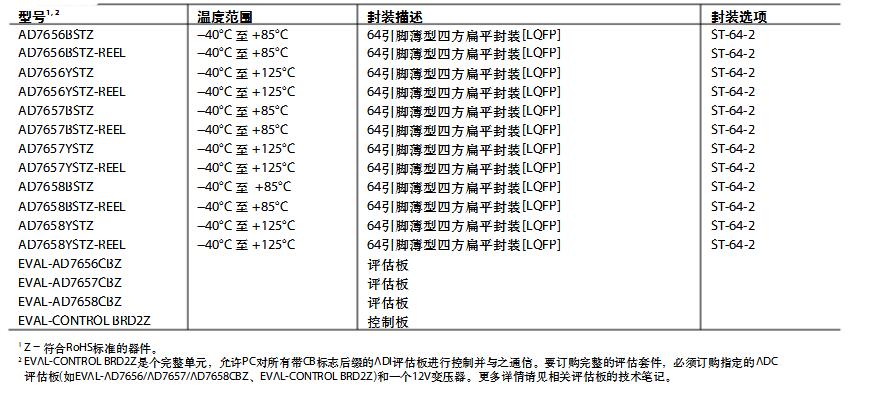

ad7656订购指南

四款ad7656应用威廉希尔官方网站

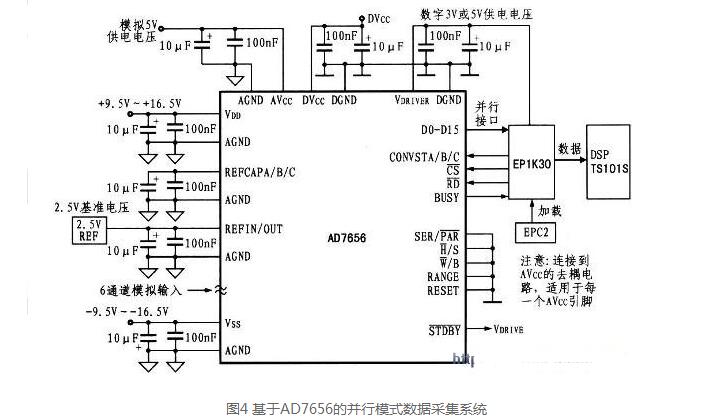

应用威廉希尔官方网站 一:

图4所示是AD7656在并行接口状态下的外围威廉希尔官方网站 连接。其中的DVcc和AVcc分别是数字电压端和模拟电压端,它们在接入前要经过1个去耦威廉希尔官方网站 ,如图4所示,每个供电电压输入引脚都要连接1个去耦威廉希尔官方网站 ,该威廉希尔官方网站 由1只10μF和1只100nF的电容器组成。VDD、Vss和VDRIVE同样要连接去耦威廉希尔官方网站 。

AD7656的输出接到FPGA中进行数字信号的滤波处理,然后再送入数字信号处理器(DSP)进行处理。用FPGA控制引脚CONVSTA/B/C、 RD和CS的状态,可以用编程的方法或硬件连接的方式来实现。系统中的FPGA是ALTERA公司的EP1K30,DSP选用ADI公司的TS101S。此系统的外围威廉希尔官方网站 比较简单,比较容易实现,具有真正的高速、高性能数字信号采集功能。

应用威廉希尔官方网站 二:

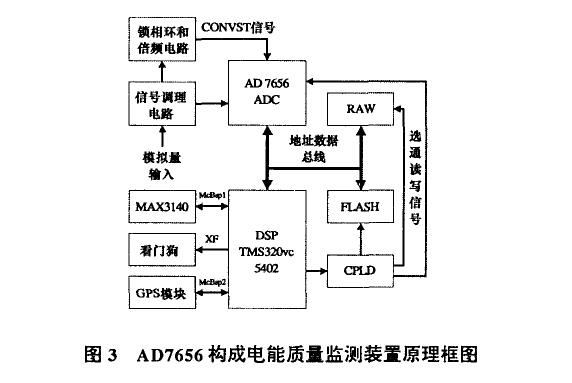

电能质量测控系统采用16位高功能、低功耗的DSP芯片TMS320vc5402作为CPU,具有先进的多总线结构,40位AIU,数据/程序寻址空间1M*16bit,内置4K*16bitP/DROM和16K*16bitDARAM,工作频率可达到IOOMIPS。该处理器是整个监测系统的控制核心,主要完成系统的通讯接口,负责系统中各个威廉希尔官方网站 的协调管理以及计算结果的预处理。其特点是任务多,各个任务之间的协调较为复杂。DSP芯片接收数据采集系统送来的数字信号,并对其进行分析和计算,以实现各种算法,完成电压、电流、功率、功率因数、频率及各项电能指标的计算和分析。同时通过开关量输入输出通道实现各种控制模式。系统扩展高精度CPID实现对外围各种设备的控制;扩展1片AM28F010作为外部程序存储器和数据存储器;与上位机通讯采用RS一485协议,为此内部集成一个通用的UART和全功能收发器MAX3140。

电能质量监测需要对电压、电流、有功功率、无功功率、频率等基本参数进行实时监测,并对电力系统的谐波、三相电压不平衡度、电压闪变等指标进行分析。为了保证实时性,系统采用2片高速6通道同时转换的A/D转换器AD7656,同步采集三相电压信号和电流信号,简化了系统的硬件设计和软件程序设计,为DSP及时准确地完成繁多的系统任务和复杂的算法奠定了基础。A/D转换模块中,A/D采集要求DSP在接受到指示A/D转换已完成的信号后从A/D中读取转换结果,因此需要建立两个硬件中断,一个是A/D中断请求,BUSY引脚变低指示所有转换已完成,通知DSP可从片内的寄存器读转换结果;另一个是DSP接收A/D数据中断,如CS和RD低脉冲即为DSP从AD7656中读转换结果,在RD的上升沿将数据读入DSP,建立两个与硬件中断相对应的软件中断SWI,建立配置A/D属性的任务。系统的硬件结构框图如图3。

应用威廉希尔官方网站 三:

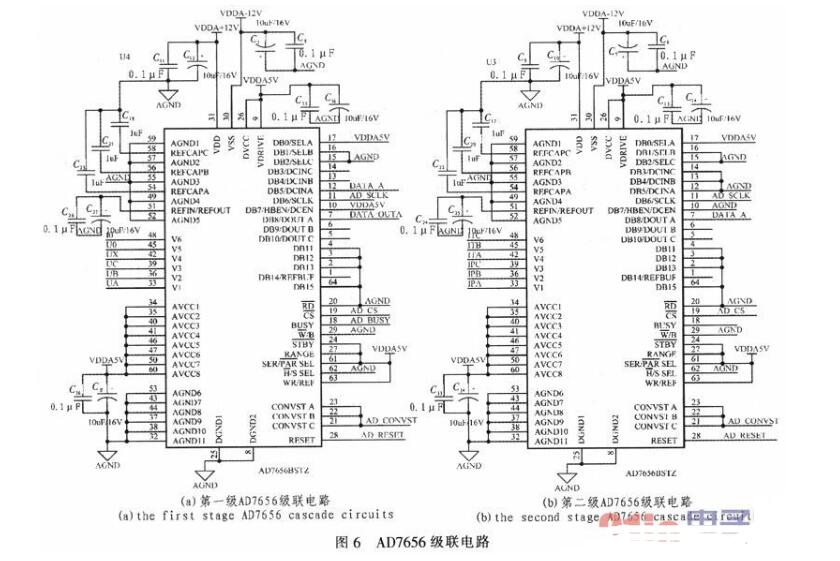

如图6所示为AD7656级联威廉希尔官方网站 图,锁相环的输出信号PLL-CONVST控制两块AD7656的21、22、23管脚,同时启动12路采集;CPU作为主机为AD7656的11管脚(AD—SCLK)提供时钟信号。CPU从图6(a)的管脚7(DATA—OUTA)通过SPI读取数据;图6(a)的12管脚与图6(b)的管脚7连接,实现两块AD7656的级联;通过判断AD7656的18管脚(AD—BUSY)来提醒CPU读取转换数据。

应用威廉希尔官方网站 四:

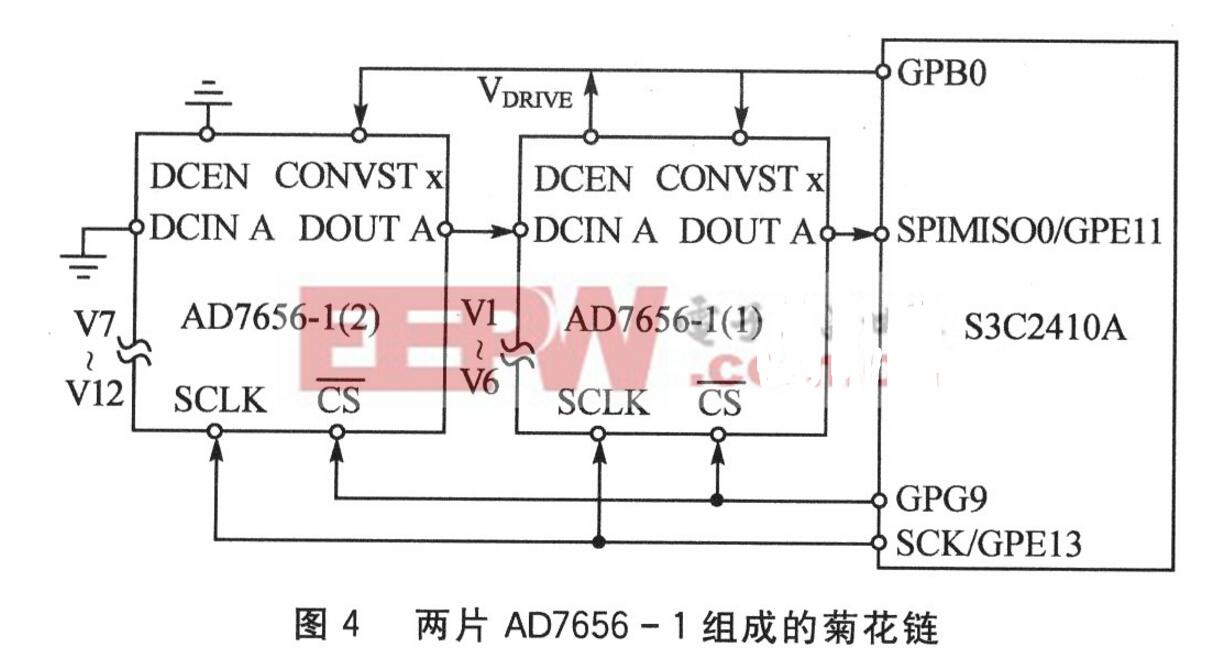

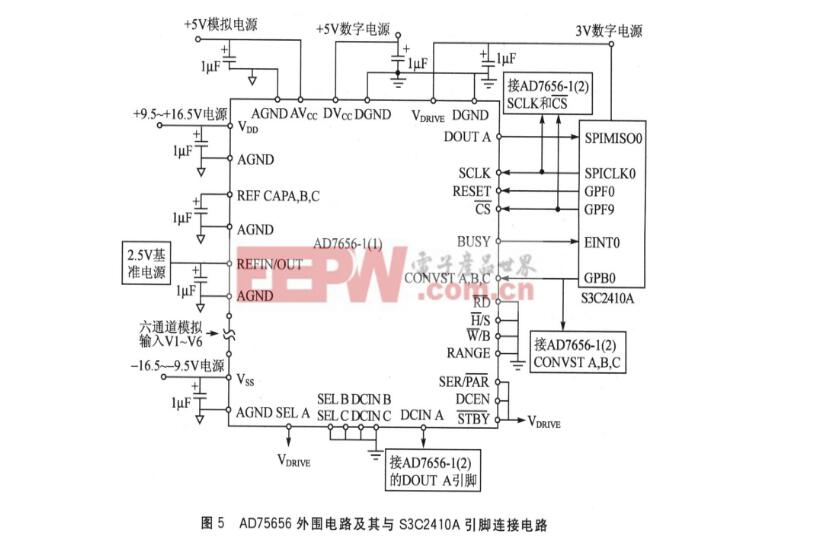

采用2片AD7656-1配置成菊花链,可实现12通道同时采样,数据通过DOUTA[]输出,S3C2410A用同步串行接[10(SPIO)接收数据,如图4所示。S3C2410A的GPEII弓|脚实现片上同步串行接[1SPIO的MISO功能,GPEI3(SCK)3|脚实现SPIO接C的同步时钟输出,GPFO弓|脚配置为中断EINTO输入并与AD7656-1(1)的BUSY脚相连;GPBO设置为PWM输出,GPG9弓|脚没置为通用输出口,分别作为AD7656-1(1)和AD7656-1(2)的CONVST和CS的控制信号输入。AD7656-1连接外围威廉希尔官方网站 时,必须对关键弓|脚进行必要的设置:AD7656-1(1)、AD7656-1(2)的DVCC、AVCC、VDRIVE、REFIN/OUT和VSS|脚须并联一个1uF的去耦电容;为了与S3C2410A的3.3V的接[匹配,VDRIVE接+3V电源;STBY接VDRIVE,选择正常模式;RANGE接地表示选择输入范围士10V;H/s接数字地选择为硬件配置;SER/PAR接VDRIVE,RD接数字地,选择为串行模式。AD7656-1(1)的DCEN接VDRIVE,配置为菊花链模式,且SELA接VDRIVE,SELB、C,DCINA、B、C接数字地;AD7656-1(2)的DCEN接数字地,配置为排菊花链模式,且SELA接VDRIVE,SELB、C,DCINB、C接数字地。具体配置如图所示。

ad7656相关文章:ad7656应用威廉希尔官方网站 图大全(四款ad7656外围威廉希尔官方网站 /电能质量监测/级联威廉希尔官方网站 )

-

AD7656的工作原理2011-01-02 0

-

AD7656在电力继电保护产品中的应用2011-01-02 0

-

AD7656的模拟输入接口2018-10-09 0

-

请问AD7656的控制引脚模拟地怎么接2018-11-21 0

-

AD7656的知识点,总结的太棒了2021-04-14 0

-

AD7656的工作原理及系统构成,使用AD7656有什么注意事项?2021-04-20 0

-

AD7656 pdf datasheet2008-08-14 793

-

ad7656的应用介绍2009-09-30 917

-

AD7656的原理及在继电保护产品中的应用2009-10-17 3285

-

AD7656在电力系统测控中的应用2011-06-13 1152

-

ad7656应用威廉希尔官方网站 图大全(四款ad7656外围威廉希尔官方网站 /电能质量监测/级联威廉希尔官方网站 )2018-05-16 7458

-

一文解析DSP与AD7656的高速AD采集威廉希尔官方网站2018-05-18 21676

-

AD7656参考代码2021-03-18 636

-

AD7656原理图2021-04-30 712

-

ad7656串行输出代码2023-12-28 938

全部0条评论

快来发表一下你的评论吧 !