射频定时发送器的基本功能与设计方案介绍

描述

引言

射频定时发送器是射频控制模块中的一个重要组成部分,用于产生需要定时发送的射频控制信号:AD_ON(模数转换信号)、DA_ON(数模转换信号)、APC(自动功率控制信号)、AGC(自动增益控制信号)和AFC(自动频率控制信号),再通过选择两个SPI接口RF_SPI和AD_SPI把控制信号定时地传送到射频发送模块。射频定时发送器需要完成的四种基本功能分别是:定时发送、竞争发送、数据采样时钟分频,以及APC_burst模式,如图1所示,本文将详细阐述这些基本功能模块的设计原理。

图1 射频定时发送器功能结构图

定时发送模块

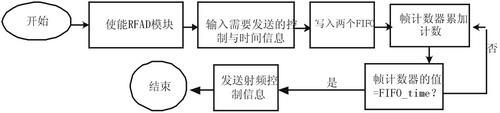

射频定时发送器的主要功能就是定时传输射频控制信息,为了满足此功能,需要在模块中设计两个FIFO:DATA FIFO用于存储射频控制信息;TIME FIFO用于存储时间信息。模块中设定当系统帧计数器与TIME FIFO中存储的某一时间相同时,就把与这个时间对应的射频控制信息发送出去。因此还需设计一个模块,判断当帧计数器的值等于FIFO_time(FIFO中存储的时间)时,产生使能信号(read_en, fifo_read_en, time_int)发送信息,工作流程如图2所示。

图2 定时发送射频控制信息设计流程图

FIFO

该模块中将设计两个FIFO,它们将需要发送的射频控制信息及其发送时间缓存起来,设计用FIFO进行存储的目的是将这两种信息一一对应起来,避免发送的时候出错。

define data_fifo

module data_fifo (rst_,clk,we_i,rd_i, addwr_i,addrd_i,fifo_data_i,fifo_data_o);

1) 首先定义该模块的信号线:输入信号为rst_ (复位信号)、clk(标准时钟)、 we_i(写信号)、 rd_i(读信号)、addwr_i[4:0](写FIFO地址)、 addrd_i[4:0](读FIFO地址)和fifo_data_i[11:0](写入FIFO的值);输出信号为fifo_data_o[11:0] (FIFO输出值)。

2) 再定义一个宽度为12位、深度为32的FIFO:reg [11:0] register_fifo[0:31];

3) 设计写FIFO的情况:以clk为参考时钟,首先判断复位信号,当复位信号为低时,对FIFO进行复位:if(!rst_) register_fifo[0.。..。.31] 《= 12’b0;当rst_不为低且we_i为高时,则对FIFO进行写操作:if(we_i == 1’b1) register_fifo[addwr_i] 《= fifo_data_i;

4) 设计读FIFO的情况:同样以clk为参考时钟,先判断复位信号,当复位信号为低时,对fifo_data_o进行复位:if(!rst_) fifo_data_o《= 12’b0;当rst_不为低且rd_i为高时,则对FIFO进行读操作:if(rd_i == 1’b1) fifo_data_o 《= regsiter_fifo[addrd_i];

使能信号及中断产生模块

FIFO读/写使能信号是由外部模块驱动的,因此需要设计一个模块用于产生控制FIFO的读/写信号,并且该模块还需产生时间中断信号用于使能发送器。

define transfer time

module time_count(rst_,clk,fifo _time,framc,read_en,fifo_read _en,time_int);

1) 首先定义该模块的信号线:输入信号为rst_、clk、 fifo_time[15:0](FIFO中存储的时间信息)、framc(帧计数器值);输出信号为read_en(FIFO地址累加使能信号)、 fifo_read_en(读FIFO值使能信号)、time_int(时间中断信号);再定义一个reg [1:0] time_int_delay,用于存储time_int在上一个时钟的信息,如time_int_delay[0] 《= time_int; time_int_delay[1] 《= time_int_delay[0];

2) 定义fifo_read_en信号在time_int被拉高后延迟一个clk拉高,再延迟一个clk拉低,即assign fifo_read_en = time_int |(time_int_delay[0]);定义read_en信号在time_int被拉高后延迟两个clk后拉高,再延迟一个clk拉低,即 assgin read_en = time_int_delay[0] |(time_int_delay[1])。这样做的目的是控制在当前clk的上升沿到来时取出FIFO中当前地址的值,然后在下一个clk的上升沿立即计算出下一次取值的地址,这样就能保证在每一次取值之前其所在的位置已经计算完成,避免了取值出错的情况。

3) 最后定义如何产生time_int信号。time_int产生的条件是:当fifo_time中存储的时间信息等于framc时,time_int被拉高,即被使能,if(fifo_time== framc ) time_int 《= 1‘b1;

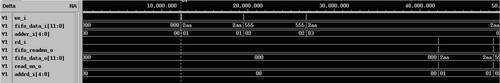

FIFO读写操作的仿真结果如图3所示,对FIFO的读/写操作分别由we_i和rd_i(fifo_read_en)控制,而计算读FIFO的地址由read_en控制,这样就能保证在每次取FIFO值之前其所在地址已经被计算完成。

图3 FIFO读/写操作仿真图

竞争发送模块

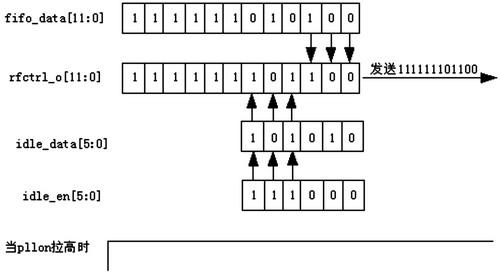

芯片在空闲情况下,可能会有空闲状态的射频控制信息(idle_data)需要发送,当芯片唤醒后则应优先发送该信息。但当芯片唤醒后产生的射频控制信息fifo_data与idle_data在同一时刻发送时,就会出现竞争发送的情况。因此,在设计该模块时限定当idle_en(空闲使能信号)与pllon(pll时钟使能信号)同时拉高时,发送idle_data中的相应比特来取代fifo_data中的相应比特,如图4所示。

图4 射频定时发送器在空闲情况下的工作流程

transfer idle_data and fifo_data:

module idle_time(fifo_ data,pllon,idle_en,idle_data,rfctrl_o);

1) 定义该模块的信号线:输入信号为fifo_data[11:0](FIFO中存储的射频控制信息)、idle_data (空闲时需发送的射频控制信息)、idle_en、pllon;输出信号为rfctrl_o(最后输出的射频控制信息)。

2) 下面对需发送的控制信息进行逻辑组合。其敏感电平是pllon、fifo_data、idle_data和idle_en,即当上述电平中任意一个发生变化时,就执行下面的语句:

always @(pllon or fifo_data or idle_data or idle_en)//组合逻辑威廉希尔官方网站

begin

rfctrl_o[0] = (idle_en[0])?idle_ data[0]:fifo_data[0];

rfctrl_o[1] = (idle_en[1])?idle_ data[1]:fifo_data[1];

rfctrl_o[2] = (idle_en[2])?idle_ data[2]:fifo_data[2];

rfctrl_o[3] = (idle_en[3])?idle_ data[3]:fifo_data[3];

rfctrl_o[4] = (idle_en[4])?idle_ data[4]:fifo_data[4];

。..。..。..。..。.. 。..。..。..。..。..。. 。..。..。..。..。.

end

竞争发送的仿真结果如图5所示:在pllon没有被拉高的情况下,rfctrl_o发送的就是fifo_data的值,只有当pllon被拉高的条件下才会有竞争发送的情况。

数据采样时钟分频模块

为了数据发送同步,射频定时发送器输出数据的频率应与外接模块保持一致,射频定时发送器采样发送数据的时钟是系统时钟的分频时钟。因此,产生分频时钟和采样使能信号是该模块设计的关键所在,并要求每次对发送数据的采样都应发生在分频时钟的上升沿。

generator ad_clk and send ad_sdatao:

module drv_clk(rst_,clk,frq_ drv,ad_sclk,spi_en,rfctrl_data,ad_datao);

1) 定义该模块的信号线:输入信号为rst_、 clk、 frq_drv(分频系数)、rfctrl_data(射频控制信息);输出信号为ad_sclk(分频时钟)、ad_sdatao(发送数据)。

2) 以clk为基准时钟,定义一个reg[3:0] count计数器对clk的上升沿进行计数。当count=frq_drv-1时,ad_sclk进行反转并对count清零,这样就产生了分频时钟。

3) 该模块设计要求每次对发送数据的采样都应发生在分频时钟的上升沿。但为了避免产生异步,对数据进行采样时不能以产生的ad_sclk为标准,应仍以clk为基准时钟。即在每8个clk时钟的上升沿发送1位的rfctrl_data,并由高位到低位发送,这样采样时就不会出现毛刺,能做到较好的同步。

always @(posedge clk or negedge rst_)

begin

count 《= count+1

if(count == 2*frq_drv-1)

begin

ad_sdatao 《= rfctrl_data[11]; //每次发送rfctrl_data的最高bit

rfctrl_data[11:0] 《= {rfctrl_data[10:0], 1’b0};

//然后rfctrl_data[11:0]左移一位,去除已发送的bit

end

end

这种方式能确保在每一个ad_sclk的上升沿对发送数据的数据进行采样,避免了产生毛刺。

图5 竞争发送仿真图

burst发送模式设计

为了使发送功率更加稳定,射频定时发送器中设计了一种burst模式,即把一次性需要发送的功率分为几步发送出去,并规定了每步发送的功率值=step_value*para(每步值×增益),这样就可以避免在发送功率控制信息时产生突激。

burst step design:

module burst(rst_,clk,apc_ flag_i,step0.。...step11,para,ad_s datao,apc_burst_en,apc_burstout);

1) 定义该模块的信号线:输入信号为rst_、 clk、 apc_flag_i(apc标志信号)、step0.。...step11 (每步需发送的功率值)、para(每步增益)、apc_burst_en(burst模式使能信号);输出信号为apc_burstout(每步最终发送的功率)、ad_sdatao(发送数据)。

2) 定义assign apc_burstout = step_value*para,设置step_count记录目前发送的步数,并根据step_count的信息,用step_value存储当前步数的值。

always @(posedge clk or negedge rst_)

begin

case(step_count)

2‘b00: step_value[11:0]《= step0[11:0];

2’b01: step_value[11:0]《= step1[11:0];

2‘b10: step_value[11:0]《= step2[11:0];

。..。..。..。..。..。.

endcase

end

3) 最后定义当每次apc_burst_en使能时,step_count累加。

仿真结果如图6所示:当apc_flag_i拉高时,射频控制信息开始从0步到11步分步发送;当apc_flag_i拉低时,再从第12步到第1步发送。

图6 APC在burst模式下发送数据的仿真结果时序图

结语

作为射频控制模块中的重要部分,射频定时发送器能够定时发送射频控制信息,并能根据实际情况调整发送模式。本文对该模块最重要的四大功能模块,即定时发送模块、竞争发送模块、分频采样时钟模块以及burst模式发送模块的设计方案作了基本介绍,希望对芯片设计人员有所帮助。

-

视频矩阵切换器的基本功能与介绍2018-02-26 0

-

物联网的最基本功能是什么?2020-06-16 0

-

MCU的基本功能及程序编写2021-01-12 0

-

MCU的基本功能2021-02-05 0

-

分享一种低成本HART发送器的设计方案2021-04-09 0

-

智能合约的基本功能是什么2021-07-12 0

-

STM32CUBEMX基本功能如何配置?2021-11-23 0

-

串口的基本配置和基本功能是什么?2021-12-10 0

-

reertos基本功能包括什么2021-12-27 0

-

PLC的基本功能与特点解析2022-02-16 0

-

高性能射频调制器促成多载波通信发送器设计2006-05-07 553

-

钽电容器的基本功能与结构2023-12-08 978

-

555定时器的基本功能 555定时器的工作原理及其应用2024-01-18 15202

-

校正射频发送器的外部和内部射频功率衰减2024-09-03 71

全部0条评论

快来发表一下你的评论吧 !