一种精简FPGA编程威廉希尔官方网站 的实现方案

描述

1 、引言

便携式、小型的仪表和设备是一个非常重要的应用领域,在未来一段时间内会有比较大的市场。而FPGA等现场可编程器件也是正在兴起与普及的一种器件,把FPGA更好地运用到上述仪表和设备中,可以减少这些仪器、设备的开发周期,大幅度提升这些仪器的性能,减少总成本和体积等。

在许多应用场合,如大型设备中的板卡,比较适合采用标准的FPGA编程威廉希尔官方网站 。但是对于便携式设备的应用场合,采用标准威廉希尔官方网站 联系FPGA与CPU需要消耗的资源太多。许多DSP芯片只有2个通用I/O引脚,所以如果能只使用1~2个引脚就完成FPGA编程功能,意义将非常重大。

2 、标准的FPGA编程威廉希尔官方网站

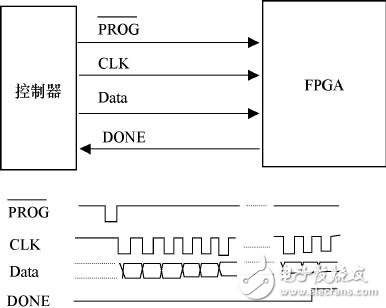

以Xilinx的Spartan系列FPGA为例,图1是一个标准的编程威廉希尔官方网站 。威廉希尔官方网站 中控制器使用了4条控制信号线PROG,CLK,Data,DONE。首先Prog信号控制FPGA的初始化,一个Prog信号的低电平使FPGA进入编程状态,在编程过程及以后的运行过程中,Prog信号保持高电平;在编程过程中,Data信号与CLK信号配合,在每个Clk信号的上升沿,FPGA锁定/读取一个Data信号,如此循环,直到控制器将需要编程的程序全部送到FPGA中;当FPGA正确接收到编程程序以后,就会产生一个DONE信号,通知控制器一切完毕。

该威廉希尔官方网站 是Xilinx公司推荐的一个FPGA的标准威廉希尔官方网站 ,对于许多常规应用场合,它还是比较合适的,但是对于手持式仪表等尺寸非常小的设备,由于控制器本身只有1~2个I/O控制线,而上述标准威廉希尔官方网站 占用4个I/O口,就有可能无法应用。

3 、精简的FPGA编程方法

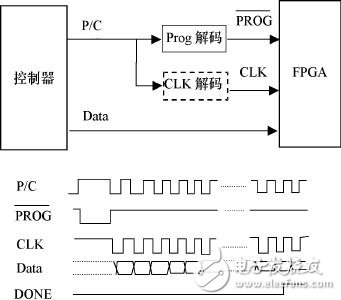

本文给出了一种精简的FPGA编程威廉希尔官方网站 如图2所示。控制器的I/O控制信号线包括P/C和Data。P/C控制信号产生图2中所示的波形,经过Prog解码威廉希尔官方网站 (如图4所示)得到Prog信号,经过CLK解码威廉希尔官方网站 (在本例中也可以不经过),得到CLK信号,它们与Data一起组成完整的FPGA控制信号,完成对FPGA的编程控制。

图1 通常的FPGA下载威廉希尔官方网站

图2 精简的FPGA下载威廉希尔官方网站 之一

该威廉希尔官方网站 只使用2根I/O控制信号线,比标准编程威廉希尔官方网站 要少,利用特殊控制信号的编码与解码,得到完成FPGA的编程工作。

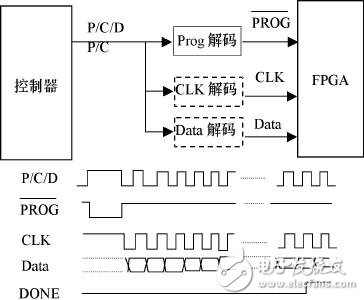

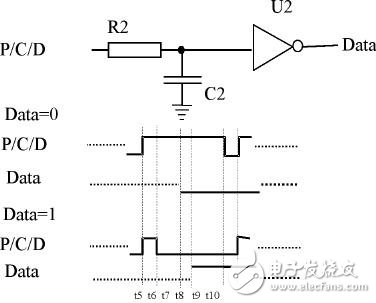

更进一步,也可以只使用一个I/O控制信号线,如图3所示,使用Prog解码威廉希尔官方网站 (如图4所示)、CLK解码威廉希尔官方网站 和Data解码威廉希尔官方网站 (如图5所示),得到FPGA编程所必须的Prog信号、CLK信号和Data信号。该方法比图2所示的威廉希尔官方网站 所需要的控制线还要少。

图3 精简的FPGA下载威廉希尔官方网站 之二

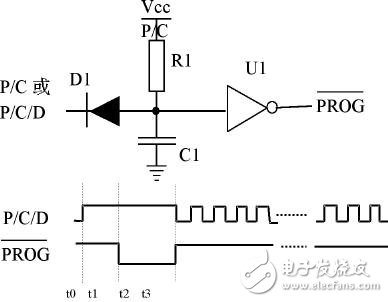

图4 Prog解码威廉希尔官方网站

图5 Data解码威廉希尔官方网站

本方法利用比标准FPGA编程威廉希尔官方网站 更少的I/O控制线,经过解码威廉希尔官方网站 的解码得到FPGA编程所需要的控制信号。对于不同公司的产品,本方法只要稍加变动就可以使用。

4 、应用案例

以Xilinx的Spartan II系列产品为例,图4为Prog控制信号解码威廉希尔官方网站 ,图5为Data信号解码威廉希尔官方网站 。不妨假定CLK信号的周期为Tclk,Prog解码威廉希尔官方网站 中的时间常数为tProg=R1*C1,Data解码威廉希尔官方网站 的时间常数为tData=R2*C2。

Prog控制信号解码威廉希尔官方网站 的原理: P/C信号或P/C/D信号由Prog编码和CLK(Data)编码组成,其中Prog编码是一个周期比较长的高电平,见图4的t2-t0,它大于Prog解码威廉希尔官方网站 的时间常数tProg,CLK(Data)编码是周期比较短的脉冲,小于解码威廉希尔官方网站 的时间常数tProg,所以Prog信号可以被解码得到,而其他不相关信号则被过滤掉。一般可以选择Prog编码周期t2-t0》5tProg,而CLK(Data)编码周期t3-t2《1/5tProg。当FPGA编程结束以后,P/C信号,或者P/C/D信号应当立即复位,否则Prog会出现错误。

Data解码威廉希尔官方网站 的原理可以分成Data=0和Data=1两种情况:

Data=“0时”,当P/C/D信号的前一个数据的上升沿t5结束,并保持一段时间,到达t6后,继续保持高电平,经过大约tData(与先前状态有关),Data控制信号线就会出现低电平,即信号0,为了更加可靠,可以等一段时间,到达时刻t9时P/C/D信号再给出一个负脉冲用于锁定数据。当然负脉冲的宽度应当比较窄,否则Data信号会反转,通常负脉冲宽度t10-t9《1/4tCLK。

Data=“1时”,当P/C/D信号的前一个数据的上升沿t5结束,并保持一段时间,到达t6后,立即进入低电平,经过大约tData(与先前状态有关),Data控制信号线就会出现高电平,即信号1,为了更加可靠,可以等一段时间,到达时刻t10时,P/C/D信号再给出一个上升沿用于锁定数据。

这样Data信号也可以被正确地解码出来。在本例中CLK信号无须专门的解码威廉希尔官方网站 ,P/C/D信号可以直接作为CLK控制信号使用。

本方法经过实验验证,其中R1=10KW,C1=0.1mF, R2=1KW, C2=0.01mF,D1为1N5817,U1/U2为74HC14。当然也可以根据需要进行调整。

5 、结语

FPGA是一种功能非常强大,非常灵活的器件,正在向各种中、高档的应用普及,采用本文提出的精简FPGA编程方法,节省了控制器的I/O线,克服了FPGA在便携式设备中应用的一个瓶颈。文中给出了其基本原理并通过了实验,具有一定的使用价值。

-

一种基于FPGA的UART实现方法设计2019-06-21 0

-

一种基于FPGA的DSU硬件实现方法2019-06-28 0

-

一种基于FPGA和MCU的总线转换方案设计2019-06-28 0

-

一种基于FPGA的可配置FFT IP核实现设计2019-07-03 0

-

求大神分享一种高速突发模式误码测试仪的FPGA实现方案2021-04-29 0

-

求一种精简的FPGA编程方法2021-04-30 0

-

分享一种基于Actel Flash FPGA的高可靠设计方案2021-05-10 0

-

分享一种FPGA的动态配置方案2021-05-27 0

-

分享一种不错的无线语音传输系统设计方案2021-05-31 0

-

用FPGA实现纠错编码的一种方法2011-11-10 906

-

一种基于FPGA的ZigBee物理层发射机的数字基带实现方案_陈2017-03-14 999

-

一种基于FPGA的数字频谱仪设计与实现2017-12-25 13189

-

一种基于CPLD加载FPGA的方案设计详解2019-02-19 2309

-

一种基于FPGA的MSK调制器设计与实现2021-04-27 907

-

一种均衡充电管理威廉希尔官方网站 的实现方案2023-11-14 165

全部0条评论

快来发表一下你的评论吧 !