1、如何理解DC所做的工作

DC的任务是综合,湾湾人称之为合成,综合的概念是通过RTL、单元库、约束,吐出netlist,由于每一个单元库都有各自的特性极限,如果你的约束不合理,如果你的代码不可综合,所以不是每一个RTL的想法都能够跑出netlist。

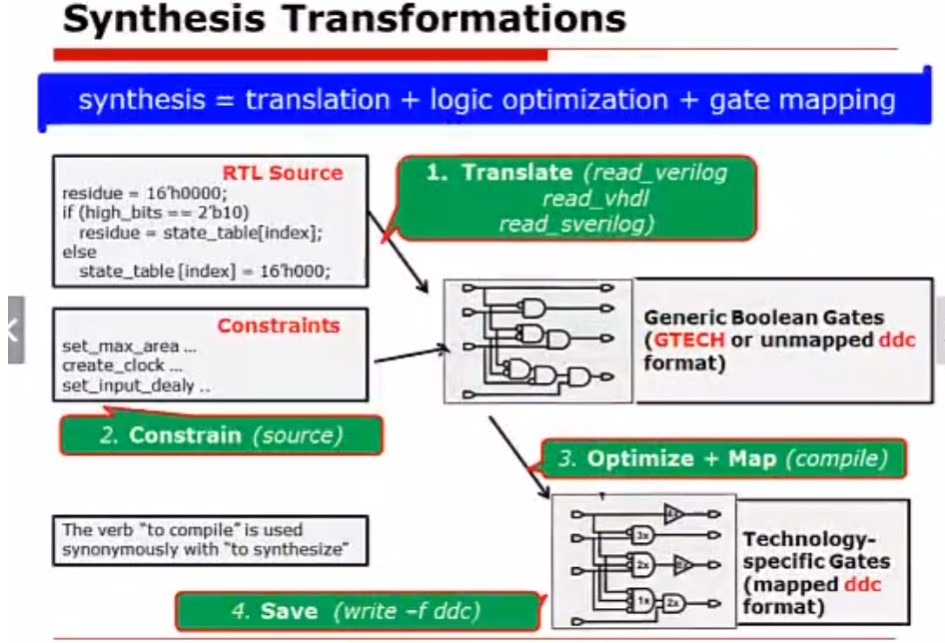

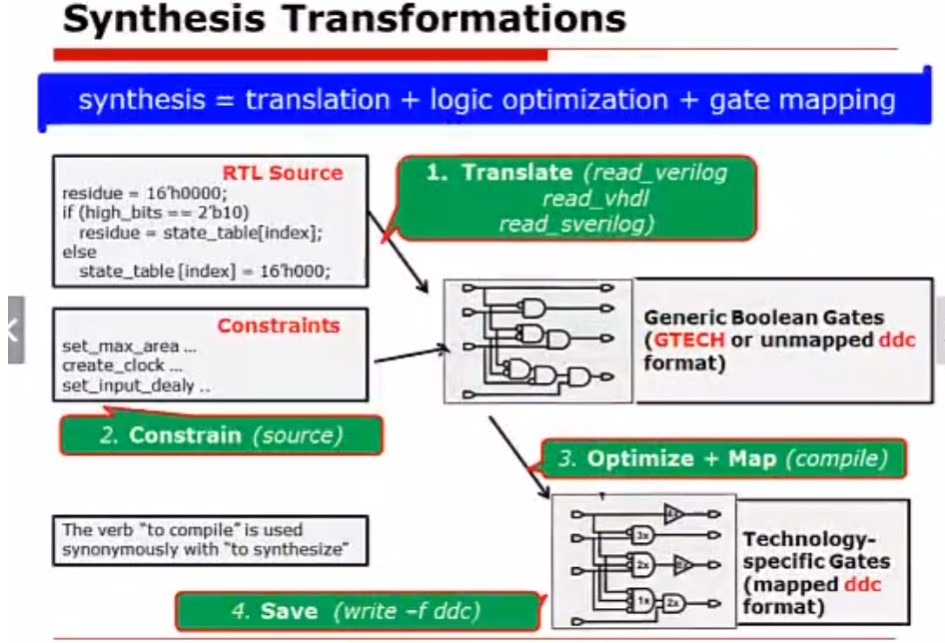

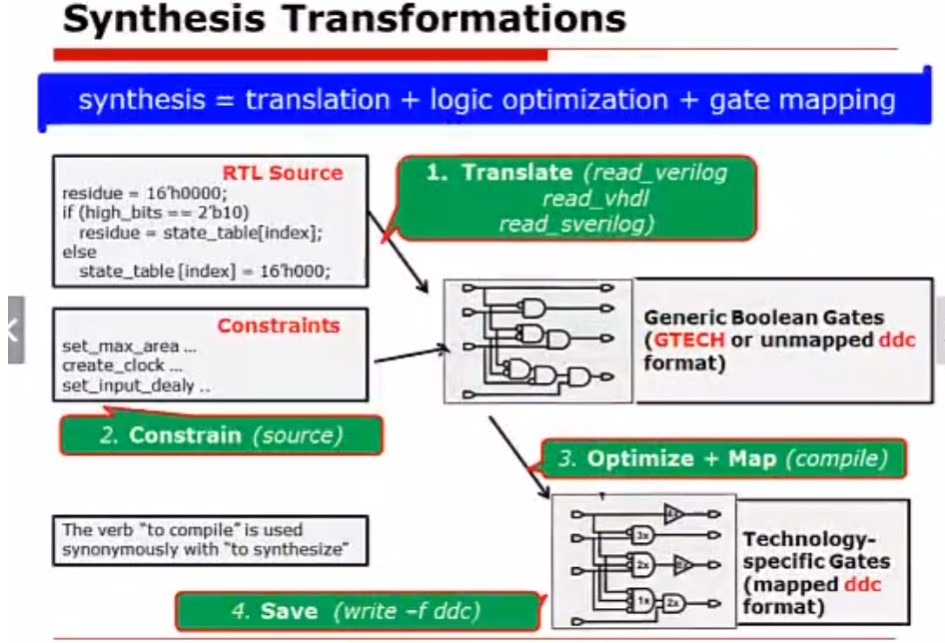

基本的综合可以用一个等式来表达:synthesis = translation + logic optimization + gate mapping

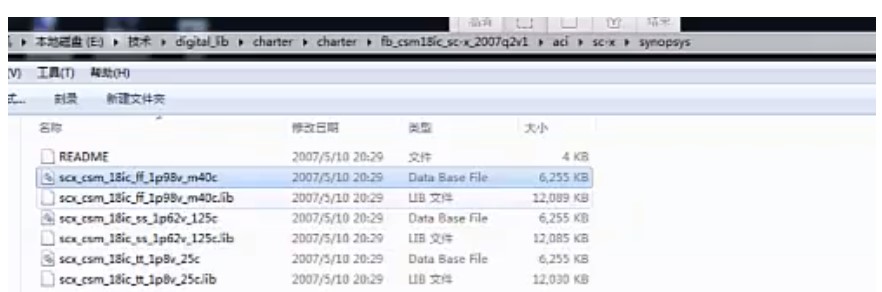

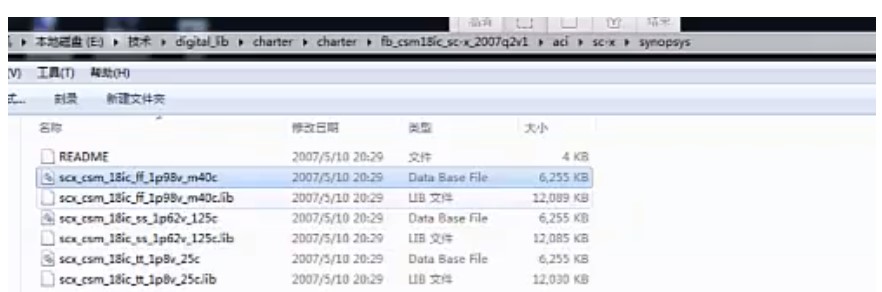

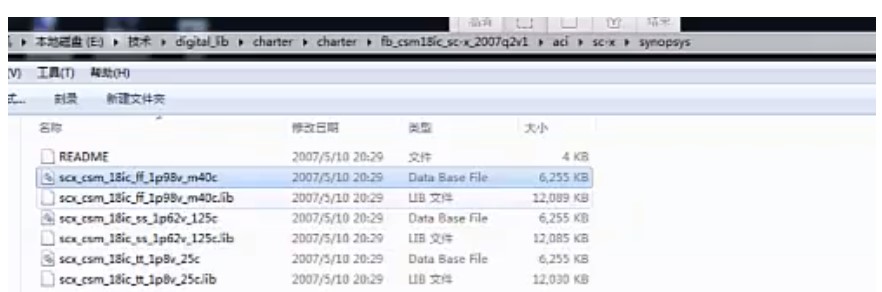

如上图所示,db代表是给工具读的,而lib是给人读的,其中1p98v,代表1.98v,ff代表快速模型。

2、 .synopsys.dc.setup的建立

我们知道安装目录,用户目录,以及工程目录下都可以有这个文件,工程目录下面的优先级是最高的,也是我们经常拿来改动的。这个工程目录下面肯定是空的,需要我们自己手写,所以需要我们一次写好模板,以后拿来用即可。有5个文件夹,mapped是存放综合完成之后的netlist文件的目录,这些文件是经过综合库映射的。Unmaped是存放综合时没有经过工艺库映射所得到的文件目录。

Report是存放报告(比如时序报告、面积报告、DC启动报告等)的目录。Script是存放约束脚本的目录。Work就是启动DC的目录了,在这个目录里面,我们要进行创建.synopsys_dc.setup文件并且编写这个文件,将这个文件放置在work的目录下面。

3、启动文件的知识讲解:

target library: 综合完成后,生成的网标里面的所有基本cell需要的 library. 如:AND/XOR/DFF 等。

官方解释:The target_library specifies the name of the technology library that corresponds to the library whose cells the designers want DC to infer and finally map to.

Target library代表你设计所用到的目标库,是DC在mapping时将设计映射到特定工艺所使用的库,就是使用目标库中的元件综合成设计的门级网表,也就是standard cell的库。通常在综合时,我们都用SS corner下的standard cell库作为target library(也就是选择slow模型下的db), 然后DC会在这些library中去做综合以及优化。通俗点说,只有作综合用的库放在target_library,像ROM,PAD,IO等不用综合的单元,就不要放到target_library中了。

link library:

官方解释:The link_library defines the name of the library that refers to the library of cells used solely for reference。

link library代表设计所用到的链接库。是提供门级网表实例化的基本单元,也就是门级网表实例化的元件或单元都来自该库。链接库定义为standard cell的库文件加上所有IO pad ,memory, IP等宏单元库文件。通常link library会包含target library

target library与link library的区别:

也就是说target library是map时从其中选用stdcell的那个库,link library是包括了target library,同时还包括了设计中用到的IP等宏模块。

target library是给DC让其translate这些std的cell,从而形成netlist,而那些不需要translate的,不需要映射的如IP,memory,PAD等IP,就不必给target library了。

现在我的整个设计的各个部分都已经完成了映射,包括标准的logic 、IO 、IP等,现在我需要将这张已经完成映射的netlist给DC做一个链接,也就是将映射好的每一个部分整合起来,因此,需要都填在link library里面。

本博主的另一种理解是:link library就相当于一个菜单,有没有inv呀,有没有mux呀,相当于一个人点菜一样,把自己需要的东西都写上去,对于这些inv mux就去target library里面去找。在找之前先去内存中去找,所以link library里面需要先加*,然后再去target library里面做一个map的动作,最后将PAD cell 和IP 和基本的logic cell 进行link起来。也就是说link library相当于做一个链接的作用,他负责将那些已经映射好的netlist进行一个顶层的链接。

synthetic library: 这个是综合工具理解你的function block (如RTL code中的 + - / * 等)需要的library.

所以对于synopsys DC来说,synthetic library一般只有:dw_foundation.sldb.

默认的synthetic library一般有:dw_foundation.sldb. 在design compiler的安装目录下可以找到,还有一个是standard.sldb 这个是默认加载的。

https://my.oschina.net/u/4579537/blog/4349836

网上的应该也是照着ug来的

最后网上的还出现了一个hs_name_rules.v 这个我没用到过,说是对verilog的命名规则的检查。

另外,set与set_app_var有什么区别呢

如果定义了一个不是DC的内部变量使用set_app_var就会报错。

因此为了风险性,建议,如果你是在定义DC的内部变量,比如说search_path的话,需要使用set_app_var更加安全,否则我可能错误set targrt_library 这样也不会报错。

此外,对于search_path变量来说就是,DC会在search_path中挨着一个一个地根据这个路径来寻找后面设置的.db文件等。

所以在后面设置DC内部变量的时候,只需要写上文件名 xxx.db xxx.sldb等等即可。

为什么set_app_var search_path [list 。 $search_path。。。。。

里面还有一个search_path,因为里面这个search_path指的是根目录文件里面的.synopsys_dc_setup里面的默认的search_path。前面已经说过这个work目录下面的启动文件只是将里面的变量的优先级调到最高。如果不写的话,这个search_path就会完全覆盖掉根目录下面的search_path,所以你还可以看到有人用的是追加列表append而不是set。

什么是Design Ware?

DesignWare为synopsys自己开发的一些软IP,其中包括加法器,乘法器,比较器,FIFO等IP,根据约束,DC会直接调用相应适合的IP核。

define_design_lib指定中间文件存放到work目录,否则默认会存放到当前目录,文件多了看起来比较混乱。另外,建议使用current_design命令显式指定当前模块。

如果我使用如下,这个启动文件,我是在my_li的文件夹下面,是没问题的。也就是说文件夹,是指我的工作文件夹,也就是我的启动环境的文件夹。通常来说就为work。如果你在work路径下,然而你这里的filename为比如一个my_li,就会报错,你就写你的当前启动环境所在的文件夹就可以了。

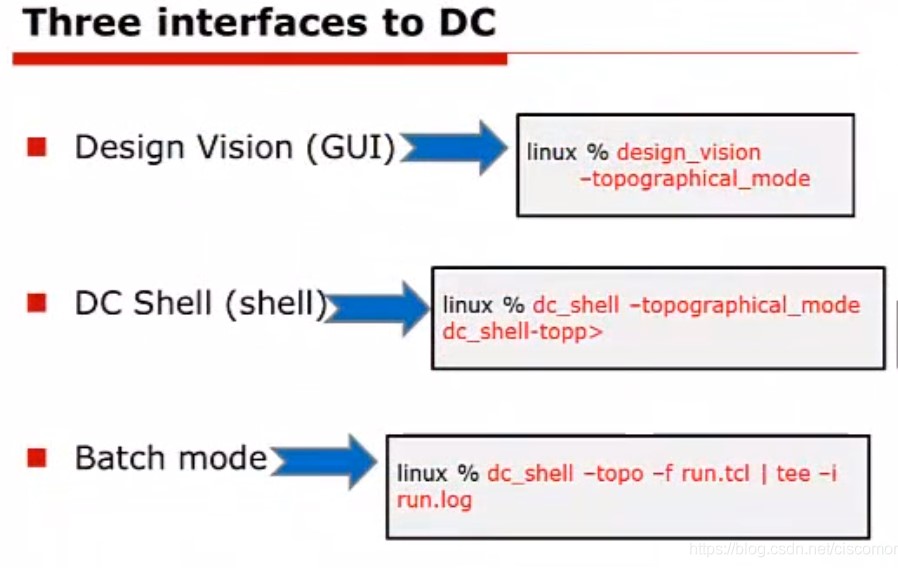

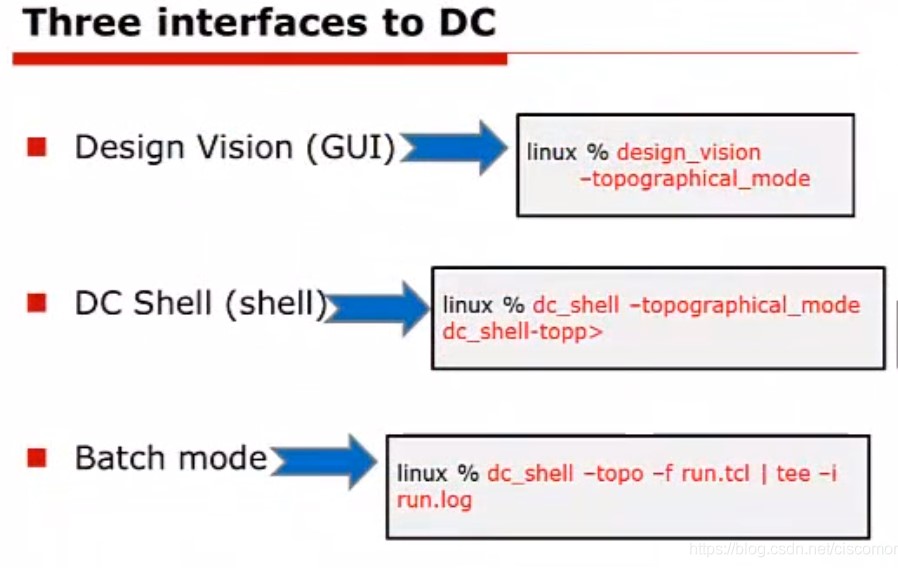

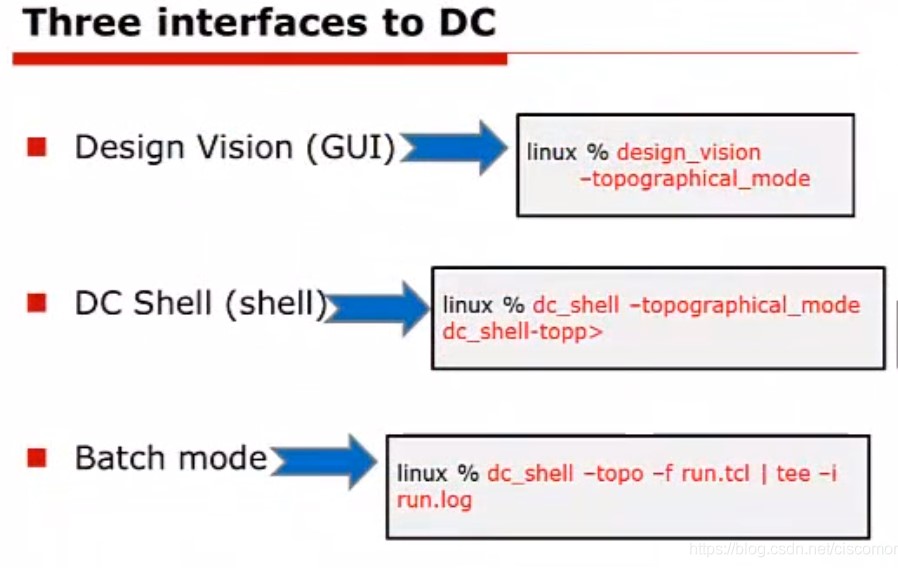

4、启动DC吧

这里,我们现在已经配置好的启动文件,你现在准备好手中的RTL,随便用一个你以前写过的不带IP核的RTL好了(以后会介绍如何用IP核)。除了约束我们现在不用管,脚本也不用管。我们先把DC跑起来吧。

在work目录下面,我们启动之前写好的启动文件。

我们使用了

dc_shell | tee start.log

从而让这份启动日志也打印在start.log中

如下图所示我们使用read_verilog命令,值得注意的是如果我们用*.v是不可以的,这里由于只有一个文件,我还是展示一下列表的使用,另外,由于我们在search_path里面指定了路径,因此就会在里面去搜索,所以,这里只用写.v的文件名就可以了

接着做一个link

link没有参数

详见syn2 link的用法,建议这里可以看一下,能对DC有进一步的理解。

使用list_libs 查看当前内存中所有使用的库

使用list_designs来查看当前的设计有几个module。下图在TOP.v文件里面有4个module,其中TOP.V是顶层的module。

其中*代表顶层的current_design

也可以直接使用current_design 来查看

5、再看看workshop吧

按理说,前面已经把启动文件已经写好了,这里就应该收尾了,想必你也一样曾在eetop上下载过官方的workshop吧,刚开始后的时候,我也不知索然,因为发现视频里面讲解的.synopsys_dc.setup根本不一样。

但是现在你要是已经明白了刚才我介绍的那些命令,应该知道了。

A路径变量的定义我们会放在common_setup.tcl中(一般是用set设置的变量)。

B库变量的指定我们一般放在dc_setup.tcl这个文件中,这里的库变量一般是用set_app_var进行指定,此外指定的是具体的某一个库,而不仅仅是路径,DC会从search_path里面寻找到这些库。

C.synopsys_dc.setup文件中,仅仅包含source xxx.tcl这些内容,比如source common_setup.tcl ;source dc_setup.tcl 以及source其他的设置内容。

所以官方是按照这样设计的。其实也没关系,我们再来看看官方是怎样启动的。

1、如何理解DC所做的工作

DC的任务是综合,湾湾人称之为合成,综合的概念是通过RTL、单元库、约束,吐出netlist,由于每一个单元库都有各自的特性极限,如果你的约束不合理,如果你的代码不可综合,所以不是每一个RTL的想法都能够跑出netlist。

基本的综合可以用一个等式来表达:synthesis = translation + logic optimization + gate mapping

如上图所示,db代表是给工具读的,而lib是给人读的,其中1p98v,代表1.98v,ff代表快速模型。

2、 .synopsys.dc.setup的建立

我们知道安装目录,用户目录,以及工程目录下都可以有这个文件,工程目录下面的优先级是最高的,也是我们经常拿来改动的。这个工程目录下面肯定是空的,需要我们自己手写,所以需要我们一次写好模板,以后拿来用即可。有5个文件夹,mapped是存放综合完成之后的netlist文件的目录,这些文件是经过综合库映射的。Unmaped是存放综合时没有经过工艺库映射所得到的文件目录。

Report是存放报告(比如时序报告、面积报告、DC启动报告等)的目录。Script是存放约束脚本的目录。Work就是启动DC的目录了,在这个目录里面,我们要进行创建.synopsys_dc.setup文件并且编写这个文件,将这个文件放置在work的目录下面。

3、启动文件的知识讲解:

target library: 综合完成后,生成的网标里面的所有基本cell需要的 library. 如:AND/XOR/DFF 等。

官方解释:The target_library specifies the name of the technology library that corresponds to the library whose cells the designers want DC to infer and finally map to.

Target library代表你设计所用到的目标库,是DC在mapping时将设计映射到特定工艺所使用的库,就是使用目标库中的元件综合成设计的门级网表,也就是standard cell的库。通常在综合时,我们都用SS corner下的standard cell库作为target library(也就是选择slow模型下的db), 然后DC会在这些library中去做综合以及优化。通俗点说,只有作综合用的库放在target_library,像ROM,PAD,IO等不用综合的单元,就不要放到target_library中了。

link library:

官方解释:The link_library defines the name of the library that refers to the library of cells used solely for reference。

link library代表设计所用到的链接库。是提供门级网表实例化的基本单元,也就是门级网表实例化的元件或单元都来自该库。链接库定义为standard cell的库文件加上所有IO pad ,memory, IP等宏单元库文件。通常link library会包含target library

target library与link library的区别:

也就是说target library是map时从其中选用stdcell的那个库,link library是包括了target library,同时还包括了设计中用到的IP等宏模块。

target library是给DC让其translate这些std的cell,从而形成netlist,而那些不需要translate的,不需要映射的如IP,memory,PAD等IP,就不必给target library了。

现在我的整个设计的各个部分都已经完成了映射,包括标准的logic 、IO 、IP等,现在我需要将这张已经完成映射的netlist给DC做一个链接,也就是将映射好的每一个部分整合起来,因此,需要都填在link library里面。

本博主的另一种理解是:link library就相当于一个菜单,有没有inv呀,有没有mux呀,相当于一个人点菜一样,把自己需要的东西都写上去,对于这些inv mux就去target library里面去找。在找之前先去内存中去找,所以link library里面需要先加*,然后再去target library里面做一个map的动作,最后将PAD cell 和IP 和基本的logic cell 进行link起来。也就是说link library相当于做一个链接的作用,他负责将那些已经映射好的netlist进行一个顶层的链接。

synthetic library: 这个是综合工具理解你的function block (如RTL code中的 + - / * 等)需要的library.

所以对于synopsys DC来说,synthetic library一般只有:dw_foundation.sldb.

默认的synthetic library一般有:dw_foundation.sldb. 在design compiler的安装目录下可以找到,还有一个是standard.sldb 这个是默认加载的。

https://my.oschina.net/u/4579537/blog/4349836

网上的应该也是照着ug来的

最后网上的还出现了一个hs_name_rules.v 这个我没用到过,说是对verilog的命名规则的检查。

另外,set与set_app_var有什么区别呢

如果定义了一个不是DC的内部变量使用set_app_var就会报错。

因此为了风险性,建议,如果你是在定义DC的内部变量,比如说search_path的话,需要使用set_app_var更加安全,否则我可能错误set targrt_library 这样也不会报错。

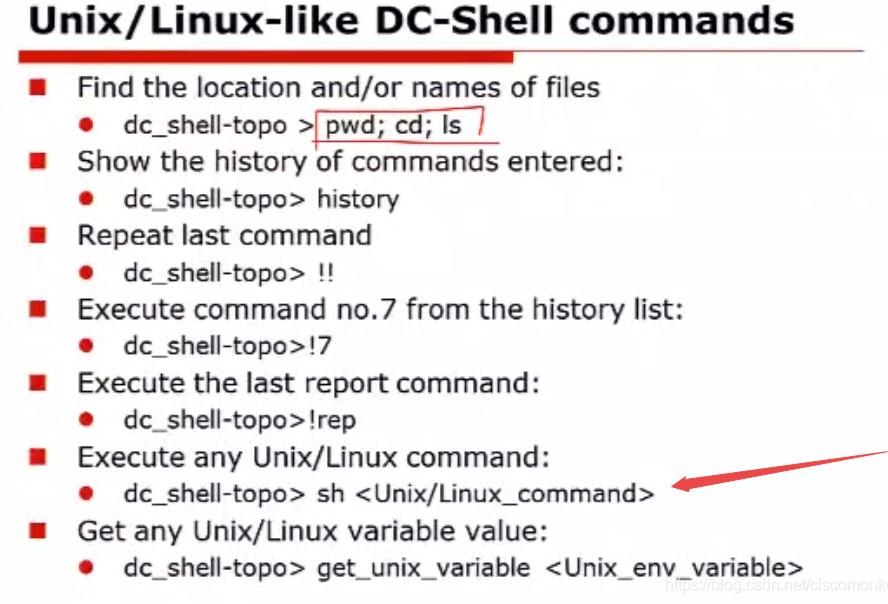

此外,对于search_path变量来说就是,DC会在search_path中挨着一个一个地根据这个路径来寻找后面设置的.db文件等。

所以在后面设置DC内部变量的时候,只需要写上文件名 xxx.db xxx.sldb等等即可。

为什么set_app_var search_path [list 。 $search_path。。。。。

里面还有一个search_path,因为里面这个search_path指的是根目录文件里面的.synopsys_dc_setup里面的默认的search_path。前面已经说过这个work目录下面的启动文件只是将里面的变量的优先级调到最高。如果不写的话,这个search_path就会完全覆盖掉根目录下面的search_path,所以你还可以看到有人用的是追加列表append而不是set。

什么是Design Ware?

DesignWare为synopsys自己开发的一些软IP,其中包括加法器,乘法器,比较器,FIFO等IP,根据约束,DC会直接调用相应适合的IP核。

define_design_lib指定中间文件存放到work目录,否则默认会存放到当前目录,文件多了看起来比较混乱。另外,建议使用current_design命令显式指定当前模块。

如果我使用如下,这个启动文件,我是在my_li的文件夹下面,是没问题的。也就是说文件夹,是指我的工作文件夹,也就是我的启动环境的文件夹。通常来说就为work。如果你在work路径下,然而你这里的filename为比如一个my_li,就会报错,你就写你的当前启动环境所在的文件夹就可以了。

4、启动DC吧

这里,我们现在已经配置好的启动文件,你现在准备好手中的RTL,随便用一个你以前写过的不带IP核的RTL好了(以后会介绍如何用IP核)。除了约束我们现在不用管,脚本也不用管。我们先把DC跑起来吧。

在work目录下面,我们启动之前写好的启动文件。

我们使用了

dc_shell | tee start.log

从而让这份启动日志也打印在start.log中

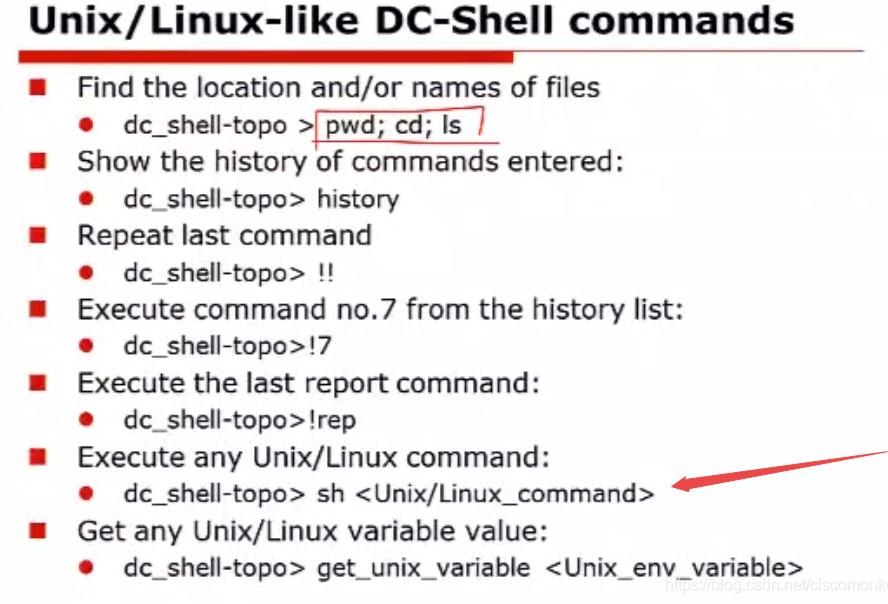

如下图所示我们使用read_verilog命令,值得注意的是如果我们用*.v是不可以的,这里由于只有一个文件,我还是展示一下列表的使用,另外,由于我们在search_path里面指定了路径,因此就会在里面去搜索,所以,这里只用写.v的文件名就可以了

接着做一个link

link没有参数

详见syn2 link的用法,建议这里可以看一下,能对DC有进一步的理解。

使用list_libs 查看当前内存中所有使用的库

使用list_designs来查看当前的设计有几个module。下图在TOP.v文件里面有4个module,其中TOP.V是顶层的module。

其中*代表顶层的current_design

也可以直接使用current_design 来查看

5、再看看workshop吧

按理说,前面已经把启动文件已经写好了,这里就应该收尾了,想必你也一样曾在eetop上下载过官方的workshop吧,刚开始后的时候,我也不知索然,因为发现视频里面讲解的.synopsys_dc.setup根本不一样。

但是现在你要是已经明白了刚才我介绍的那些命令,应该知道了。

A路径变量的定义我们会放在common_setup.tcl中(一般是用set设置的变量)。

B库变量的指定我们一般放在dc_setup.tcl这个文件中,这里的库变量一般是用set_app_var进行指定,此外指定的是具体的某一个库,而不仅仅是路径,DC会从search_path里面寻找到这些库。

C.synopsys_dc.setup文件中,仅仅包含source xxx.tcl这些内容,比如source common_setup.tcl ;source dc_setup.tcl 以及source其他的设置内容。

所以官方是按照这样设计的。其实也没关系,我们再来看看官方是怎样启动的。

举报

举报

举报

举报