FPGA驱动AD7606B,FPGA时序描述如下:

1、首先是AD7606B复位时序:RESET拉低并延时等待11ms确认tPOWER-UP后,将RESET置高并等待3.1us确认tRESET完全复位后,再将RESET拉低并等待260us确认tDEVICE_SETUP完全复位后,输出初始状态:CONVRT=0,CS=1,RD=1。

2、进入状态机循环:

状态0:保持初始状态20ns;CONVRT=0,CS=1,RD=1。

状态1:再延时20ns后将CONVRT置高;CONVRT=1,CS=1,RD=1。

状态2:延时20ns后等待BUSY信号的高电平到来。

状态3:延时100ns后再次确认BUSY信号的高电平,若此时BUSY信号不为高电平,则为BUSY的干扰信号返回状态0。

状态4:延时400ns后等待BUSY信号的低电平到来;检测到低电平后将CS拉低;CONVRT=1,CS=0,RD=1。

状态5:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态6:延时20ns后等待FRSTDATA信号的高电平到来;检测到高电平后将RD置高,并读取CH1的转换数据;CONVRT=1,CS=0,RD=1。

状态7:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态8:延时20ns后将RD置高,并读取CH2的转换数据;CONVRT=1,CS=0,RD=1。

状态9:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态10:延时20ns后将RD置高,并读取CH3的转换数据;CONVRT=1,CS=0,RD=1。

状态11:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态12:延时20ns后将RD置高,并读取CH4的转换数据;CONVRT=1,CS=0,RD=1。

状态13:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态14:延时20ns后将RD置高,并读取CH5的转换数据;CONVRT=1,CS=0,RD=1。

状态15:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态16:延时20ns后将RD置高,并读取CH6的转换数据;CONVRT=1,CS=0,RD=1。

状态17:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态18:延时20ns后将RD置高,并读取CH7的转换数据;CONVRT=1,CS=0,RD=1。

状态19:延时20ns后将RD拉低;CONVRT=1,CS=0,RD=0。

状态20:延时20ns后将RD置高,并读取CH8的转换数据;CONVRT=1,CS=0,RD=1。

状态21:延时20ns后将CONVRT拉低,CS置高后等待采样周期(10us)信号到来;采样周期到达后返还状态0;CONVRT=0,CS=1,RD=1。

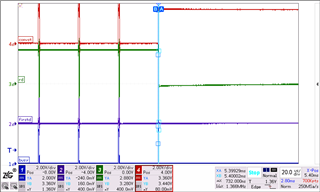

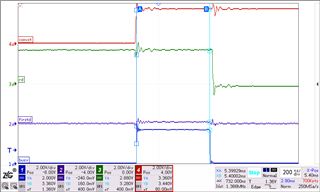

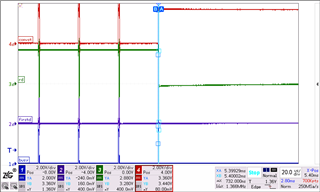

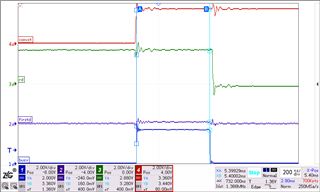

经过长时间测试发现:FRSTDATA偶尔会没高电平输出,导致FPGA时序会卡死在等待FRSTDATA的高电平状态(状态6)。示波器抓图如下: