本篇展示数字时钟功能,具有计时和校时功能。具体数码管从左至右显示小时和分钟,秒钟LED1闪烁显示。三个按键用于时钟校准,校准相应的刻度,该数码管闪烁。。

K1 用于切换正常计时,校准小时和分钟

K2 用于时钟的“+”

K3 用于时钟的“-”

不同于原工程MES2KG\demo\7_watch,这里K1校时依次从小时_高,小时_低,分钟_高,分钟低,且对应数码管从左至右。

一.工程准备

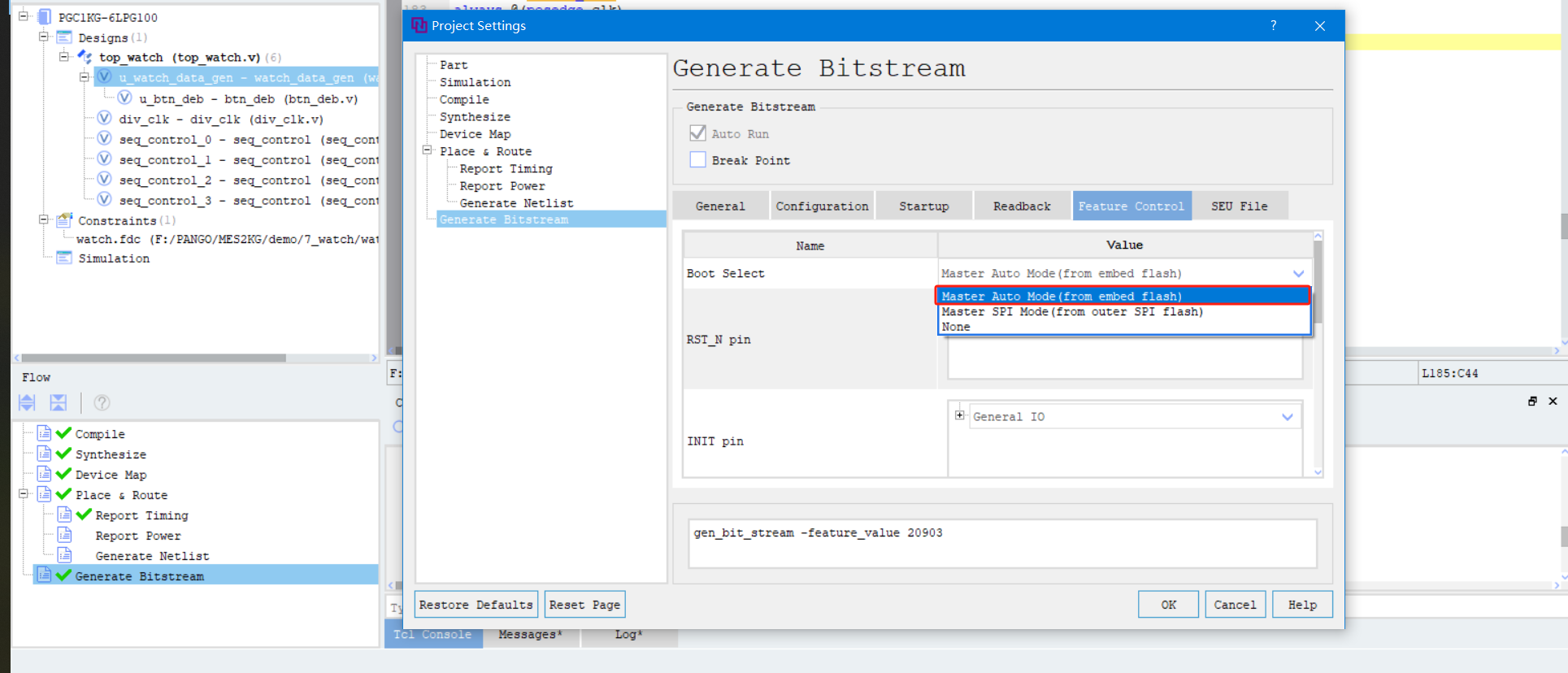

以MES2KG\demo\7_watch为基础,打开工程,选择FPGA型号。这里特别注意检查下位流生成启动配置,如下图Boot Select为NONE则改为MasterAutoMode(from enbed flash),否则点FLASH烧录重上电因启动工作不了。

图1:位流生成配置

二代码修改

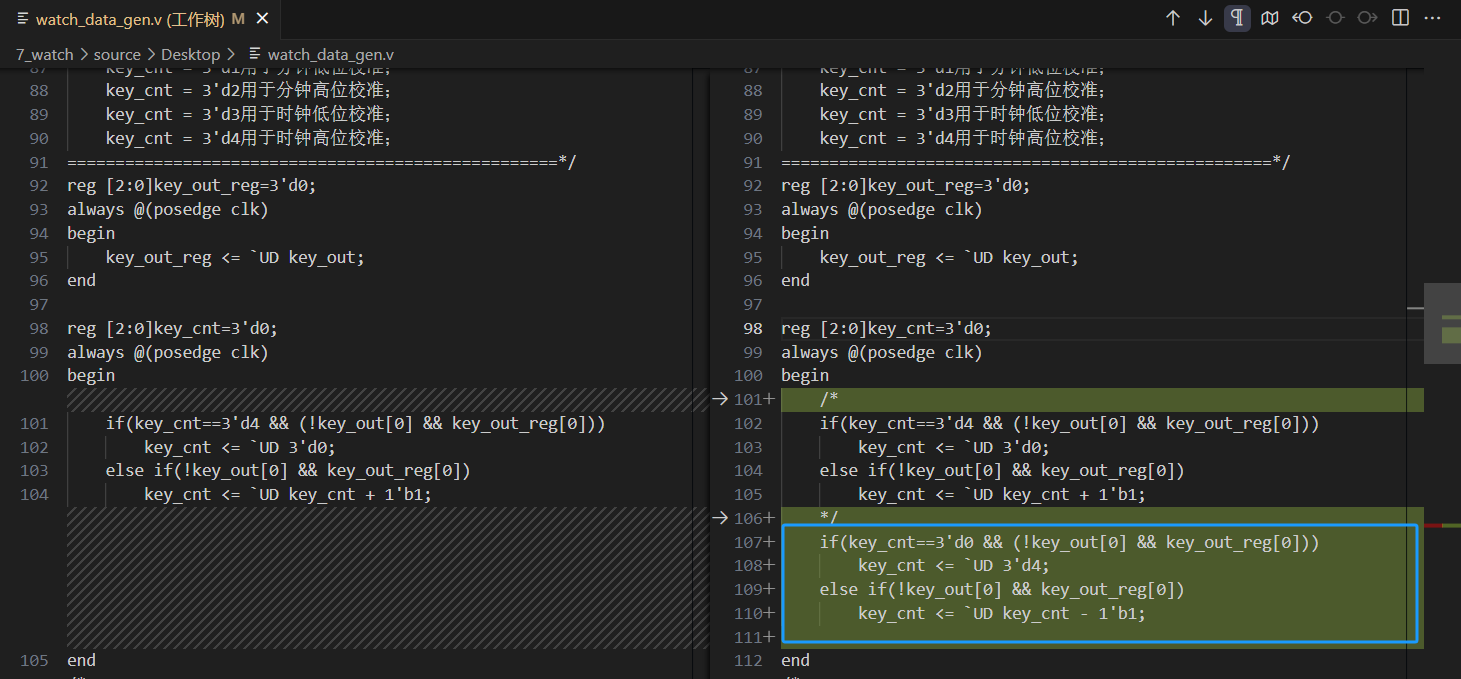

这里修改实现校准从小时到分钟,从高位到低位,随大多数习惯方式设置。代码修改部分如下:

watch_data_gen.v

图2:K1键值控制方式修改

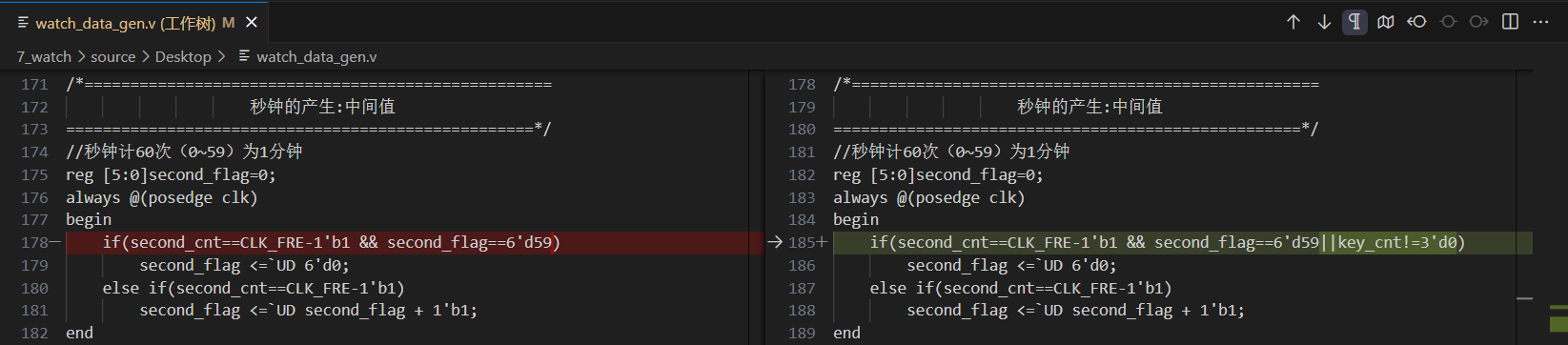

另外做了一点代码优化,即校时设置期间秒数清0,更改如下

图3:校时优化

三.测验

1.编译烧录

2.测试

按按键K1分别为进入校时Hour_H,Hour_L,Min_H,Min_L,退出校时,且相应数码管位做显示;进入校时K2为+1,K3为-1.具体效果见如下视频。