U-BOOT在启动的过程中,需要配置系统时钟。配置系统时钟,大概是以下几个步骤:(1)设置系统PLL锁定时间

(2)配置PLL

(3)配置各模块分频系数

(4)切换到PLL时钟

1.基本原理

首先输出一个高电平,然后,通过三个晶振,输出一个频率,然后,通过倍频器(锁相环),将频率升高,然后,再通过分频,把分出来的不同的频率,提供给不同的器件,比如ARM Cotrex内核、各种设备控制器等等。0k210(S5PV210)上蓝色的框标注的就是晶振的位置,最上面的是27MHz,中间和下面两颗是24MHz,顺便讲一下另外几片东西,最左边的四片是内存DDR2-800,这表示数据传输频率为800MHz,外部时钟频率200MHz,内部时钟频率为100MHz;下面的黄色框是NAND FLASH,外部时钟频率133MHz。

倍频的原理:

下图就是上电后的XXti输出的频率变化图(XXTI引脚见P448的系统时钟流程图最左边的XXTI引脚,XXTI的详细介绍见P354的Figure 3-2 S5PV210 Top-Level Clocks),频率从小变到指定频率需要一段时间(图中标红框的部分),当CPU频率在变化的时候,比如由复位后的初始的400HZ,我要升到1000HZ, 这时,首先把CPU的频率锁定,因这此时CPU的频率是变化的,频率变化,CPU的状态就无法确定,所以,此时用PLL--phase-locked loop锁相环,将CPU频率锁定一段时间,直到我的频率输出稳定为止。芯片手册上显示APLL默认的设置时间为30us。(注:我参考的是S5PV210RISC MicroprocessorRevision1.10

May 2010版本的芯片手册)

分频的原理:

设置不同的位,比如,设置某一位为0,那么,分频时,原来频率比如为1000HZ,那么频率就被分为1000/1=1000Hz, 这样就可以分给ARMCLK使用。

ddr2工作原理分析

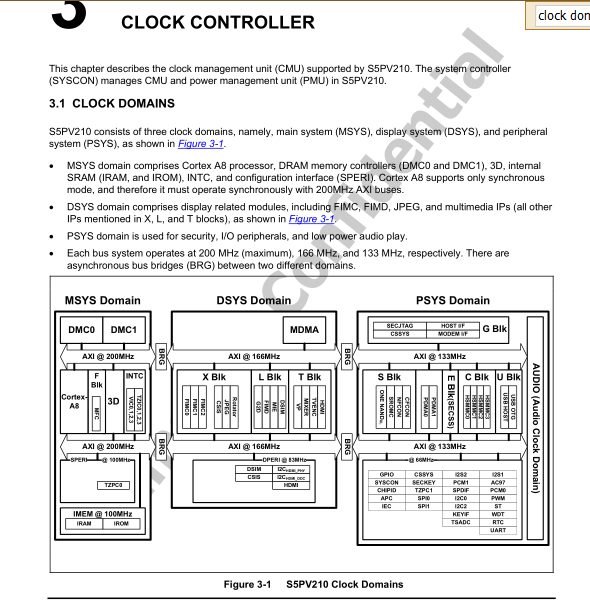

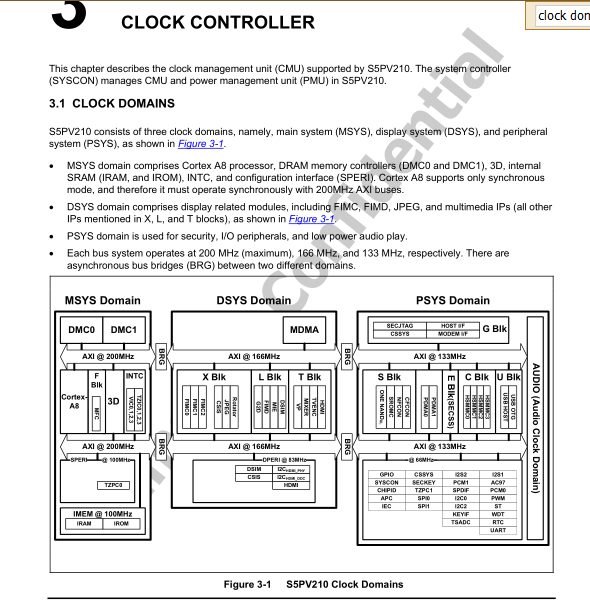

S5PV210的Clock分为三个domain,意思是三个区域--MSYS,DSYS,PSYS,这三个区域分别都是AMBA总线,AMBA总线分为AHB和APB两种总线(这是不严格的分法,仅仅是便于理解),每种总线都有不同的时钟频率,AHB--HCLK/APB--PCLK

那么MSYS,DSYS,PSYS最少有6个时钟(实际上不止6个),分别为HCLK_MSYS/PCLK_MSYS、HCLK_DSYS/PCLK_DSYS、HCLK_PSYS/PCLK_PSYS,再外加一个CPU要用的时钟ARMCLK,总共7个时钟频率。MSYS,DSYS,PSYS分别管理不同的设备,为不同的设备提供不同的频率。

这些不同设备的频率是如何产生?由图可知最后,总共有13个CLK。

由上图可知,通过XOM[0]产生频率,然后在APLL升频,然后在分频1时,有一个两级分频,然后,在分频2又有一个8级分频,最后,就可以输出一个频率,提供给S5PV210的ARM芯片使用,P356页查到常用的CLK值,这里我们的S5PV210的ARMCLK为1000MHz。

那么,在硬件上是如何实现的呢?

开发板上晶振有三颗,两个24kHz,一个27kHz。(晶振,全名晶体振荡器,成份石英(二氧化硅),晶振用于通过压电效应给CPU提出振荡频率,再通过别的威廉希尔官方网站

,将例如正弦曲线波转换成方波有了晶振,CPU才有频率输出)。

CPU第一次启动时,PLL有一个默认的初始值,芯片手册找到P522页,找到默认的初始频率:

• APLL: M=200, P=6, S=1 FOUT = (MDIV X FIN )/ (PDIV X 2(SDIV-1))) = 800MHz

• MPLL: M=667, P=12, S=1 FOUT = (MDIV X FIN) / (PDIV X 2SDIV) = 667MHz

• EPLL: M=80, P=3, S=3, K=0 FOUT = ((MDIV+KDIV) X FIN) / (PDIV X 2SDIV) = 80MHz

To speed up first boot loader’s operation, the first boot loader initializes the PLL with fixed value. Fixed PLL setting

is as follows:

• APLL: M=200, P=6, S=1 FOUT = (MDIV X FIN )/ (PDIV X 2 (SDIV-1) )) = 800MHz

• MPLL: M=667, P=12, S=1 FOUT = (MDIV X FIN) / (PDIV X 2 SDIV ) = 667MHz

• EPLL: M=80, P=3, S=3, K=0 FOUT = ((MDIV+KDIV) X FIN) / (PDIV X 2 SDIV ) = 80MHz

由上图查出可知,ARMCLK的默认频率为400MHz

1)查看芯片手册的P355页,查出总共有以下几种由CMU输出的时钟

有四种PLLs(APLL,MPLL,EPLL,HPLL),还包括USB_OTG PHY clock。

3.2.2 CLOCKS FROM CMU

CMU generates internal clocks with intermediate frequencies using clocks from the clock pads (that is, XRTCXTI,

XXTI, XUSBXTI, and XHDMIXTI), four PLLs (that is, APLL, MPLL, EPLL, and VPLL), USB PHY and HDMI PHY

clock. Some of these clocks can be selected, pre-scaled, and provided to the corresponding modules.

It is recommended to use 24MHz input clock source for APLL, MPLL, EPLL and VPLL.

To generate internal clocks, the following components are used.

• APLL uses FINPLL (refer to Figure 3-1) as input to generate 30MHz ~ 1GHz.

• MPLL uses FINPLL as input to generate 50MHz ~ 2GHz.

• EPLL uses FINPLL as input to generate 10MHz ~ 600MHz.

• VPLL uses FINPLL or SCLK_HDMI27M as input to generate 10MHz ~ 600MHz. This PLL generates 54MHz

video clock.

• USB OTG PHY uses XUSBXTI to generate 30MHz and 48MHz

• HDMI PHY uses XUSBXTI or XHDMIXTI to generate 54MHz.

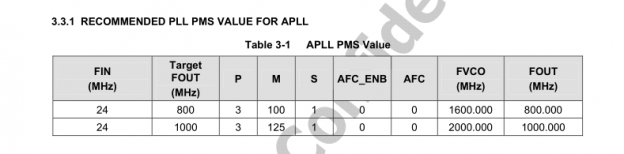

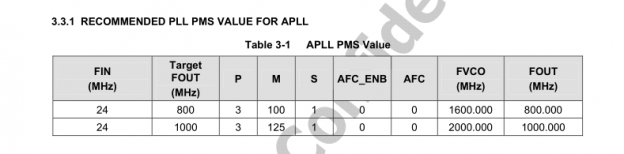

2)先查看APLL PMS的倍频表

P357 S5PV210_UM_REV1.1.pdf -- Table 3-1. APLL PMS Value

S5PV210 has four PLLs, namely, APLL, MPLL, EPLL, and VPLL.

• APLL: used to generate ARM clock

• MPLL: used to generate system bus clock and several special clocks

• EPLL: used to generate several special clocks

• VPLL: used to generate Video clocks. Usually, generates 54 MHz.

查看芯片手册,设置P/M/S的bit,可以将频率拉升到我们想要的频率。

那么我们要设置升高频,翻看手册,P371页,找到PLL CONTROL REGISTERS。

• (APLL_LOCK, R/W, Address = 0xE010_0000)

• (MPLL_LOCK, R/W, Address = 0xE010_0008)

• (EPLL_LOCK, R/W, Address = 0xE010_0010)

• (VPLL_LOCK, R/W, Address = 0xE010_0020)

下篇预告《uboot源码之系统时钟配置》

举报

举报