时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能。

时钟发生器芯片厂家可输出差分100MHz,125MHz,156.25MHz和单端33.33MHz CPU时钟,同时输出6路25MHz缓冲参考时钟。

Ø 主要特性

l 7路单端LVCMOS输出,输出阻抗为30Ω;

l 3对LVPECL输出

-- 1路差分LVPECL输出对(QA,nQA)的输出频率为156.25 MHz

-- 2路可选的差分LVPECL输出对(QB,nQB和QC,nQC)的输出频率为100 MHz和125 MHz

l 1路单端LVCMOS输出(QD)的频率为33.33MHz CPU时钟

l 可选外部晶体或单端输入源

l 晶体振荡器接口用于25MHz晶体

l DCO频率:2.5GHz

l 125MHz下的RMS相位抖动,使用25MHz晶体(12kHz~20MHz):0.188ps(典型值)

l 电源噪声抑制PSNR:-70dB

l +3.3 V电源电压

l -40°C至85°C环境工作温度

l 无铅(RoHS 6)封装

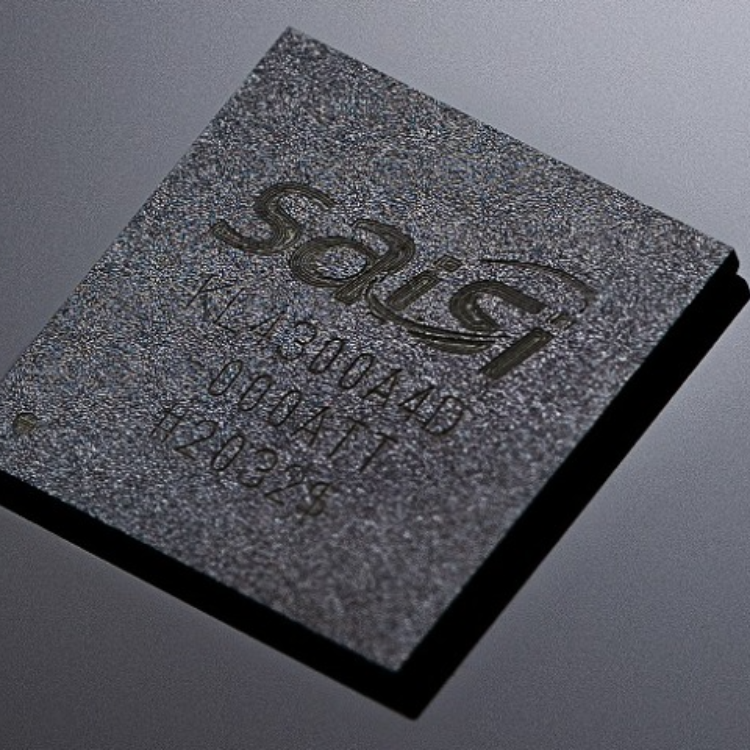

l 40引脚VFQFN封装6.0 × 6.0 × 0.85mm

Ø 时钟芯片应用场景

l 无线基站

l 以太网线卡,交换机和路由器

l SCSI,SATA,and PCI-express

l 低抖动,低相噪时钟发生器