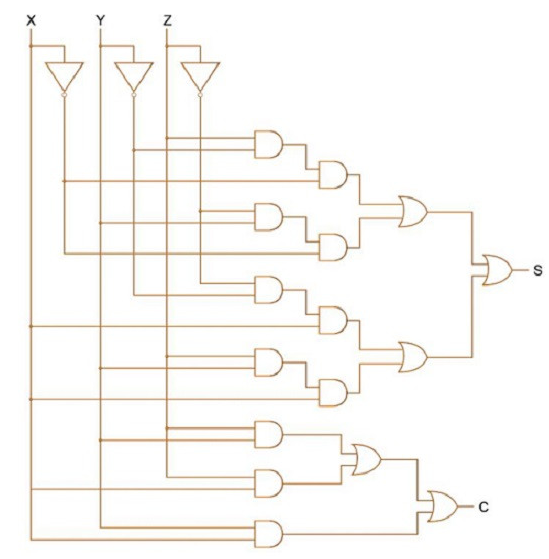

用两个全加器构成二一十进制相减器

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电子技术>威廉希尔官方网站 图>信号处理电子威廉希尔官方网站 图>用两个全加器构成二一十进制相减器

相关推荐

0

0 2

2 11018

11018

1

1 15

15 53586

53586

34099

34099

12686

12686 2536

2536

33292

33292 12524

12524

20964

20964 4157

4157

2650

2650 2050

2050 14957

14957

65775

65775

53651

53651

44957

44957

16924

16924

145644

145644

52599

52599

137363

137363

28

28 37

37 12142

12142 23684

23684 5522

5522 8495

8495 1940

1940

3559

3559

评论