时钟周期约束

时钟周期约束,顾名思义,就是我们对时钟的周期进行约束,这个约束是我们用的最多的约束了,也是最重要的约束。

下面我们讲一些Vivado中时钟约束指令。

1. Create_clock

在Vivado中使用create_clock来创建时钟周期约束。使用方法为:

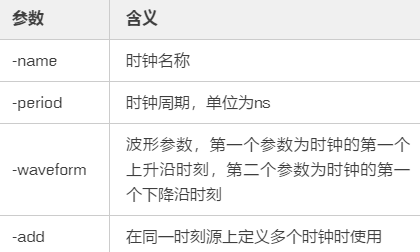

create_clock -name-period -waveform { } [get_ports ]

这里的时钟必须是主时钟primary clock,主时钟通常有两种情形:一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:另一种是高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

如何确定主时钟是时钟周期约束的关键,除了根据主时钟的两种情形判断之外,还可以借助Tcl脚本判断。

在vivado自带的example project里面,打开CPU(HDL)的工程,如下图所示。

把工程的xdc文件中,create_clock的几项都注释掉。这里解释下端口(Port)和管脚(Pin)。get_ports获取的是FPGA的IO端口,get_pins获取的是FPGA内部子模块的Pin,具体的我们在第14讲的Tcl命令中会讲到。

再Open Synthesized Design或者Open Implementation Design,并通过以下两种方式查看主时钟。

• 方式一

运行tcl指令report_clock_networks -name mainclock,显示结果如下:

• 方式二

运行tcl指令check_timing -override_defaults no_clock,显示结果如下:

Vivado中的tcl命令行相当好用,有很多的功能,大家可以开始习惯用起来了。

对于高速收发器的时钟,我们也以Vivado中的CPU example工程为例,看下Xilinx官方是怎么约束的。

# Define the clocks for the GTX blocks create_clock -name gt0_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt0_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK] create_clock -name gt2_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt2_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK] create_clock -name gt4_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt4_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK] create_clock -name gt6_txusrclk_i -period 12.8 [get_pins mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt6_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK]

当系统中有多个主时钟,且这几个主时钟之间存在确定的相位关系时,需要用到-waveform参数。如果有两个主时钟,如下图所示。

则时钟约束为:

create_clock -name clk0 -period 10.0 -waveform {0 5} [get_ports clk0]

create_clock -name clk1 -period 8.0 -waveform {2 8} [get_ports clk1]

约束中的数字的单位默认是ns,若不写wavefrom参数,则默认是占空比为50%且第一个上升沿出现在0时刻。使用report_clocks指令可以查看约束是否生效。还是上面的CPU的例子,把约束都还原到最初的状态。执行report_clocks后,如下所示,我们只列出其中几项内容。

Clock Report

Clock Period(ns) Waveform(ns) Attributes Sources

sysClk 10.000 {0.000 5.000} P {sysClk}

gt0_txusrclk_i 12.800 {0.000 6.400} P {mgtEngine/ROCKETIO_WRAPPER_TILE_i/gt0_ROCKETIO_WRAPPER_TILE_i/gtxe2_i/TXOUTCLK}

...

====================================================

Generated Clocks

====================================================

Generated Clock : clkfbout

Master Source : clkgen/mmcm_adv_inst/CLKIN1

Master Clock : sysClk

Multiply By : 1

Generated Sources : {clkgen/mmcm_adv_inst/CLKFBOUT}

Generated Clock : cpuClk_4

Master Source : clkgen/mmcm_adv_inst/CLKIN1

Master Clock : sysClk

Edges : {1 2 3}

Edge Shifts(ns) : {0.000 5.000 10.000}

Generated Sources : {clkgen/mmcm_adv_inst/CLKOUT0}

...

一般来讲,我们的输入时钟都是差分的,此时我们只对P端进行约束即可。如果同时约束了P端和N端,通过report_clock_interaction命令可以看到提示unsafe。这样既会增加内存开销,也会延长编译时间。

2. create_generated_clock

其使用方法为:

create_generated_clock -name/ -source / -multiply_by / -divide_by / -master_clock /

从名字就能看出来,这个是约束我们在FPGA内部产生的衍生时钟, 所以参数在中有个-source,就是指定这个时钟是从哪里来的,这个时钟叫做master clock,是指上级时钟,区别于primary clock。

它可以是我们上面讲的primary clock,也可以是其他的衍生时钟。该命令不是设定周期或波形,而是描述时钟威廉希尔官方网站 如何对上级时钟进行转换。

这种转换可以是下面的关系:

-简单的频率分频

-简单的频率倍频

-频率倍频与分频的组合,获得一个非整数的比例,通常由MMCM或PLL完成

-相移或波形反相

-占空比改变

-上述所有关系的组合

衍生时钟又分两种情况:

① Vivado自动推导的衍生时钟

② 用户自定义的衍生时钟

首先来看第一种,如果使用PLL或者MMCM,则Vivado会自动推导出一个约束。大家可以打开Vivado中有个叫wavegen的工程,在这个工程中,输入时钟经过PLL输出了2个时钟,如下图所示。

但在xdc文件中,并未对这2个输出时钟进行约束,只对输入的时钟进行了约束,若我们使用report_clocks指令,则会看到:

注:有三个约束是因为PLL会自动输出一个反馈时钟

自动推导的好处在于当MMCM/PLL/BUFR的配置改变而影响到输出时钟的频率和相位时,用户无需改写约束,Vivado仍然可以自动推导出正确的频率/相位信息。劣势在于,用户并不清楚自动推导出的衍生钟的名字,当设计层次改变时,衍生钟的名字也有可能改变。但由于该衍生时钟的约束并非我们自定义的,因此可能会没有关注到它名字的改变,当我们使用者这些衍生时钟进行别的约束时,就会出现错误。

解决办法是用户自己手动写出自动推导的衍生时钟的名字,也仅仅写出名字即可,其余的不写。如下所示。

create_generated_clock -name/ -source

这一步很容易会被提示critical warning,其实有个很简单的方法,就是name和source都按照vivado中生成的来。具体我们到后面的例子中会讲到。

3. set_clock_groups

使用方法为:

set_clock_groups -asynchronous -group-group set_clock_groups -physically_exclusive -group -group

这个约束常用的方法有三种,第一种用法是当两个主时钟是异步关系时,使用asynchronous来指定。这个在我们平时用的还是比较多的,一般稍微大点的工程,都会出现至少两个主时钟,而且这两个时钟之间并没有任何的相位关系,这时就要指定:

create_clock -period 10 -name clk1 [get_ports clk1] create_clock -period 8 -name clk2 [get_ports clk2] set_clock_groups -asynchronous -group clk1 -group clk2

第二种用法是当我们需要验证同一个时钟端口在不同时钟频率下能否获得时序收敛时使用。比如有两个异步主时钟clk1和clk2,需要验证在clk2频率为100MHz,clk1频率分别为50MHz、100MHz和200MHz下的时序收敛情况,我们就可以这样写。

create_clock -name clk1A -period 20.0 [get_ports clk1] create_clock -name clk1B -period 10.0 [get_ports clk1] -add create_clock -name clk1C -period 5.0 [get_ports clk1] -add create_clock -name clk2 -period 10.0 [get_ports clk2] set_clock_groups -physically_exclusive -group clk1A -group clk1B -group clk1C set_clock_groups -asynchronous -group "clk1A clk1B clk1C" -group clk2

第三种用法就是当我们使用BUFGMUX时,会有两个输入时钟,但只会有一个时钟被使用。比如MMCM输入100MHz时钟,两个输出分别为50MHz和200MHz,这两个时钟进入了BUFGMUX,如下图所示。

在这种情况下,我们需要设置的时序约束如下:

set_clock_groups -logically_exclusive / -group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT0]] / -group [get_clocks -of [get_pins inst_mmcm/inst/mmcm_adv_inst/CLKOUT1]]

4. 创建虚拟时钟

虚拟时钟通常用于设定对输入和输出的延迟约束,这个约束其实是属于IO约束中的延迟约束,之所以放到这里来讲,是因为虚拟时钟的创建,用到了本章节讲的一些理论。虚拟时钟和前面讲的延迟约束的使用场景不太相同。顾名思义,虚拟时钟,就是没有与之绑定的物理管脚。

虚拟时钟主要用于以下三个场景:

• 外部IO的参考时钟并不是设计中的时钟

• FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

• 针对I/O指定不同的jitter和latency

简而言之,之所以要创建虚拟时钟,对于输入来说,是因为输入到FPGA数据的捕获时钟是FPGA内部产生的,与主时钟频率不同;或者PCB上有Clock Buffer导致时钟延迟不同。对于输出来说,下游器件只接收到FPGA发送过去的数据,并没有随路时钟,用自己内部的时钟去捕获数据。

如下图所示,在FPGA的A和B端口分别有两个输入,其中捕获A端口的时钟是主时钟,而捕获B端口的时钟是MMCM输出的衍生时钟,而且该衍生时钟与主时钟的频率不是整数倍关系。

这种情况下时序约束如下:

create_clock -name sysclk -period 10 [get_ports clkin] create_clock -name virclk -period 6.4 set_input_delay 2 -clock sysclk [get_ports A] set_input_delay 2 -clock virclk [get_ports B]

可以看到,创建虚拟时钟用的也是create_clock约束,但后面并没有加get_ports参数,因此被称为虚拟时钟。

再举个输出的例子,我们常用的UART和SPI,当FPGA通过串口向下游器件发送数据时,仅仅发过去了uart_tx这个数据,下游器件通过自己内部的时钟去捕获uart_tx上的数据,这就需要通过虚拟时钟来约束;而当FPGA通过SPI向下游器件发送数据时,会发送sclk/sda/csn三个信号,其中sclk就是sda的随路时钟,下游器件通过sclk去捕获sda的数据,而不是用自己内部的时钟,这是就不需要虚拟时钟,直接使用set_output_delay即可。

注意,虚拟时钟必须在约束I/O延迟之前被定义。

5. 最大最小延迟约束

顾名思义,就是设置路径的max/min delay,主要应用场景有两个:

• 输入管脚的信号经过组合逻辑后直接输出到管脚

• 异步威廉希尔官方网站

之间的最大最小延迟

设置方式为:

set_max_delay[-datapath_only] [-from ][-to ][-through ] set_min_delay [-from ] [-to ][-through ]

max/min delay的约束平时用的相对少一些,因为在跨异步时钟域时,我们往往会设置asynchronous或者false_path。对于异步时钟,我们一般都会通过设计来保证时序能够收敛,而不是通过时序约束来保证。

-

FPGA

+关注

关注

1629文章

21735浏览量

603175 -

时序约束

+关注

关注

1文章

115浏览量

13419 -

Vivado

+关注

关注

19文章

812浏览量

66499

发布评论请先 登录

相关推荐

FPGA时序案例分析之时钟周期约束

FPGA时序案例分析之时钟周期约束

评论