引言

本文主要介绍了时钟偏差和时钟抖动。

一、时钟偏差的相关概念

时钟偏差 Clock Skew 是指同一个时钟域内的时钟信号,到达各个模块(如寄存器)所用的时间偏差(由于布线长度不一致以及存在的线延时)。

时钟偏差主要分为正偏差和 负偏差 。当信号传输的目标寄存器在接收寄存器之前捕获正确的时钟信号,威廉希尔官方网站 发生正偏差(时钟布线方向与数据流水方向一致);当信号传输的目标寄存器在接收寄存器之后捕获正确的时钟信号,威廉希尔官方网站 发生负偏差(时钟布线方向与数据流水方向相反)。

正偏差和负偏差

二、时钟抖动的相关概念

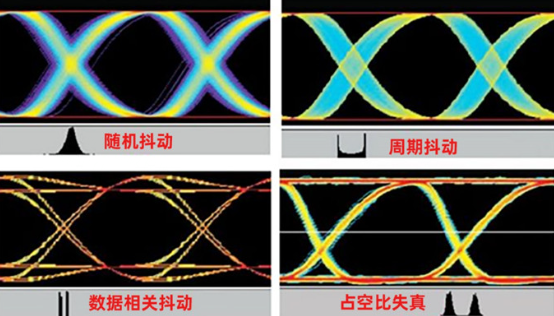

时钟抖动 Clock Jitter 是指相对于理想时钟沿而言,实际时钟所存在的不随时间积累的、时而超前、时而滞后的偏移(时钟脉冲宽度发生了暂时的变化,也就是 Tcycle 或大或小,这是永远存在的);

总结

时钟偏差 Skew 通常是指时钟相位上的不确定,时钟抖动 Jitter 通常是指时钟频率上的不确定;相位为整体移动,频率为单个时钟变动;

时钟偏差和时钟抖动都要求系统时钟宽度增加,以满足建立时间和保持时间的要求,从而降低了系统时钟频率,导致了系统的性能变差。所有的时钟网络布线都应该使用由 FPGA 提供的专用时钟资源(如全局时钟资源、局部时钟资源和 I/O 时钟资源),否则时钟偏差会非常严重。

- 源时钟,指发送数据的时钟;目的时钟,指接收数据的时钟;

- 发送沿,指发送数据的源时钟活动边沿;接收沿,指接收数据的目的时钟活动边沿;

在超大规模集成威廉希尔官方网站 中,存在大量需要时钟信号进行同步的寄存器,这就需要构建一个时钟信号的分布传输网络,来提供时钟偏移尽可能小的同步时序。在集成威廉希尔官方网站 的物理设计阶段,需要设计一个良好的时钟树结构 CTS,通过在时钟信号传输威廉希尔官方网站 上插入具有不同时延参数的缓冲器,可以尽可能地使时钟偏移接近零,即时钟信号近乎同步到达各个寄存器。

-

寄存器

+关注

关注

31文章

5342浏览量

120328 -

缓冲器

+关注

关注

6文章

1922浏览量

45479 -

时钟

+关注

关注

10文章

1733浏览量

131474 -

时钟抖动

+关注

关注

1文章

62浏览量

15926 -

布线

+关注

关注

9文章

771浏览量

84328

发布评论请先 登录

相关推荐

正确理解时钟器件的抖动性能

谈谈非理想时钟的时钟偏差

FPGA如何消除时钟抖动

时钟抖动与相位噪声的关系

时钟抖动和时钟偏移的区别

抖动的概念和类型 量化时域抖动、随机抖动和频域抖动的方法

时钟偏差和时钟抖动的相关概念

时钟偏差和时钟抖动的相关概念

评论