一.压降

LDO(低压降稳压器) 的典型特性便是压降。因为它的名称以及其缩写由此而来。

从根本上来讲,压降它指的是正常的稳压所需要的输入和输出之间的电压差。但是,考虑到各种原因这个压差会发生一些不可控的细微的变化。压降对于实现高效运转或者产生有限的电压余量是非常重要的,下面我们对此进行详细介绍。

压降的介绍

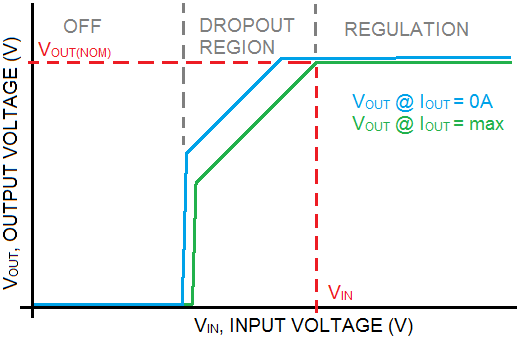

压降电压Vdo的意思是为了实现正常的稳压需求,我们输入的电压Vin必须比输出的电压Vout要高出一个最小压差 Vdo。参见公式1:VIN ≥ VOUT(nom) + VDO (1)

如果输入的电压Vin比很低,我们的LDO,线性稳压器将不会稳出所需输出的电压,这种情况时,Vout输出电压=输入电压Vin-Vdo.

我们以稳压后输出电压为3.3V的降压芯片TPS799等LDO为案例:当输出Vout电流为200mA时,芯片TPS799的最大压降为175mV。也就是说必须输入电压要大于3.375V或更高的电压,它就不会影响降压稳压调节过程。

但是,当输入电压小于3.375V的时侯,LDO芯片TPS799将会处于压降状态而停止调节,如下图所示。

如图,虽然我们要求应该将输出电压Vout调节为3.3V,但是LDO芯片 TPS799 由于没有余量电压来保持稳压。进而,输出电压便会跟随输入电压来变化。

决定压降的因素介绍

压降主要是由低压降稳压器LDO架构的特性来决定,下面举例分析。

如图,为一个PMOS LDO降压器,上图为它的架构,从图中可以看出如果要调节好输出端电压Vout,就必须用反馈回路来把PMOS的DS间的内阻Rds控制好。

当发现输入电压Vin越来越接近输出电压Vout时,误差放大器便会调整PMOS的Vgs电压,来使PMOS的导通内部更加小,进而保持稳压。

当Vgs调整到一定程度也就是Vgs(th)达到饱和

状态时,PMOS的内阻Rds将达到最小值,此时可以得到内阻Rds*输出电流Iout=压降电压。

但是细心的你会发现还有一个办法降低内阻Rds,那就是将输出端Vou的值提高,可以得到Vgs进一步拉大,从而实现需求。

如图,为一个NMOS LDO降压器。原理基本和PMOS LDO是一样的,反馈回路还是控制内阻Rds的大小,当输入端Vin越接近输出电压Vout时,误差放大器便会增加Vgs来降低内阻Rds,进而保持稳压。

-

线性稳压器

+关注

关注

5文章

768浏览量

66639 -

误差放大器

+关注

关注

9文章

98浏览量

34958 -

低压降稳压器

+关注

关注

1文章

102浏览量

8745 -

NMOS管

+关注

关注

2文章

121浏览量

5411 -

PMOS管

+关注

关注

0文章

83浏览量

6633

发布评论请先 登录

相关推荐

低压降稳压器的PSRR特性

什么低压降(LDO)稳压器?

低压差线性稳压器LDO内部原理

Diodes推出全新低压降线性稳压器

Diodes全新低压降线性稳压器(LDO)提升系统稳定性及瞬

电源芯片选择什么好?什么是 LDO(低压降)稳压器?

什么是低压降稳压器(LDO)的压降? - 第五部分

决定低压降稳压器LDO压降的因素介绍

决定低压降稳压器LDO压降的因素介绍

评论