半加器、全加器是组合威廉希尔官方网站 中的基本元器件,也是CPU中处理加法运算的核心,理解、掌握并熟练应用是硬件课程的最基本要求。本文简单介绍半加器、全加器,重点对如何构造高效率的加法器进行分析。

半加器和全加器

所谓半加器,是指对两位二进制数实施加法操作的元器件。其真值表、威廉希尔官方网站 图和逻辑符号分别如下图所示:

根据真值表,其输入输出之间的对应关系为:

从半加器的真值表、威廉希尔官方网站 图可以看出,半加器只能对单个二进制数进行加法操作,只有两个输入,无法接受低位的进位,因此称为半加器。

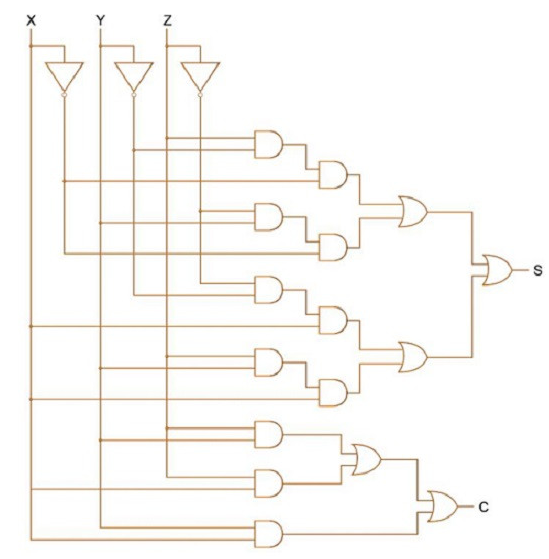

对此,全加器则解决了这个问题,全加器有三个输入(包括来自低位的进位),两个输出,其对应的真值表、威廉希尔官方网站 图和逻辑符号如下所示:

加法器的构造

有了全加器,构造加法器就非常容易了,假设有A3A2A1A0和B3B2B1B0,利用全加器构造A3A2A1A0+B3B2B1B0的串行进位加法器威廉希尔官方网站 图如下图所示:

图中的C-1=0,因为已是最低位,没有进位。这种串联方法只是完成了基本功能,从效率上则完全不可行。

那如何做呢?其实方法挺简单的,只需要把Ci和参与运算的两个4位二进制数之间的关系梳理清楚就行了。直接用代入法展开得:

在这个关系式里,直接列出了4位二进制加法的最终进位,不用等待低位计算完了,再计算高位,而是直接进行计算,最终得到的超前进位加法器威廉希尔官方网站 图如下所示:

假设超前进位加法器中的每个门时延是t,对于4位加法,最多经过4t的时延,而且,即使增加更多的位数,其时延也是4t。

对比串行进位加法器和超前进位加法器,前者线路简单,时延与参与计算的二进制串长度成正比,而后者则是线路复杂,时延是固定值。通常,对于32的二进制串,可以对其进行分组,每8位一组,组内加法用超前进位加法器,组间进位则用串行进位。采用这种折中方法,既保证了效率,又降低了内部线路复杂度。

-

全加器

+关注

关注

10文章

62浏览量

28506 -

半加器

+关注

关注

1文章

29浏览量

8793

发布评论请先 登录

相关推荐

怎么利用QuartuesII查元件真值表

怎么利用QuartusII查元件真值表

求常用单片机的功能表、引脚图、真值表

关于多位输入真值表的问题

输入真值表相同 输出结果不同 74HC138

LUT真值表在实施期间发生了变化

门威廉希尔官方网站 的计算方式 门威廉希尔官方网站 工作原理真值计算

真值表,真值表是什么意思

全加器真值表解释

全加器的真值表

全加器真值表和半加器真值表详细分析

全加器真值表和半加器真值表详细分析

评论