32位处理器可以装64位系统吗?从技术角度看,32位处理器是不能装64位系统的,因为不支持,不确定的用户可以使用下面的两种方法来检查32位处理器是否能装64位系统。方法:通过计算机评分查看1、以

2020-06-28 09:57:16

32位处理器的开发与8位处理器的开发有哪些明显的不同?开发一个32位的嵌入式系统需要哪些工具和环境呢?32位嵌入式系统的开发过程中存在哪些技术难点?有什么方法去应对呢?

2021-04-19 08:11:43

功能和额外的性能,使得整个嵌入式系统的升级只需通过软件的升级即可实现。而8位处理器通常受到的64K软件限制也不存在了,设计者几乎可以任意选择多任务操作系统,并将应用软件设计得复杂庞大,真正体现“硬件软件

2017-04-06 09:11:03

的性能,使得整个嵌入式系统的升级只需通过软件的升级即可实现。而8位处理器通常受到的64K软件限制也不存在了,设计者几乎可以任意选择多任务操作系统,并将应用软件设计得复杂庞大,真正体现“硬件软件化

2017-06-02 18:52:49

的性能,使得整个嵌入式系统的升级只需通过软件的升级即可实现。而8位处理器通常受到的64K软件限制也不存在了,设计者几乎可以任意选择多任务操作系统,并将应用软件设计得复杂庞大,真正体现“硬件软件化

2018-07-04 08:50:08

8086处理器有何功能?中断系统的功能都有哪些呢?

2021-10-29 07:07:41

ADSP-TS201SABP-050 245PCS现货

2019-01-07 10:27:12

PCS.预计春节后3月份到货。ADSP-TS201SAPBZ-060 在途400只+公司库存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

控制器,支持SDRAM协议。以下就是这两种协议的应用。4.1 SDRAM接口ADSP-TS201处理器有一个专用的SDRAM接口.可以实现与标准SDRAM 6 Mb,64 Mb,128 Mb.256

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}报道:ADSP-TS201谁用过

2012-09-19 14:14:35

用于多处理TigerSHARC系统的集群总线通信的详细信号完整性和时序分析。该系统由8个ADSP-TS101S器件,一个主处理器和SDRAM组成,其集群总线运行频率为100MHz。包括仿真结果和物理

2019-08-30 09:24:28

4月7日,全球权威AI基准测试MLPerf发布最新榜单,在聚焦低功耗、高能效的IoT领域Tiny v0.7榜单中,基于平头哥玄铁RISC-V C906处理器的软硬件联合优化方案,取得了全部4个指标

2022-04-08 14:47:36

写了个雷达信号检测的程序,包括经典的处理方法,MTI,多普勒滤波器组,单元平均选大恒虚警门限检测等。分享出来,请大神指点,多谢。

2014-04-29 21:31:03

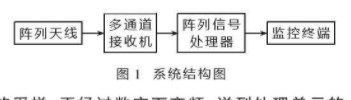

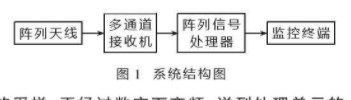

大,耗时长,精度低。随着微电子技术和计算机技术的飞速发展,天线方向图自动测试逐渐取代了手动测量,实现了信号录取、数据处理以及方向图绘制的自动化,大大提高了测量速度和精度。本文介绍了一种雷达天线方向图的自动化测量系统,分析了软硬件结构及原理。

2019-06-11 08:08:05

和 静止 目 标对动 目 标检测 的千扰 。4. 2 经典恒虚警 算法分析 图 4-1 为雷达信 号处理流程 , 如 图表示 回 波信 号经处理后在距离 维和速度维的能量分布情况。 若 当 前检测

2018-02-28 09:19:59

和 静止 目 标对动 目 标检测 的千扰 。4. 2 经典恒虚警 算法分析图 4-1 为雷达信 号处理流程 , 如 图表示 回 波信 号经处理后在距离 维和速度维的能量分布情况。 若 当 前检测 单元 为

2018-03-29 10:53:32

矢量中断控制器(NVIC)与处理器核心紧密集成,以实现低延迟中断处理。

•多个高性能总线接口。

•低成本调试解决方案,具有以下可选功能:

--实现断点和代码修补程序。

--实施监视点、跟踪和系统分析

2023-08-08 07:18:05

解决方案。爱特公司通过扩大Core8051的支持范围,使得开发便携嵌入应用的设计人员能够充分利用基于8051处理器的强大的开发生态系统和丰富的代码资源,并全面发挥Actel FPGA的灵活性优势。

2019-09-24 07:45:20

控制单元,调试系统以及标准的存储映射。嵌套中断向量控制器(Nested Vector Interrupt Controller,简称NVIC)是Cortex-M3处理器中一个比较关键的组件,它为基于Cort

2021-07-16 06:33:15

2.1STM32F103xx增强型LQFP48引脚分布2.2 STM32F103xx概述2.2.1ARM®的Cortex™-M3核心并内嵌闪存和SRAMARM的Cortex™-M3处理器是最新一代

2021-08-11 07:03:10

MSM8940处理器是什么?MSM8940处理器有哪些特点?

2021-11-09 07:09:11

什么是MT7628处理器呢?MT7628处理器有哪些特点呢?

2021-11-09 06:13:35

RK3188处理器有哪些特性呢?RK3168处理器具备哪几大特点呢?RK3126处理器是什么?有何作用?

2022-02-18 07:21:37

RK3188处理器特征是什么?

2021-10-26 07:38:16

RK3399处理器与AR9201处理器有哪些不同之处呢?hi3559A处理器与RV1126处理器有哪些不同之处呢?

2022-02-21 07:29:27

S3C2410处理器通过GPD端口连接LED1-4四个灯,试着画出其威廉希尔官方网站

连接图,并变成实现其逐一点亮功能。

2016-11-23 21:50:59

FPGA处理数据的时间,所以整个系统实现了流水线操作。1 系统的总体设计系统硬件主要由信号采集模块、FIFO、FPGA和SEP3203处理器组成。信号采集模块主要包括信号接收器和A/D转换模块。接收

2019-04-26 07:00:06

流水线操作。1系统的总体设计[1-2]系统硬件主要由信号采集模块、FIFO、FPGA和SEP3203处理器组成。信号采集模块主要包括信号接收器和A/D转换模块。接收到的信号首先要通过NE5534进行

2018-12-05 10:13:09

STM32处理器的启动方式是什么?

2021-11-29 07:48:02

和预测性维护),有助于赋予HMI全新的意义,而不是仅限于实现人机交互的界面。AM62处理器能够以低功耗实现边缘器件的分析功能(挂起状态功耗低至7mW且无需特殊考虑散热设计),支持工程师灵活地在尺寸受限

2022-11-03 06:11:50

TMS320C6678处理器的性能怎么样?怎么探讨TMS320C6678处理器的VLFFT演示?

2021-04-19 10:53:46

飞思卡尔塔式系统是什么?TWR-P1025处理器模块目标应用是什么?

2021-05-25 06:36:00

的处理器体系上。本文主要完成基于Cortex-M3处理器的μC/OS-III移植,通过本次移植,加深对嵌入式操作系统原理的理解。此外,在μC/OS-III移植成功的基础上进行嵌入式应用程序开发,可以把

2020-03-31 08:19:15

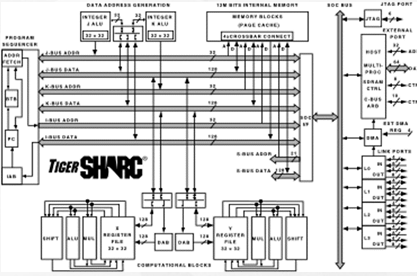

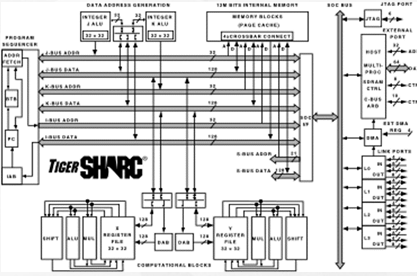

本文主要结合ADI公司的高性能ADSP-TS201的结构特点,讨论了在系统设计的过程中应该重点注意的几个问题和ADSP-TS201的外部接口技术,并给出了其与SDRAM,FPGA的连接实例,对基于TigerSHARC系列DSP的应用设计具有实用的参考价值。

2021-05-27 06:59:04

现经过测试的软件部分将会正常工作,这会节省项目后期的大量时间及努力。软硬件联合仿真系统由一个硬件执行环境和一个软件执行环境组成,通常软件环境和硬件环境都有自己的除错和控制界面,软件通过一系列由处理器启动

2008-07-17 08:56:46

类别:嵌入式系统处理器知识产权许可商ARMHoldingsplc已经成功开发出双内核Cortex-A9处理器设计(被称为Osprey)的两个实现。Cortex-A9处理器能与其他Cortex系列

2021-12-13 06:03:17

摘要:简要介绍了软硬件协同仿真技术,指出了在大规模FPGA开发中软硬件协同仿真的重要性和必要性,给出基于Altera FPGA的门级软硬件协同仿真实例。 关键词:系统级芯片设计;软硬件协同仿真

2019-07-04 06:49:19

了该采集系统的性能。笔者认为该设计方法同样适合于电力行业中其他一些实时性强、运算量大、功能复杂的多路采集分析装置中,以该设计思路替代以往的CPU+DSP,CPU+FPGA等多处理器芯片的设计方法,可实现系统级优化设计。

2013-01-22 16:41:56

本文针对高精度波形发生器的开发,进行了以AD760为核心的波形发生器的软硬件系统设计。

2021-04-12 06:54:00

如何使用KEIL进行软硬件仿真

2012-08-20 14:14:51

什么是DSP流水线协议?如何利用FPGA与ADSP TS201去设计总线接口?

2021-04-28 06:31:06

在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂算法处理上的优势,DSP+FPGA的实时信号处理系统的应用越来越广泛。那么,我们该怎么利用FPGA与ADSP TS201设计总线接口呢?

2019-08-09 06:56:11

本文将详细讲解基于Inte1的PXA255处理器的Sitsang开发平台红外模块的设计,其中包括Linux下的IrDA驱动程序的开发和基于MC68HC908AP64红外发射器的软硬件设计两个部分。

2021-04-27 06:03:57

RCC时钟树是由哪些部分组成的?如何去实现RCC系统时钟的软硬件设计呢?

2021-11-10 07:20:39

什么是软硬件协同设计呢?片上可编程系统SoPC是什么?如何去实现一种基于SoPC的软硬件协同设计呢?基于SoPC的软硬件协同设计有何功能呢?

2021-12-24 07:15:15

我们目前使用的是OMAPL138处理器,然后在处理器上运行嵌入式Linux系统;在这个平台基础上,我们希望使用蓝牙+WiFi功能。

1、请问我们可以使用什么模块进行操作?

2、考虑过WL1831mod模块,但是这个模块好像只支持AM335X系列,不支持OMAPL138处理器。

谢谢。

2018-06-21 03:55:06

新型车辆模拟驾驶训练系统的组成及工作原理是什么怎么实现动感系统的总体构想及其软硬件设计?

2021-05-12 06:15:16

介绍国家半导体公司(NS)的Geode TMGX1处理器及协同芯片,说明如何利用该芯片组进行嵌入式系统设计,并讨论一些设计难点的处理。

2019-09-05 07:30:36

RK3328处理器主要有哪些功能呢?RK3328处理器有哪些基本参数呢?怎样去搭建RK3328处理器的编译环境呢?

2022-03-09 06:50:34

:JSJK.0.2010-04-037【正文快照】:1引言可重构片上系统上包含了执行软件程序的微处理器核和实现硬件逻辑的可重构器件,因此设计人员需要通过软硬件划分来将应用所需完成的功能有效地映射到这两种类型的运算

2010-05-28 13:40:38

瑞星微3288处理器的主要硬件指标有哪些?

2022-03-03 07:29:09

和额外的性能,使得整个嵌入式系统的升级只需通过软件的升级即可实现。而8位处理器通常受到的 64K软件限制也不存在了,设计者几乎可以任意选择多任务操作系统,并将应用软件设计得复杂庞大,真正体现“硬件软件化

2016-08-08 14:52:14

ADSP-TS201的链路口程序应怎么写啊,毫无头绪啊,寄存器也看不懂,ADI公司没找到参考的链路口程序啊

2018-12-10 09:17:06

请问RISC处理器和ARM7处理器的区别在哪?求大神解答

2022-06-30 17:51:06

片上Nios Ⅱ嵌入式软核多处理器系统具有哪些优势?如何实现片上嵌入式Nios Ⅱ软核六处理器系统的设计?

2021-04-19 08:17:09

在机载SAR 的实时成像处理器中,回波信号方位向带宽以及方位向采样率不能很好的满足成像处理的要求,本文选择ADSP-TS201 处理器芯片对回波信号在成像之前对其进行方位向预处

2009-08-05 09:45:52 18

18 总体描述:ADSP-TS201S TigerSHARC处理器是-款超高性能针对大信号优化的静态超标量处理器性能处理任务和通信基础设施。数字信号处理器结合了非常宽的内存宽度和双重计块一支持浮点

2023-05-10 15:53:12

摘 要 文主要介绍了一种采用软硬件协同设计策略的用于生理信号处理的低功耗医学集成芯片。软硬件协同设计能达到性能和设计灵活性的最大化。系统硬件包括ARM7TDMI处理器,AHB兼

2010-06-19 10:29:54 24

24 描述ADSP-TS201S是TigerSHARC处理器系列中的最新款器件之一。ADI公司的TigerSHARC处理器面向众多依靠多个处理器共同工作来执行计算密集型实时功能的信号处理应用,非常适合

2024-01-26 11:33:09

介绍了一种基于ADSP-TS201的无线电测向系统。给出了系统的总体结构和工作原理,研究了MUSIC测向算法及基于零点预处理的波束合成算法,介绍了DSP模块的设计思想和程序流程图。实

2010-11-22 14:52:42 39

39 FPGA与ADSP TS201的总线接口设计

在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂

2009-12-11 10:13:29 2356

2356 特征: 处理器: 每簇由两个可以达到600MHz的ADSP-TS201 DSP处理器;整板共两簇。每个DSP可以进行3.6 GFLOPS的浮点处理能力(每个板上有4个处理器,就可以进行14.4GFLOPS的处理能力)。每个DSP芯片内有24MbitsRAM哈佛超标量体系结构; 一个用于接口连接和协处

2011-02-25 15:49:54 75

75 针对数字信号处理器的不同仿真和验证要求,提出了一种可测性软硬件协同仿真和验证平台的设计. 采用可配置IP 模块和总线结构,实现了硬件平台可配置性和可重用性;采用在线仿真模块

2011-06-09 17:54:21 39

39 为了解决 雷达信号处理 中的高速运算, 大容量存储和高速数据传输的问题, 提出采用 TS201 芯片实现雷达信号处理机设计, 利用其超高性能的处理能力和易于构造多处理并行系统的特

2011-07-20 17:20:13 65

65 数字信号处理器DSP是一种具有特殊结构的微处理器,它专门为实现数字信号处理的各种算法而设计,因而在硬件结构上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定点和浮点计算功

2011-09-21 11:59:38 1964

1964 设计并实现了一种基于ADSP TS201的组网雷达数据融合实时处理系统。主要阐述了双ADSP TS201并行处理系统的结构、算法量的估计与结果分析。系统可满足集中式组网融合和分布式组网融合

2011-10-09 10:49:40 30

30 基于ADSP_TS201S的多DSP并行系统设计

2015-12-29 17:33:04 22

22 大规模集成威廉希尔官方网站

技术的发展,作为数字信号处理的核心数字信号处理器(DSP)得到了快速的发展和应用。ADSP-TS201DSP是美国模拟器件(ADD公司继TSl01之后推出的一款高性能处理器。此系列DSP性价比很高,兼有FPGA和ASIC信号处理性能和指令集处理器的高

2017-10-20 15:01:32 0

0 ,不利于硬件的开发进度。面对这一难题,文章从FPGA 的软硬件协同测试角度出发,利用PC 机和测试硬件设备的特点,进行FPGA 的软硬件协同测试的设计,努力实现FPGA 的软硬件协调测试系统在软硬件的测试和分析中的应用。

2017-11-18 05:46:28 1616

1616 现代雷达信号处理已成为雷达功能实现的关键,本文根据某型雷达信号处理机的系统需要,对其硬件结构及软件设计做了系统优化。设计了1套以4片 TS201和1片FPGA为核心信号处理板,该系统仅用l副板卡

2017-12-11 02:21:07 1881

1881

TS201是ADI公司继ADSP-TS101之后又推出的新一代高性能Tiger-SHARC处理器,它集成了更大容量的存储器,性价比很高。它兼有ASIC和FPGA的信号处理性能和指令集处理器的高度可编程性与灵活性,适用于高性能、大存储量的信号处理和图像应用。其特点如下:

2020-08-27 09:05:59 2258

2258

模拟器件公司(Analog Devices)推出的下一代TigerSHARC处理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

ADSP-TS201 EZ-KIT Lite威廉希尔官方网站

板设计数据库

2021-04-13 12:13:17 1

1 EE-201:ADSP-TS20x TigerSHARC®处理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC®处理器IBIS文件用户指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式处理器过时数据表

2021-04-15 18:45:56 6

6 EE-205:将代码从ADSP-TS101S TigerSHARC®处理器移植到ADSP-TS201S TigerSHARC处理器的注意事项

2021-04-16 13:54:51 9

9 EE-170:评估ADSP-TS201S TigerSHARC®处理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC®处理器的散热设计

2021-04-22 09:46:01 10

10 ADSP-TS201 TigerSHARC处理器编程参考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC处理器硬件参考

2021-05-18 15:46:19 1

1 ADSP-TS101 TigerSHARC处理器硬件参考

2021-05-22 10:59:30 4

4 EE-218:为ADSP-TS201 TigerSHARC®处理器编写高效浮点FFT

2021-05-26 09:17:20 5

5 评估板上的两个ADSP-TS201S处理器和基础调试软件,以便通过基于USB、可在PC中运行的工具集进行架构评估。 利用该EZ-KIT Lite,用户可以了解有关ADI公司ADSP-TS201S硬件与软

2021-06-09 08:59:50 4

4 ADSP-TS201 EZ-KIT Lite威廉希尔官方网站

板设计数据库

2021-06-17 16:05:58 0

0 EE-201 ADSP-TS20x TigerSHARC®处理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 EE-198 ADSP-TS201S TigerSHARC®处理器IBIS文件用户指南

2021-06-18 11:13:33 2

2 软件和硬件需要定义好交互的“接口”,通过接口实现软硬件的“解耦”。例如,对CPU来说,软硬件的接口是指令集架构ISA:ISA之下的CPU处理器是硬件,指令集之上的各种程序、数据集、文件等是软件。

2022-12-07 14:23:15 1852

1852 电子发烧友网站提供《基于ADSP-TS201的着陆雷达恒虚警威廉希尔官方网站

实现.pdf》资料免费下载

2023-10-23 09:59:21 0

0 电子发烧友网站提供《TigerSHARC® ADSP-TS201S处理器的散热设计要点.pdf》资料免费下载

2023-11-29 11:12:01 0

0

电子发烧友App

电子发烧友App

评论