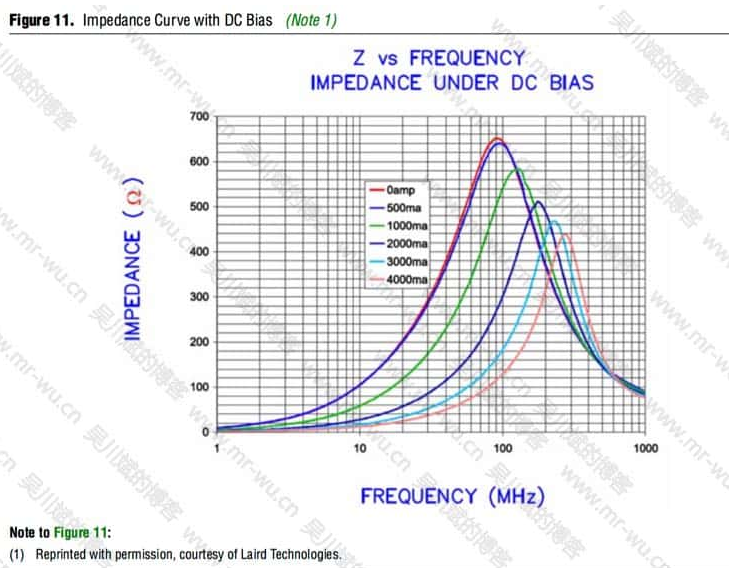

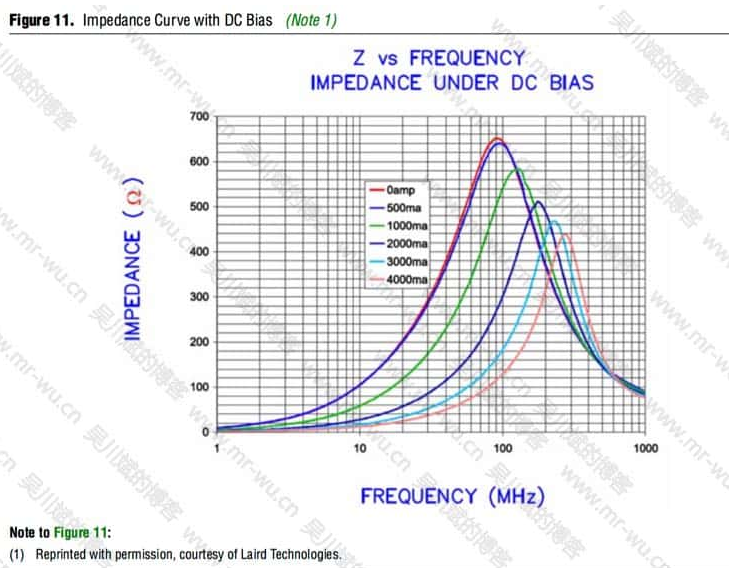

磁珠这玩意虽好,但也不能贪杯哟,硬件菌在决定服用磁珠之前,老wu建议先看看下这份 Altera 公司的铁氧体磁珠应用笔记。

2020-09-16 12:38:58 1795

1795

充分利用DSP资源,我们需要对DSP48E1有所了解。 1.DSP48E1介绍 DSP48E1是7系列的最小计算单元,DSP资源,支持许多独立的功能,其基本功能如下所示 DSP48E1简易模型 包括: 带有D寄存器的25位预加法器 25*18二进制乘法 48位累加 三输入加法 其他的一些功能还包括

2020-09-30 11:48:55 26617

26617

Kintex-7 FPGA的内部结构相比传统FPGA的内部结构嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等单元,大大提升了FPGA的性能。

2023-08-24 09:26:56 1393

1393

基于DSP+FPGA的20路 50Msps AD 数据处理平台1、板卡概述 该DSP+FPGA高速信号采集处理板由我公司自主研发,包含一片TI DSP TMS320C6455和一片Xilinx

2014-06-24 14:01:53

和Spartan-6。我无法使用任何一个软件套件编程任何设备。之前我使用Artix 100T编程了类似的设置,但似乎新的50T无法识别我的iMPACT。我也尝试添加设备,但它没有用。有没有办法更新ISE

2020-05-29 11:52:31

7 series FPGAs MultiBoot功能指让FPGA从2个或者多个BIT文件中加载一个BIT文件运行程序,本文档介绍基于个人参考设计例程K7MultiBoot的应用笔记

2019-04-05 00:25:27

模式下,48位加法器/减法器也支持双24位或双12位SIMD算术运算。在这种配置中,动态ALUMODE控制信号也支持对两个48位二进制数的按位逻辑操作。 在DSP48E1列中,级联各个DSP48E1片

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特点什么

2021-03-05 06:26:41

我正在实例化DSP切片并进行简单的乘法然后加法((A * B)+ C)。根据DSP48E1用户指南,当使用所有三个流水线寄存器时,它给出了最高频率为600 MHz。但就我而言,它使用流水线寄存器

2020-06-12 06:32:01

嗨,我有一个如下的指令:(D-A)* B + C.端口A,B,C,D与DSP48E1输入引脚相对应。我试图将整个操作打包在DSP单元中。 (顺便说一句,我的数据宽度是8位)在布局和布线完成后,我

2019-04-01 14:25:40

在我的设计中,我需要延迟一些数据(32位宽)一段时间。我一直在使用SRL16而不是FFs,它可以很好地延迟超过几个周期。我还注意到,使用DSP48E1片很容易将数据延迟到48位宽,延迟三个周期,因此

2019-04-18 06:40:33

DSP48E1属性

2021-01-27 06:21:23

和RSTB复位(如图2-7和图2-8所示)。 P端口 每个DSP48E1片都有一个48位的输出端口p。这个输出可以通过PCOUT路径内部连接(级联连接)到相邻的DSP48E1片。PCOUT连接

2020-12-23 16:54:08

ADC前端威廉希尔官方网站

的五个设计步骤(ADI应用笔记中文版)附件e0677055-d30d-4b55-9091-fe1f7b6010f7.pdf221.6 KB

2018-11-19 09:15:06

的FSMC配置的存储器接口实例,以及时序计算和硬件连接方法。本应用笔记的实例是基于STM3210E-EVAL评估版上的存储器,这是大容量STM32F10xxx的评估版。使用的存储器是一个16位的异步NOR闪存存储器,一个8位的NAND闪存存储器和一个16位的异步SRAM存储器。

2023-10-10 07:45:10

Avnet 设计的 Artix-7 50T FPGA评估套件是完全可定制的开发工具套件,非常适合嵌入式设计人员对灵活低功耗平台的需求。Artix–7 50T FPGA评估板是一套完整的系统,它把嵌入式处理器系统所需的所有功能和接口都集成到一个小小的芯片上。相关资料打包下载

2016-08-19 15:32:34

FTG256C,256个引脚的 FBGA 封装,同时包含50t和100t版本,先来一波板子照片~其中,主要的参数: 逻辑单元 Logic Cells:33280; 乘法器 DSP48:90; 可配置逻辑块 CLBs

2021-07-29 15:13:38

充分利用DSP资源,我们需要对DSP48E1有所了解。

1.DSP48E1介绍

DSP48E1是7系列的最小计算单元,DSP资源,支持许多独立的功能,其基本功能如下所示

DSP48E1简易模型

包括

2023-06-20 14:29:51

freeRTOS使用笔记一(移植篇)目录freeRTOS使用笔记一(移植篇)一,移植准备(1)从官网或者github获取源码(2)创建自己的工程目录二,开始移植(1)复制源码(2)修改工程一,移植

2022-01-27 07:49:39

,使用浏览器打开网页之后,可以在页面上实时更新当前的温度和气压。项目硬件/软件:硬件:Artix-7 50T FPGA开发板软件:Vivado2014.4项目测试环境:Chrome浏览器流程框图由于没有

2016-12-11 19:05:19

的LwIP历程“7A50T_EthernetLite_LwIP_VIV2014_4”。解压之后,在doc目录下可以看到历程的使用教程,这里就不贴图依依介绍了,文档写的比较详细。这里主要是记录一下如何把

2016-11-09 23:15:59

本帖最后由 lijuqiang000 于 2016-12-20 10:55 编辑

感谢“电子发烧友william hill官网

”和“xilinx”举办的这次Artix-7试用活动,使我有机会接触到了xilinx系列

2016-12-20 10:55:09

1600Mbps。其与FPGA的接口如下图,主要引脚有:Data[0:15],DM[0:1],DQS[0:1],Address和Control 具体的FPGA引脚分配如下图 对应FPGA中的BANK 15

2016-12-13 11:02:54

此篇先细致探索一下板卡的硬件资源。 如下图所示,主要以Artix-7 50T FPGA为核心,外围有电源管理和时钟威廉希尔官方网站

,通信、输入输出端口,和存储器。电源管理: 板卡电源输入有两种方式1) 由DC

2016-12-12 22:12:39

嵌入式开发板,有丰富的外设,如网卡,u***2uart等,上手就纯粹的接线就可以了。烙铁是用不上的,杜邦接口也不用了,感觉清爽了很多。然后非常感谢同样获取试用机会的lijinqiu1(抱歉不会@),参考他

2016-10-24 18:50:16

工程时,在器件板卡选型时,可以选择Boards面板,选择Artix-7 50T Evaluation Board板卡。无需知道FPGA芯片详细信息。5、在Block Design设计时,可以直接拖动板卡资源到设计面板中。这就是简单的LED实例化过程,在嵌入式设计时,相当方便用户使用。

2016-11-28 15:15:16

Digilent 的 PmodArtix-7 50T FPGA 评估套件 接口,支持 48 个用户 I/O 引脚 8 个用户 DIP 开关 双 10/100 以太网接口 JTAG 编程/配置端口 配对适应双倍宽度

2016-11-23 22:36:52

型号xc77a50ti-ftg256选择控制器类型为DDR3SDRAM控制器设置时钟频率400MHz,内存具体型号MT41K128M16XX-15E,电压1.5V,数据宽度16位设置输入时钟频率200MHz MIG控制器提供三种接口

2016-12-16 10:21:49

的设计维护和改进变得更为轻松。比如并没有找到artix-7 50T驱动,逛ni、Avnet、xilinx都呵呵感谢ni的技术支持回复我的邮件!!!用labview,xilinx的编译器就不要装太高的版本ba

2016-12-21 10:56:25

测试用的AIM1-AIN3 ADC采集引脚,这次用不到SCLK I2C的时钟SADDR 选择I2C器件地址,接低电平地址是 0X90D0-D7 摄像头的并行数据口FRAME_VALID 行同步信号

2016-12-15 21:44:42

模块资料多一点,在TI官网可以下载到。FPGA采用安富利的Artix-7 50T开发板,具有52160个逻辑单元、2.7Mbit BRAM以及120个DSP48 slice,还有4个速度为

2016-12-29 11:25:39

持久战,从文件大小就可以看出来--一个petalinux的安装包有7G大小。。。这是要了老命了!学校网络整改后,龟网速能吓死人,基本上是200k左右,居然还有时20k。。。完全受不了。。。基本上

2016-12-03 19:12:02

bin_file!!! 在打开硬件管理器(Hardware Manager),并连接上板卡。 在hardware面板中右击FPGA器件(xc7a50t),选择Add Configuration Memery

2016-12-27 20:22:29

了Xilinx Artix-7FPGA的基本结构和性能,在此基础上,就可以充分发挥该器件的特性,设计实用的系统了。 到此为止,关于7A50T开发板上的硬件资源就已经基本学习完成,下一节,将开始Xilinx 的FPGA开发流程的学习。 小梅哥2016年11月1日星期二于成都市电子科技大学

2016-11-01 15:52:18

收到一个白色纸箱,作为剁手party,拆快递箱那快感不用多说了,打开纸箱,一块板子,几张说明书,还有数据线等配件 相比其它搭载高端FPGA芯片的开发板,Artix-7 50T开发板算是比较迷你的,当然

2016-11-01 14:40:21

外设资源等,如下几篇博文:【Artix-7 50T FPGA试用体验】二 板卡细探(一)【Artix-7 50T FPGA试用体验】二 板卡细探(二) 一切就绪,开始上手FPGA调试和开发了,第一步

2016-12-19 08:12:39

以太网可以说是现今应用最广泛的数据通信协议之一,本篇从物理层对以太网在Artix-7 50T开发板上应用进行评测。一、原理:按照技术发展以太网可以分为:标准以太网、快速以太网、千兆以太网和万兆以太网

2016-12-13 20:07:58

LwIP在Artix-7 50T上的应用。 直接在官网上下载Artix-7 50T的LwIP参考设计,使用vivado 2014.4打开。 如下图,为系统模块图,核心是microblaze软核 具体可看如下

2016-12-14 15:56:23

接口连接到Artix-7FPGA上,从而实现了给7A50T板卡扩展16个485接口的功能。到此为止,关于通信管理机的硬件接口就已经全部搭建好了。系统框架也已经介绍完毕,下一步,该搭建该系统了。

2016-12-16 10:45:36

操作系统设计起来更加的方便。而本设计采用7A50T开发板进行设计,当然不是看中了7A50T能够嵌入软核并运行网络协议,看中的是FPGA在通信协议加速上的各种优势。 为什么使用FPGA设计通信管理机我们曾经

2016-12-16 10:43:40

计(二)【Artix-7 50T FPGA试用体验】基于7A50T FPGA开发套件的工业通信管理机设计(三)AXI接口【Artix-7 50T FPGA试用体验】基于7A50T FPGA开发套件的工业

2016-12-27 10:36:50

本帖最后由 chy520cvv 于 2016-12-14 19:05 编辑

利用官方的板卡进行PetaLinux开发的好处之一就是文件资料丰富,同时会有相关支持。但是Artix-7 50T

2016-12-14 19:04:11

\2016.2\data\boards\board_parts Vivado软件安装的板卡文件下。拷贝xdc文件重启Vivado,创建工程时,在器件板卡选型时,可以选择Boards面板,选择Artix-7 50T

2016-12-16 23:19:04

IEEE1588USB-UART 接口Xilinx PC4 和 Digilent SMT2Xilinx XC7A50T-1FTG256C下面让我们开始上电吧!!网口旁边的u***口是一个虚拟串口

2016-10-19 22:42:09

,进行IIC测试~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ~~Artix-7 50T - IIC EEPROM Write/Read

2016-10-20 22:33:22

1. 拿到板子先研究一下硬件。红色的板子蛮好看。在底面有一个小模块,我估计是 JTAG下载模块。2. 去官网下载资料,地址如下:http://www.em.avnet.com/artix7

2016-11-06 16:54:52

具体型号特点 FPGA主芯片XC7A50T-1FTG256C高性能低成本FPGA器件,含高速收发器 DDR3存储器MT41K128M16JT-125:E256M字节DDR3存储器 QSPI FLASH存储器

2016-10-27 18:35:03

,Y 方向的投影数值保存下来,假如取8位宽 、,那么1个数字就是8bit*16的字符模板。2. 把这些模板矩阵存入FPGA 的内部RAM中作为标准模板库。采用8×16 bit 大小的数组作为标准模板

2016-12-19 01:19:43

本帖最后由 chy520cvv 于 2016-12-25 20:36 编辑

原本想利用PetaLinux实现嵌入式Linux在7A50T板卡上的移植,然后将之前在树莓派上做的智能语音家居的系统

2016-12-25 20:34:46

0x00000000Processor started. Type "stop" to stop processor RUNNING>E:\Artix-7 FPGA\开发板资料\7A50T

2016-10-29 15:05:43

可以用直连的方式去测试,这样就可以直接修改IP。)E:\Artix-7 FPGA\开发板资料\7A50T\7A50T

2016-10-29 20:42:56

`7A50T开发板试用报告之开箱这是我第一次接触Xilinx的板卡和软件,显得诚惶诚恐,各种新概念迎面扑来,非常担心力所不逮。然而为了感谢电子发烧友william hill官网

,感谢Xilinx,感谢安富利公司对我的信任

2016-10-22 19:33:44

。 反面二、简单测试接下来是串口测试,学生party不像老司机拿到板卡就调试串口,测试板卡的资源情况。希望以后养成这种习惯吧!我用的是串口调试助手1.3,测试数据如下:Artix-7 50T - IIC

2016-12-07 08:46:04

能够符合Xilinx最新的工具软件和器件系列,因此选择7系列FPGA作为原型平台。经朋友推荐,本开发板复杂度适中,学习开发,因此特申请使用该开发板进行学习开发相应的资料教程。本人拟从以下几个方面展开试用

2016-10-11 18:15:20

申请理由:项目描述:本人将使用Artix-7 50T开发板进行图像处理相关的开发测评,计划如下:1. 通过PMOD接口连接图像采集卡,图像采集卡上有模拟摄像头,通过ADC芯片将模拟信号转化为数字信号

2016-10-11 18:15:33

好的浮点数参数数据进行补偿运算,消除零偏及温漂。这其中要用到一定量的浮点运算,原本计划采用FPGA+DSP的架构,但板子面积有限。以前用过斯巴达3系列芯片的核,故决定浮点运算部分采用软核来实现,可以省掉一片DSP。

2016-10-12 09:52:40

,在此基础上设计过基于FPGA的电子琴。同时此前在电子发烧友成功申请获得过云路由和树莓派的试用,认真对待每次试用机会,认真撰写心得体会。如果获得Artix-7 FPGA的试用机会,试用进度如下:1、认真阅读

2016-11-10 12:34:54

申请理由:项目描述:1、从历程开始验证开发板的所有功能。2、使用fpga端驱动传感器(温度,气压,pm2.5等)3、完成arm端的Linux的传感器驱动开发。4、实现webservice,可以在web上查看传感器参数。

2016-10-11 18:15:58

K开发板)免费试用活动,欢迎FPGA应用开发者、高校师生和研究人员踊跃报名,申请试用!

扫描报名二维码即可立即报名!

*扫码报名参与免费试用活动

紫光同创PGL50H开发平台简介

PGL50H开发平台

2023-08-21 16:16:13

为什么BUFG驱动DSP48E1的CE会出现问题?警告:LIT:683 - DSP48E1符号“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

嗨,我想使用DSP45E1模块实现Multply-Add操作,其中一个要求是我需要DSP模块上的3级流水线。查看UG479 7系列DSP48E1 Slice用户指南(UG479) - Xilinx

2020-07-21 13:52:24

48位动态比较。这使得诸如A:B NAND C = = 0或A:B(按位逻辑)C = =模式等函数得以实现。 图2-5以非常简化的形式显示了DSP48E1片。7个OPMODE位控制X、Y和Z多路复用

2021-01-08 16:36:32

简化DSP48E1片操作

2021-01-27 07:13:57

喜据我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga设计摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的单独行。我的问题是 - 1)DSP48E

2019-04-04 06:36:56

大家好,我是Lalith kumar,我们正在使用Artix7 50t FPGA。由于板载空间限制,我们计划连接512 Mb Quad SPI / BPI闪存,用于FPGA配置以及用户数据接口。是否

2020-06-09 14:57:11

我一直在尝试将DSP48E1原语用于具有自动终端计数重置的计数器。大部分工作都很好,但我看到的一个问题是我无法让DSP48E1进行模式检测0.如果我将C输入设置为48'd0,则在P =开始时

2020-07-28 10:38:40

据我所知,乘法默认由FPGA中的DSP48E1片处理。有没有什么方法可以禁用或自定义DSP48E1元素用于自己的新算法?我的目标是使用我的乘法算法,而不是使用FPGA中的现有DSP算法。请指教。谢谢。

2020-05-04 15:22:35

,这是新型xilinx产品的基础架构,因此DSP-Slices和CLB的宽度可能相等,但我找不到确认的信息。如果有人能够提供有关7系列FPGA中CLB,DSP48E1和BRAM36K / BRAM18K之间水平关系的信息,将会非常有帮助。

2020-07-25 11:04:42

求大佬分享开源库spdlog的使用笔记

2021-12-27 06:50:03

DSP48A的SPARTAN 3A DSP FPGA之间存在什么形式的通信?它是基于公交车的吗?有仲裁吗?他们的沟通协议是什么?以上来自于谷歌翻译以下为原文What form

2019-06-28 06:19:32

/ Using_DSP48E.DSP48E_I1 / DSP48E1在站点DSP48_X3Y28上放置错误。该站点是分区拥有的私有区域组的一部分

2019-01-25 10:36:59

XC7A50T-1FGG484C FPGA可编程逻辑器件XILINX/赛灵思ALINX SoM AC7A50T,基于Artix-7 XC7A50T-1FGG484C,由FPGA + 2 DDR3

2022-06-17 17:53:59

基于Artix-7 50T FPGA开发板的近距离感应器Pmod设计示例(Vivado 2014.4 - Proximity Sensor Pmod Example Design

2016-08-03 20:40:36 52

52 Artix-7 50T FPGAEthernetLite应用实例,This example design utilizes the light-weight IP (lwIP) protocol

2016-08-04 09:04:27 201

201 Artix-7 50T FPGA开发板接口功能测试实例,This document describes a MicroBlazeTM design implemented and tested on the Xilinx Artix-7 50T Evaluation board。

2016-08-04 09:17:07 198

198 概述 Xilinx的DSP48E1模块在7系列的fpga芯片中经常被用于DSP应用当中。他能够有效提高设计的灵活性和效率,提高产品的性能。 DSP48E1支持许多独立的功能。包括:乘法

2017-02-08 01:07:12 595

595

概述 利用4个dsp48e1模块,实现四路加法器,dsp48e1模块在手册中表示比较复杂,找了两个图,可以大致看懂他的基本功能。 图1 dsp48e1端口说明 图2 简化的DSP48E1结构 软件

2017-02-08 01:10:08 473

473

作为Xlinx-FPGA的学习者,学习之路颇为坎坷。在感慨Xilinx高大上的同时不得不吐槽真贵,特别是好的开发板(在这里真诚感谢xilinx电子创新网提供的试用板)。同时高冷的Xilinx在学

2017-02-08 02:09:03 253

253

5 路琨 基于Artix-7 50T的多传感器数据融合 6 徐鹏 基于FPGA的动态视频监控(安防) 试用须知: 1、收到开发板之日起每2周必须发布一篇

2017-02-08 12:13:34 256

256 本用户指南详细介绍了Spartan®6 FPGA中DSP48A1芯片的功能。

本章提供了Spartan-6 FPGA(DSP48A1芯片)中数字信号处理(DSP)元件的技术细节。每个DSP48

2019-02-15 14:42:38 31

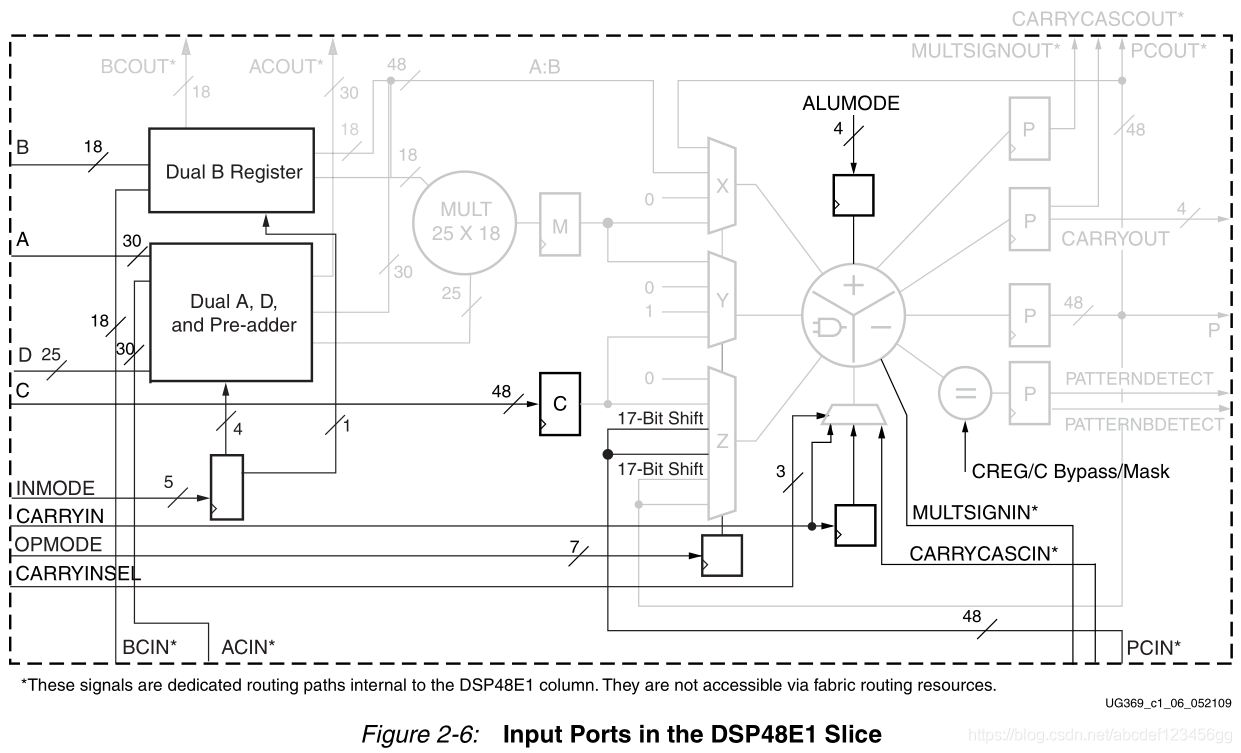

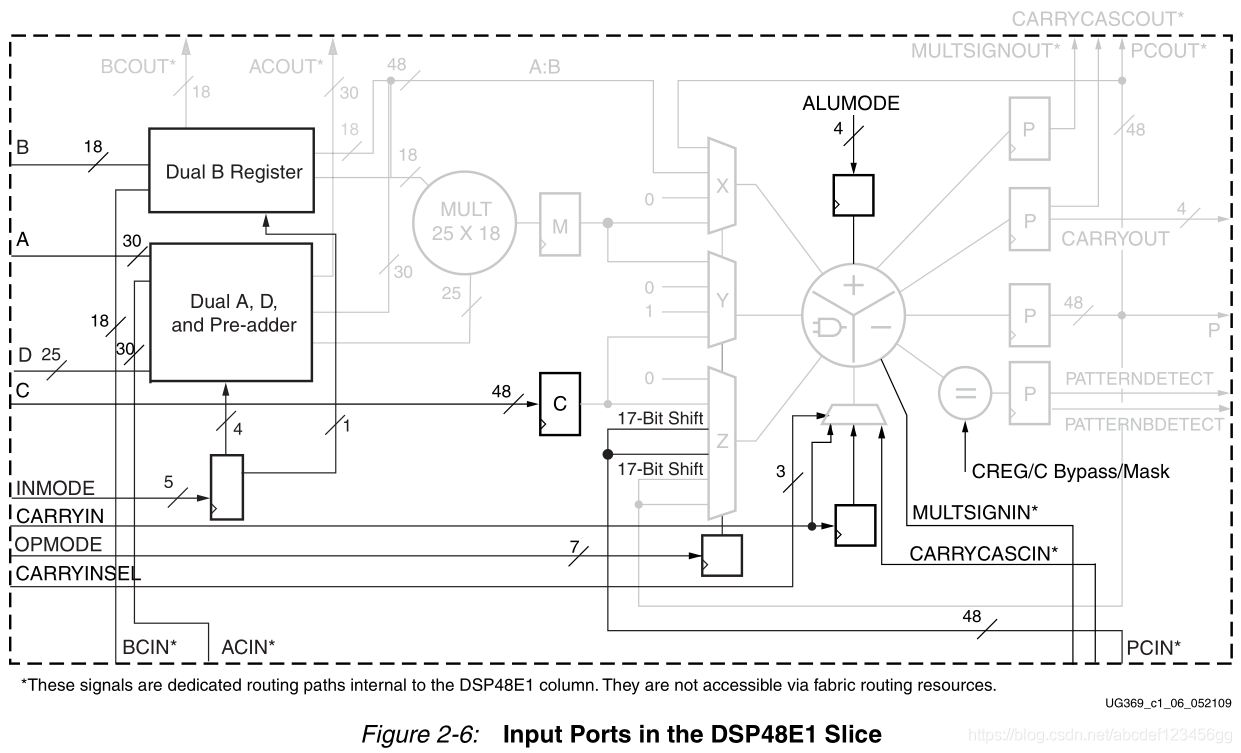

31 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2022-07-25 18:00:18 4426

4426

DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

2022-01-21 14:14:26 962

962 在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

2022-06-21 08:55:00 1882

1882 在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。

2021-01-27 07:34:32 8

8 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相应的时钟启用输入和复位输入都是保留端口。D和INMODE端口对于DSP48E1片是唯一的。本节详细描述DSP48E1片的输入端口

2021-01-27 08:18:02 2

2 DSP48E1片的数学部分由一个25位的预加器、2个25位、18位的补法器和3个48位的数据路径多路复用器(具有输出X、Y和Z)组成,然后是一个3输入加法器/减法器或2输入逻辑单元(参见图2-5)。使用2输入逻辑单元时,不能使用乘法器。

2021-01-29 08:19:37 13

13

电子发烧友App

电子发烧友App

评论