电子发烧友网站提供《完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表.pdf》资料免费下载

2024-03-13 13:58:12 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0 电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0 新唐科技,一家领先的微控制器制造商,近日宣布推出其首款支持DDR5模块的微控制器NUC1263系列。这款新品不仅具备强大的性能,还拥有独特的接口技术,旨在满足电竞市场的需求。

2024-01-30 11:02:31 326

326 STM32H750是STMicroelectronics推出的一款高性能微控制器,其特点之一是可扩展的SDRAM(同步动态随机存储器)接口。本文将详细介绍STM32H750扩展SDRAM的相关知识

2024-01-04 14:09:23 339

339

DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。

控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号

2023-12-25 14:02:58

DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。

控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号

2023-12-25 13:58:55

共模电容:又一款EMC滤波神器?(上)相信不少人是有疑问的,今天深圳市比创达电子科技有限公司就跟大家解答一下!

传统共模滤波器的局限性通常我们讨论EMC问题中的噪声及干扰,多是共模噪声、共模干扰

2023-12-25 10:53:31

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-23 09:24:37

AD9739的寄存器,发现AD9739的SYNC 控制器和RCVR控制器LOST信号拉高,不能进行正确的同步。目前观察MU控制器的同步状态一直稳定。通过接近三周的调试,还没有确定问题的原因,麻烦您帮我分析一下谢谢!

2023-12-22 08:05:12

征求一款USB控制的48路光耦开关威廉希尔官方网站

方案.vx :msg_winter

2023-12-21 15:51:04

RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理威廉希尔官方网站

16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。

2023-11-03 09:34:17 798

798

电子发烧友网站提供《基于FPGA的一种SDRAM控制器简易化设计方法.pdf》资料免费下载

2023-10-26 09:08:37 0

0 AT32 MCU SDRAM Application Note本文主要讲解AT32 SDRAM 控制器的使用。

2023-10-25 06:37:13

客户做小功率电源,目前有一款副边反激控制器型号 5L0380R目前价格处于高位,客户为了降本增效考虑国产替代,具体参数详见附件,望各位大神不另赐教!

*附件:ON-KA5L0380R.pdf

2023-10-23 17:21:16

是一款 USB3.2 Gen1X1接口的 的 4 口 口 HUB控制器 芯片, 片成 上集成 32

位 微处理器, 它具有低功耗 、 高性能 、 可配置 等特点 ;芯片 集成 USB3.0高速物

理层

2023-10-20 18:20:58

PCL6143运动控制器的原理及应用 可以用于设计开发相应的芯片威廉希尔官方网站

。介绍了PCL6143 的功能结构、主要寄存器以及指令系统。设计了一款基于PC104总线的四轴运动控制卡, 介绍了如何编写运动控制卡的功能函数库。

2023-09-26 08:14:08

电子发烧友网站提供《PIC32系列参考手册之DDR SDRAM控制器.pdf》资料免费下载

2023-09-25 11:39:59 0

0 电子发烧友网站提供《具有最大1Gb DDR2 SDRAM的SAMA5D2 SIP MPU.pdf》资料免费下载

2023-09-25 10:11:12 0

0 DDR威廉希尔官方网站

简介 RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理威廉希尔官方网站

16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。威廉希尔官方网站

控制器有如

2023-09-19 11:40:01 271

271

在这篇文章中,我们将讨论一种大电流无传感器 BLDC电机控制器威廉希尔官方网站

,该威廉希尔官方网站

不依赖于霍尔效应传感器来启动操作,而是利用电机的反电动势进行顺序输入

对于正确的换向,大多数三相 BLDC 驱动器

2023-09-14 16:09:43

本文档描述在 STM32MP1 系列 MPU 上配置 DDR 子系统(DDRSS)所需的流程和步骤。通过设定 DDR 控制器(DDRCTRL)、PHY 接口(DDRPHYC)和 SDRAM 模式

2023-09-07 07:52:24

这是DMC-500的高级概述。

DMC-500是由ARM开发、测试和许可的ARM AMBA®SoC外围设备。

它是一款高性能、面积优化的内存控制器,与AMBA 4 AXI协议兼容。

它支持以下存储设备:

·低功耗双倍数据速率3(LPDDR3)SDRAM。

·LPDDR4 SDRAM。

2023-09-04 07:05:12

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

2023-08-26 11:57:42 2050

2050 控制器是控制系统动态反应、稳定性和性能的DC-DC转换器设计中的一个关键要素。 控制器的主要功能是调节输出电压或电流, 使转换器能够用所需数量的电力提供负荷。 本节讨论控制器设计和稳定性分析,这是

2023-08-25 15:14:32 488

488 TrustZone中断控制器(TZIC)是一款高级微控制器总线架构(AMBA)兼容的片上系统(SoC)外围设备,由ARM有限公司开发、测试和授权。

TZIC为TrustZone设计中的安全中断系统

2023-08-21 06:07:52

Wavedrom 是一款功能强大且简单易用的文本转图表工具,被广泛应用于生成时序图、波形图等交互式波形。其特点在于使用简单的文本语法,使得开发人员能够以可视化的方式表示数字信号和时间序列数据

2023-08-15 12:26:34 2944

2944

PL340内存控制器是一款高性能、面积优化的SDRAM或移动SDR内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结

2023-08-12 06:25:03

PL341内存控制器是一款高性能、面积优化的DDR2 SDRAM内存控制器,兼容高级微控制器总线架构(AMBA)AXI协议。

有关AXI协议的详细说明,请参阅AMBA AXI协议规范。

本节总结了周期模型的功能与硬件的功能,以及周期模型的性能和准确性。

2023-08-12 06:01:49

我手上有一张DDR200T的开发板,板载了一块512M的SDRAM内存,板子烧了一个UX600的demosoc,我是要在这个板子跑RT-Thread。

要是想使用这块SDRAM应该怎么做呢?应该

2023-08-11 08:05:46

LPDDR2 DMC是一款符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

LPDDR2 DMC是一款高性能、区域优化的LPDDR和LPDDR2 SDRAM内存控制器,与AMBA AXI协议兼容。

2023-08-02 18:41:16

PrimeCell SDRAM控制器是一款符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

PrimeCell SDRAM控制器将SDRAM连接到嵌入式SoC ASIC和ASSP。

2023-08-02 18:13:06

控制器是一个高级微控制器总线体系结构(AMBA)主从模块,连接到高级高性能总线(AHB)。它是一款兼容AMBA的片上系统(SoC)外设,由ARM开发、测试和许可。

控制器是一种可重复使用的软IP块

2023-08-02 15:37:29

CoreLink DDR2动态存储器控制器(DMC-341)技术参考手册

2023-08-02 15:28:28

VIC是一款符合高级微控制器总线体系结构(AMBA)的片上系统(SoC)外围设备,由ARM开发、测试和许可。

VIC为中断系统提供接口,并通过两种方式改善中断延迟:

•将中断控制器移至AMBA AHB总线•为高优先级中断源提供矢量中断支持

2023-08-02 13:57:35

PrimeCell静态存储器控制器(SMC)是一款符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备,由ARM有限公司开发、测试和许可。

SMC是一个AMBA从模块,连接到高级高性能

2023-08-02 12:21:46

关于该产品是DMC-620的高级概述。

DMC-620是Arm AMBA 5芯片SoC外设,由Arm开发、测试和许可。它是一款高性能、区域优化的内存控制器,与AMBA 5 CHI协议兼容。

它支持

2023-08-02 11:55:49

DMC是由ARM开发、测试和许可的高级微控制器总线架构(AMBA)。

DMC是一种高性能、区域优化的SDRAM或移动SDR存储器控制器,与AMBA AXI协议兼容。

您可以使用多个选项配置DMC

2023-08-02 11:26:08

DMC-400是由ARM开发、测试和许可的符合高级微控制器总线架构(AMBA)的片上系统(SoC)外围设备。它是一款高性能、区域优化的内存控制器,与AMBA兼容

2023-08-02 10:28:21

这是DMC-520的高级概述。

DMC-520是由ARM开发、测试和许可的ARM AMBA 5芯片SoC外围设备。它是一款高性能、区域优化的内存控制器,与AMBA 5 CHI协议兼容。

它支持以下

2023-08-02 08:30:00

DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。

2023-07-16 15:27:10 3365

3365

电子发烧友网站提供《简单的水位开/关控制器.zip》资料免费下载

2023-07-10 15:14:12 0

0 DDR是DDR SDRAM的简称,只是人们习惯了称之为DDR,全称为Double Data Rate Synchronous Dynamic Random Access Memory,中文名为:双倍速率同步动态随机存储器,同步是指需要时钟。

2023-06-25 15:06:40 4905

4905

MS2107是一款视频和音频采集芯片,内部集成USB2.0控制器和数据收发模块、视频ADC模块、音频ADC模块和音视频处理模块。MS2107可以将CVBS、S-Vido和音频信号通过USB接口

2023-06-15 15:26:30

LTC®7820 是一款固定比例高电压高功率开关电容器 / 充电泵控制器。该器件内置 4 个 N 沟道 MOSFET 栅极驱动器以在分压器、倍压器或负输出转换器配置中驱动外部功率 MOSFET。这款

2023-06-12 10:40:35

MAX8537/MAX8539控制器为双数据速率(DDR)和组合器电源提供了一个完整的电源管理方案。MAX8537和MAX8539分别配置为反相和同相DDR电源工作模式,产生三个输出:主存储器电压

2023-06-07 11:17:02

MAX8537/MAX8539控制器为双数据速率(DDR)和组合器电源提供了一个完整的电源管理方案。MAX8537和MAX8539分别配置为反相和同相DDR电源工作模式,产生三个输出:主存储器电压

2023-06-07 11:14:43

我正在使用带有 ECC 芯片的 4GB DDR3 RAM 连接到 T1040 处理器 DDR 控制器。

我尝试了这个序列,但未能成功生成 DDR 地址奇偶校验错误:

步骤1:

ERR_INT_EN

2023-05-31 06:13:03

LTC®3870-1 是一款多相 (PolyPhase®) 降压型从属控制器,专为与 LTC 的数字电源系统管理 DC/DC 控制器进行多相运作而特别设计。通过将其自身与一个 LTC3887-1

2023-05-25 13:42:38

我使用 Wemos D1 mini 制作了一款简单但具有挑战性的游戏。

我尽量使说明尽可能详细,但如果您对此有任何疑问,请告诉我。

您所要做的就是将魔杖从电线的一端拿到另一端。它有一个 OLED

2023-05-23 06:14:41

LTC®3766 是一款具多相操作能力的副端控制器,适用于同步正激式转换器。当与 LTC3765 有源箝位正激式控制器及栅极驱动器配合使用时,该器件可造就一款完整的隔离式电源,这种电源把多相操作

2023-05-22 11:23:16

LTC®3831 是一款专为 DDR 存储器终端而设计的高功率、高效率开关稳压控制器。LTC3831 可产生一个等于 1/2 外部电源或基准电压的输出电压。LTC3831 采用同步开关架构和 N

2023-05-17 11:23:31

LTC®3717 是一款用于双倍数据速率 (DDR) 和四倍数据速率 (QDR) 存储器终端的同步降压型开关稳压控制器。该控制器采用一种谷值电流控制架构以提供非常低的占空比,并不需要使用一个检测

2023-05-17 11:20:40

LTC®3718 是一款用于 DDR 和 QDR™ 存储器终端的高电流、高效率同步开关稳压控制器。该器件采用一个低至 1.5V 的输入工作,并提供一个等于 (0.5)VIN

2023-05-17 11:13:07

LTC®3717-1 是一款用于双倍数据速率 (DDR) 和四倍数据速率 (QDR) 存储器终端的同步降压型开关稳压控制器。该控制器采用一种谷值电流控制架构,以在采用和未采用检测电阻器的情况下提供

2023-05-17 11:03:09

LTC®3776 是一款面向 DDR/QDR 存储器终端应用的两相、双输出同步降压型开关稳压控制器。第二个控制器负责将其输出电压调节至 1/2 VREF,并提供了对称的输出电压供应和吸收能力。无检测

2023-05-17 09:57:00

LTC®3876 是一款完整的 DDR 电源解决方案,可兼容 DDR1、DDR2、DDR3 及未来的较低电压 DDRX标准。LTC3876 包括 VDDQ 和 VTT DC/DC 控制器和一个高精度

2023-05-16 17:24:37

LTC®3634 是一款高效率、双通道、单片式、同步降压型稳压器,可为 DDR1、DDR2 和 DDR3 SDRAM 控制器提供

2023-05-16 17:19:38

有没有办法重置和重新初始化 DDR 控制器?DRAM 类型是 LPDDR4。

我们的目标:我们尝试为组装有不同大小 RAM 的威廉希尔官方网站

板系列实施解决方案。

为了获得可重现的结果,我们寻求在尝试下一个配置

2023-05-16 09:03:04

在使用 Imx8mp 和 rk3399proD 时,我意识到 imx 的性能优于 rk。但是如果我们比较那里的CPU配置RK比imx更强大?

2023-05-11 06:15:30

LTC®3783 是一款电流模式 LED 驱动器及升压、反激和 SEPIC 型控制器,用于驱动一个 N 沟道功率 MOSFET 和一个 N 沟道负载 PWM 开关。当采用一个外部负载开关

2023-05-06 11:27:21

的 DDR 控制器中启用 DDR 时钟的最低要求是什么。在 DDR_SDRAM_CFG 中启用 MEM_EN 时,在 DDR 时钟启动之前是否必须有一组最小的 DDR 设置,即使其余配置还不

2023-05-06 08:20:49

我们想在我们的一个物联网应用项目中使用 MIMXRT1176DVMAA。为此,我们不需要外部 SDRAM。所以,我们想在没有 SDRAM 的情况下运行这个控制器。

根据数据表,该控制器具有内部 2MB SDRAM,因此我们要使用它。

你能证实这一点吗?

2023-05-04 08:12:41

Multimedia Processor for Mobile Applications (EMMA Mobile1) DDR SDRAM Interface 用户手册 (R19UH0028EJ0500_EMMAMOBIL)

2023-04-18 19:47:17 0

0 的转起来并无法满足实际应用的需求,我们还可能面对需要解决一下问题:1)如何减少上位MCU的工作量,比如将对于电机的位置速度控制,传感器限位输入以及编码器输入下放到驱动端?如何规划好加减速轨迹曲线 使电机

2023-04-15 11:17:28

大家好,有没有简单的方法可以判断控制器在生产车间是否正常?我们可以有一些生产装置可以告诉一些产品功能是好的。我们正在寻找一些基于硬件/软件的测试,以确保 NXP 微控制器正常且未被篡改。 我们在这

2023-04-11 08:25:09

LTC®4241 是一款热插拔控制器,其允许从一个带电 PCI 总线插槽安全地进行威廉希尔官方网站

板的插拔操作。LTC4241 具有一个负责控制 4 个 PCI 电源的主控制器,和一个用于控制 3.3V 辅助

2023-04-06 13:39:24

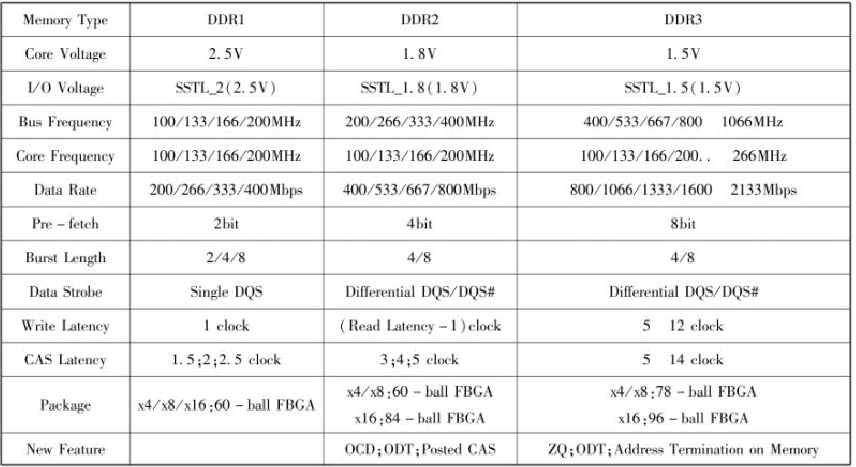

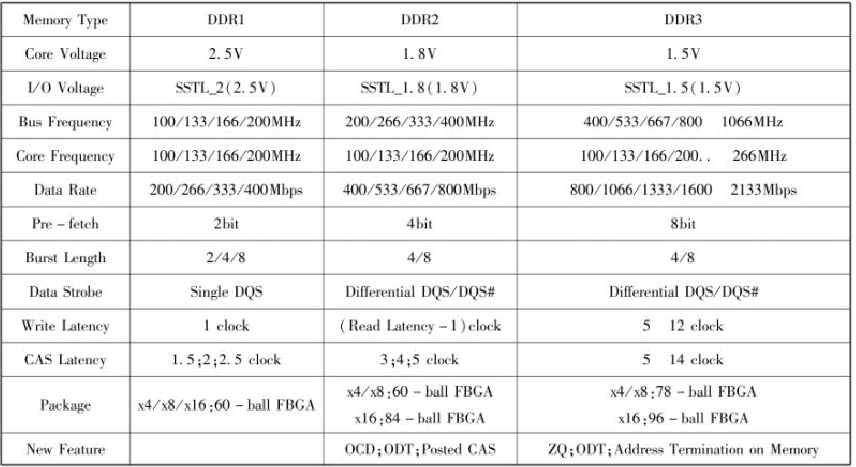

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

LT®3799-1 是一款具有功率因数校正功能的隔离型反激式控制器,专为驱动 LED 而特别设计。该控制器采用临界导通模式运作,因而允许使用一个小的变压器。这款控制器运用一种新颖的电流检测方案,能够

2023-03-31 13:42:06

LTC®4278是一款集成受电设备 (PD) 控制器和开关稳压器,拟用于高功率 IEEE 802.3at 和 802.3af 应用。凭借一个很宽的输入电压范围,LTC4278 专为支持那些包括一个

2023-03-30 11:28:45

我正在寻找一些与 IMXRT1064 的外部 SRAM 使用相关的信息。例如,EVK 有 256Mbit 166MHz SDRAM。166MHz与使用过的SDRAM有关。我试图找到 SEMC 控制器

2023-03-30 07:11:18

的操作,但我仍然无法访问内存区域。我是如何一步一步粗略地做到这一点的:初始化 DDR 控制器 1 和 2 -> 为每个控制器开启 TZC 网守 -> 应用内存区域信息 -> 设置操作

2023-03-29 07:58:56

本文档描述在 STM32MP1 系列 MPU 产品上配置 DDR 子系统(DDRSS)所需的流程和步骤。 设定 DDR 控制器(DDRCTRL)、PHY 接口(DDRPHYC)和 SDRAM 模式

2023-03-25 20:30:04 1903

1903

电子发烧友App

电子发烧友App

评论