资料下载

×

如何使用FPGA实现神经网络硬件的设计方法

消耗积分:0 |

格式:rar |

大小:0.53 MB |

2021-02-02

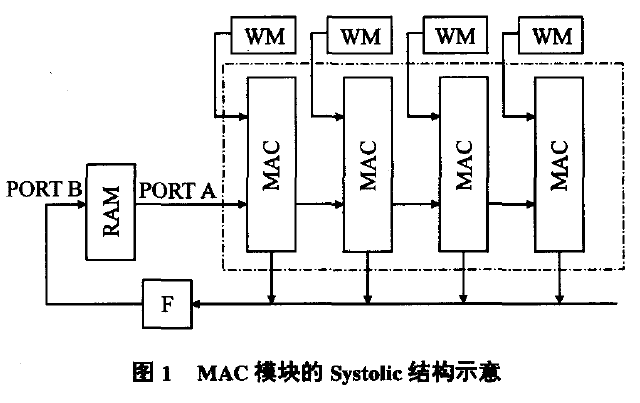

提出了一种可以灵活适应不同的工程应用中神经网络在规模、拓扑结构、传递函数和学习算法上的变化,并能及时根据市场需求快速建立原型的神经网络硬件可重构实现方法.对神经网络的可重构特征进行了分析,提出了三种主要的可重构单元;研究了可重构的脉动体系结构及BP网络到该结构映射算法;探讨了具体实现的相关问题.结果表明,这种方法不仅灵活性强。其实现的硬件也有较高的性价比,使用一片FPGA中的22个乘法器工作于100 MHz时,学习速度可达432M CUPS.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章