关于ADC的优化设计

模拟技术

描述

早在 1982 年,我在 Intel 时就第一次接触到布局生成器,大约 10% 的 GPU 是使用我编写的一些代码自动生成的。对于一名工程师来说,这是一项容易完成的任务,因为威廉希尔官方网站 是数字的,不需要优化。

在2022 年第 18 届国际合成、建模、分析和仿真方法以及威廉希尔官方网站 设计应用会议的 IEEE 论文中,有一篇由来自 FraunhoferIIS/EAS、MunEDA、IMST Gmbh 和德累斯顿工业大学的专家撰写的文章。接下来分享一下从他们的文章《使用基于模板的布局生成器和结构模型进行快速性能估计的多级模拟 IC 设计流程》中学到的知识。

像 ADC 这样的模拟设计要求你从晶体管级原理图开始,进行初始 IC 布局,提取寄生参数,进行仿真,然后测量性能以与规格进行比较。这个手动过程很容易理解,但它需要数周才能完成的迭代,因此必须有更好的方法。在论文中,他们描述了一种更加自动化的方法,基于三种组合技术:

基于模板的生成器

面向对象模板的寄生估计

基于模型的快速仿真

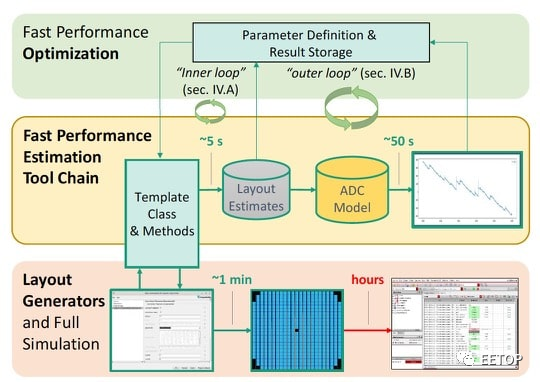

下图显示了 ADC 的优化、性能估计和布局生成器之间的交互和流程:

生成器模板、模型、性能估计

pipeline ADC 威廉希尔官方网站 有一个 SystemC AMS 模型,参数定义了器件行数等内容,而模型定义了非理想电容器的行为级描述和 OpAmp 偏移。该流程旨在执行,并在优化后达到可接受的性能标准。

内部循环在大约 5 秒内对版图寄生参数进行估计,然后在 1 分钟左右对 ADC 进行优化并生成版图。布局生成器使用最佳参数集,并生成电容器结构。对器件和导线的布局电容值进行了预表征,以便在模板方法中进行快速估算。优化步骤是使用估计的寄生参数,而不是提取的寄生参数,从而节省时间。

pipeline ADC 的 SystemC AMS 模型具有行为和结构细节,因此工程师可以在精度与运行时间之间进行权衡。使用分析模型可以在几分钟内运行一千次。外部循环添加了 ADC 模型,该运行大约需要50秒完成。

这种发生器模板方法甚至可以估计布局寄生效应、电容器变化和器件失配。全局和局部过程变化都被考虑在内。

结果

从 ADC 的晶体管级原理图开始,构建了参数化模型。拥有一个能够实现快速仿真和优化的模型,其目标是:

减少布局面积

具体布局纵横比

有效电容比误差最小

对过程变化和不匹配的鲁棒性

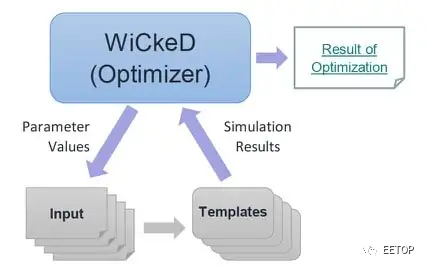

布局级优化使用了 MunEDA 的一个名为WiCkeD的 EDA 工具,它有一个循环仿真器,模板就是仿真器:

使用 WiCkeD 进行优化

由于优化器需要找到一组设计参数的性能,它要求模板对它们进行评估。优化器找到改变设计参数以改进布局的方向。评估模板需要不到 5 秒的时间,因此优化可以快速达到一组最佳布局参数。

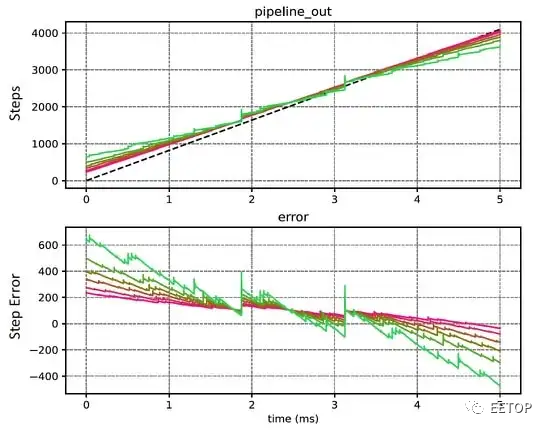

为了获得最佳的电容器阵列纵横比,他们为单元设备选择了 W 和 L 的输入参数范围,以及阵列中的行数。接下来,他们模拟了最坏情况下的性能,包括在 2 小时内使用 114 个单独参数化的偏移量。基于电容阵列中的行数和各种 W over L 值的 ADC 模型的最坏情况传递函数如下所示,其中理想曲线为虚线:

最坏情况传递函数

总结

模拟设计和优化比数字设计更难,因为其中涉及更多的相互依赖和权衡。一种具有布局生成器、基于模板的布局估计和优化的新方法已成功地用于 ADC 威廉希尔官方网站 ,它使用了来自 MunEDA 的称为 WiCkeD 的优化技术。这种方法无需花费数天到数周的时间,只需几分钟即可满足 ADC 的规范。

审核编辑:汤梓红

-

关于28335的ADC时钟问题2014-03-16 0

-

ADC优化的功率策略2018-11-05 0

-

ADC输出杂散的成因是什么?有哪些优化措施?2021-04-07 0

-

关于stm32的adc功能的例程2021-08-04 0

-

关于STM32 ADC的工作频率2021-08-04 0

-

采用ADC083000/B3000ADC芯片对ADC系统进行优化2019-05-30 4313

-

Giga ADC的架构及优化输出杂散性能的主要措施2020-09-02 2170

-

关于ADC 输入缓冲器和保护技术分析2021-05-31 5906

-

AN-1457: ADuCM3027/ ADuCM3029 集成 ADC 的性能优化2021-03-20 609

-

关于ADC芯片的选型2021-11-26 1036

-

关于STM32L系列MCU adc 测地信号不为02021-12-09 495

-

STM32ADC中断的使用注意事项和优化建议2024-01-12 3441

-

PLL抖动对GSPS ADC SNR及性能优化的影响2024-09-20 113

-

如何优化adc的采样率2024-10-31 579

全部0条评论

快来发表一下你的评论吧 !