转载地址:https://zhuanlan.zhihu.com/p/506828648

文章很详细的介绍了FPGA的基础结构,能更直观的理解内部结构原理。对深入学习很有帮助。

以下是正文:

这一段时间对 FPGA 的内部结构产生了一定的兴趣,所以找来了一本书看,这篇博客相当于是对其中相关知识点的梳理与总结, 前置知识是数字威廉希尔官方网站

逻辑 。参考书目写在了下面:

- FPGA 原理和结构:这本书是日本可重构系统研究专家写的,对 FPGA 的基本结构有非常详细的说明。

- Principles and Structures of FPGAs:这个是上面那本书的英文版。

(1)FPGA 的两个基本单元

组成 FPGA 的两个最基本的部分是组合逻辑以及时序逻辑,分别实现这两个基本部分的结构就是 FPGA 的基本单元。组合逻辑部分一般采用查找表(Look-Up-Table,LUT)的形式,时序逻辑部分一般采用触发器(Flip-Flop,FF)的形式。

1、组合逻辑的基本单元

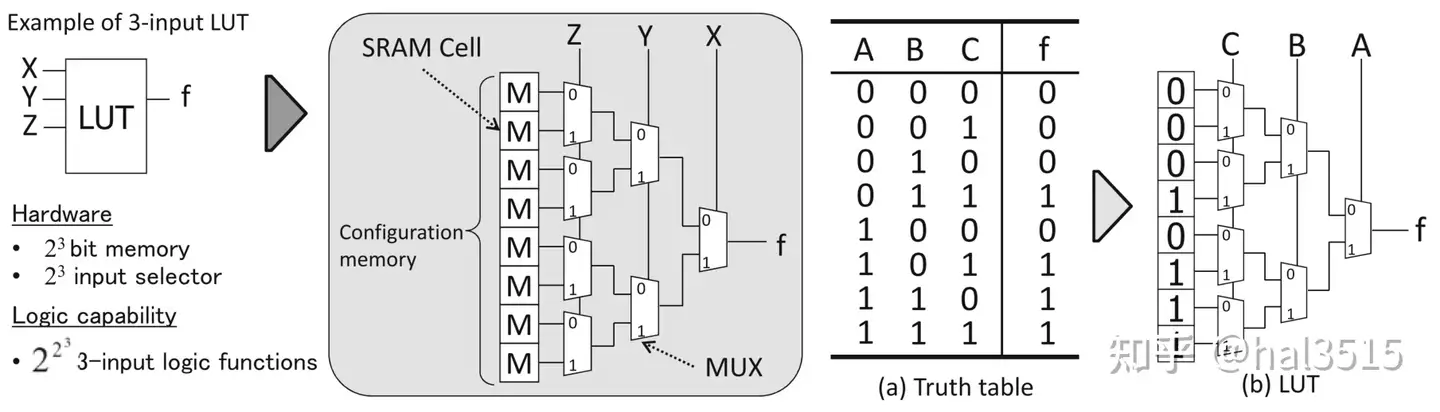

根据数电中的知识,任何一个组合逻辑都可以表示成真值表的形式(逻辑输入对应逻辑输出),也就是任意的真值表所反映的内容都能由组合逻辑实现,查找表(LUT)就能完成这个任务。

具体的过程可以参照上面这张图,左边这张图给出了一个 3 输入的查找表,可以实现任意 3 输入的逻辑函数。一般 k 输入的查找表由

个 SRAM 单元和一个 输入的数据选择器组成,可以实现 种逻辑函数。

例如:k

= 2 时为 16 种,k = 3 时为 256 种,k = 4 时为 65536 种逻辑函数。右边这张图给出 AB + AC + BC

的一个逻辑示例,使用查找表时需要先根据查找表的输入对真值表进行转换,然后将数值栏(f

栏)直接写入配置内存。当所要实现的逻辑函数的输入数比查找表的输入数多时,可以联合使用多个查找表来完成。

2、时序逻辑的基本单元

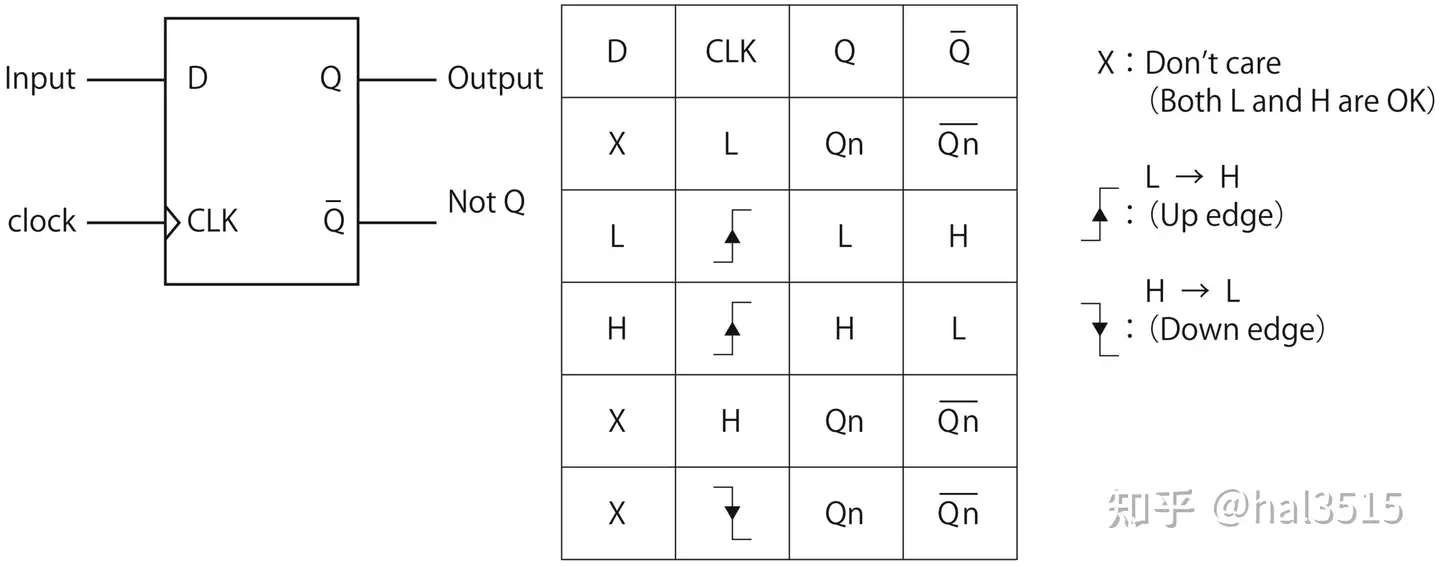

时序逻辑的基本单元采用 D 触发器,这种触发器是一种在时钟的上升沿(或下降沿)将输入信号的变化转送至输出的边沿触发器。

D-FF 的符号和真值表如上图所示,可以从真值表中看出,只有在上升沿出现时会产生输入到输出的通路,剩下的时间输出均保持不变。这里需要简单说明一下 D-FF 的原理,因为理解这件事才可以更好的理解建立时间与保持时间的概念。

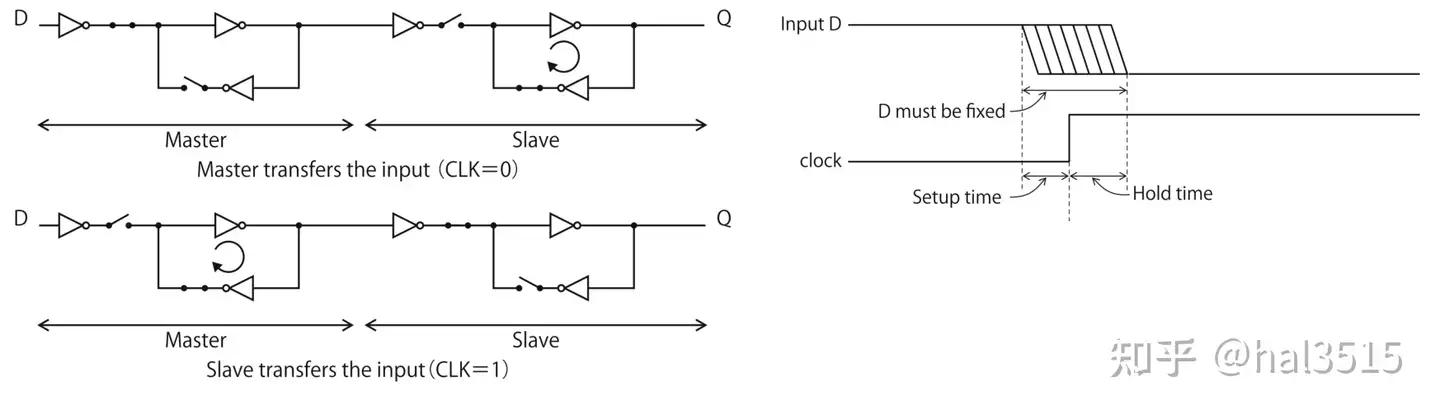

左边这张图是

D-FF 的原理图。当 CLK=0 时,主锁存器工作,将输入信号从 D 保存进来,输出信号 Q 不变;当 CLK=1

时,从锁存器工作,将主锁存器保存的信号输出到

Q,输入信号被隔断,因此不发生变化。由于这个过程中的传输门的工作不是完全理想的,因此就会需要建立时间与保持时间这两个概念。

- 建立时间(setup-time) :如果在 CLK=0 时,由于门的传输延时,输入信号没有稳定的保存到主锁存器中,那么当 CLK 从 0 变到 1,输入关闭,输出打开时,主锁存器就只能给输出端口提供一个不稳定的信号。为了避免这种情况的发生,需要输入信号在上升沿到来前已经稳定。

- 保持时间(hold-time) :当

CLK 从 0 变到

1,由于门的传输延时,门不可能立刻关闭,如果此时发生输入信号的变化,那当门关闭后实际保存的信号就可能是变化后的信号(相当于下一时刻的信号将我们需要的当前信号覆盖了)。为了避免这种情况的发生,需要输入信号在上升沿到来后保持一段时间的稳定。

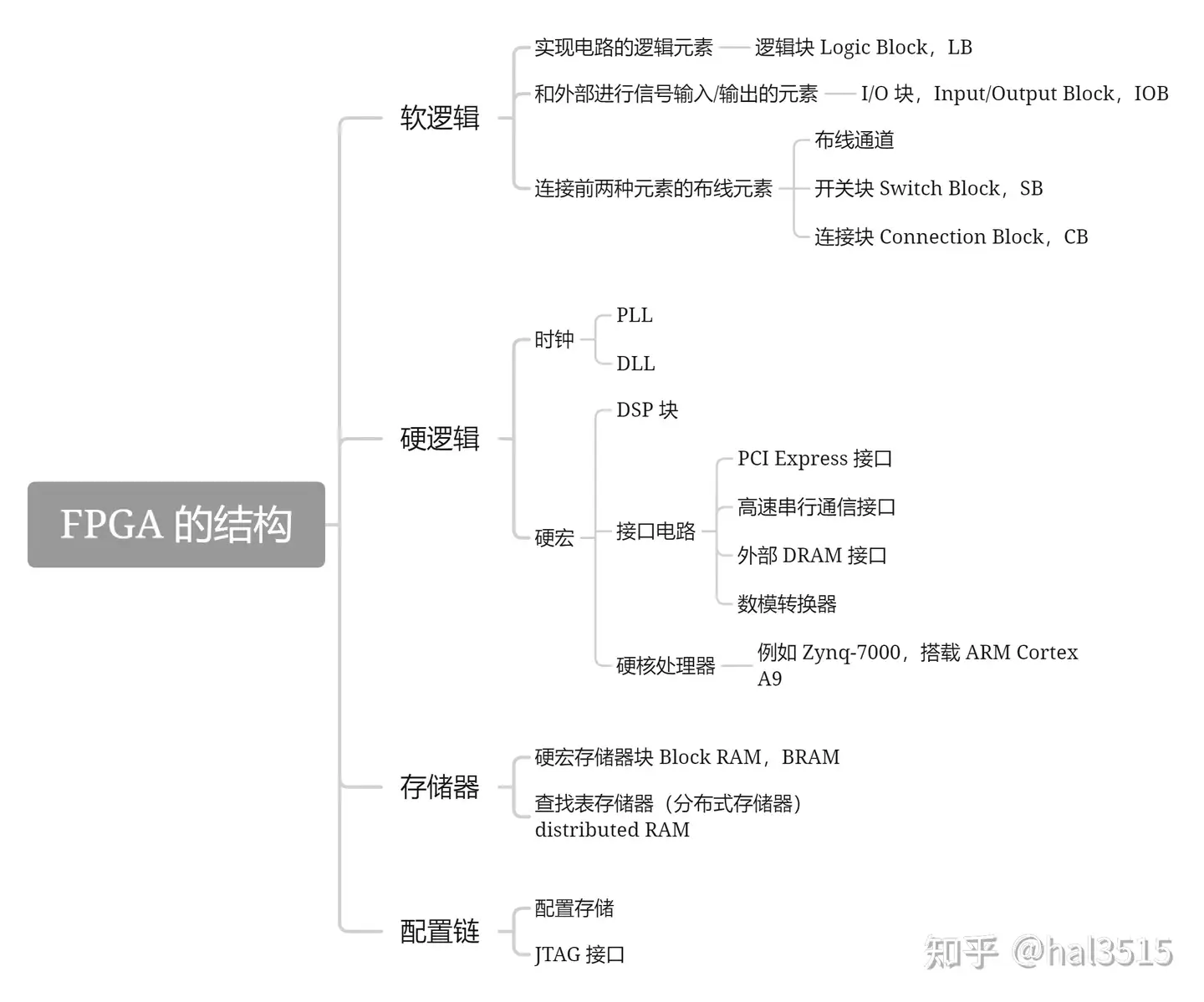

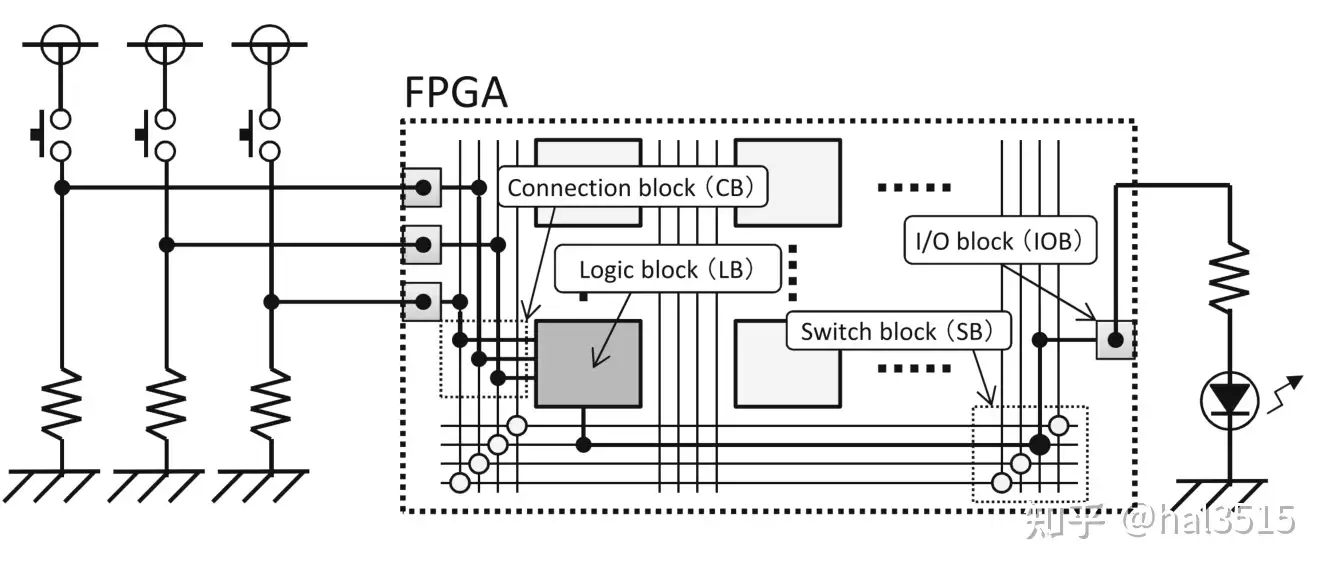

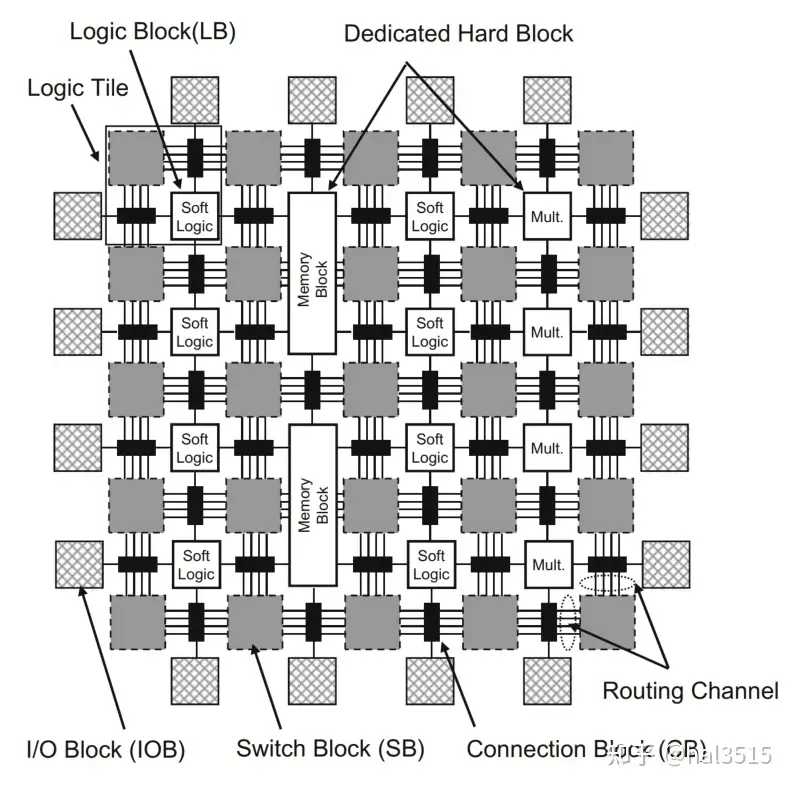

(2)FPGA 的结构

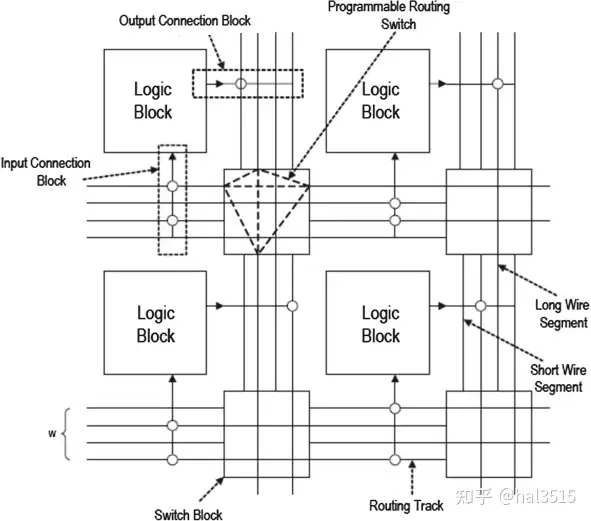

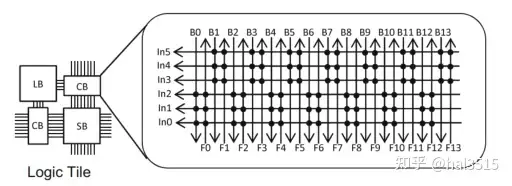

首先给出一张结构图,包含 FPGA 构成的基本要素,接下来给出两张图从宏观角度将整个 FPGA 的基本结构展示出来。图片很好理解,这里就不过多解释了,补充一点,相邻的逻辑块、连接块、开关块组成一个可重复逻辑模块(tile)。

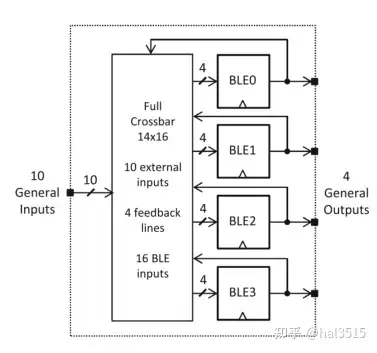

1、逻辑块的结构

大部分的逻辑块的基本要素都包含基本逻辑单元 BLE (Basic Logic Element)。BLE 由实现组合威廉希尔官方网站

的查找表,实现时序威廉希尔官方网站

的触发器,以及数据选择器构成。数据选择器在存储单元 M0 的控制下决定直接输出查找表的值还是输出 FF 中存储的值。

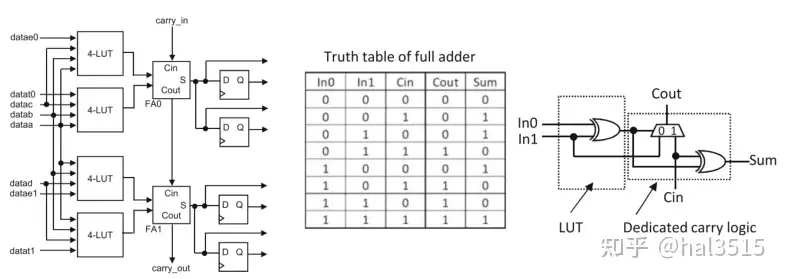

为了提高算术运算威廉希尔官方网站

的性能,FPGA 逻辑块中还包含专用的进位威廉希尔官方网站

。

左图中两个全加器(Full

Adder,FA)为专用进位逻辑,FA0

的进位输入(carry_in)连接到相邻逻辑块的进位输出(carry_out)。这条路径称为高速进位链,可以为多位算术运算提供高速的进位信号传输。右图是

Xilinx 公司 FPGA 的专用进位逻辑,Xilinx 没有设计专用的全加器威廉希尔官方网站

,而是使用查找表和进位生成威廉希尔官方网站

的组合来实现加法。

为了在不增加查找表输入数的前提下提高逻辑块的功能性,设计了逻辑簇结构。

逻辑簇的最大优势就是在增加逻辑块功能性的同时又不会大幅影响 FPGA 的整体面积。查找表的面积会随着输入 k 的增大呈指数级增长,而增加逻辑簇中 BLE 的数量 N,逻辑块的面积只按二次函数增长。

2、I/O 块的结构

I/O

块放置在芯片的外围。FPGA 的 I/O 口除了固定用途的电源、时钟等专用引脚,还有用户可以配置的用户 I/O。I/O

块具有输入/输出缓冲、输出驱动、信号方向控制、高阻抗控制等功能,可以使输入/输出信号能在 FPGA 阵列内的逻辑块和 I/O

块间按指定方式传输。I/O 块里还有触发器,可以锁存输入/输出信号。很多 FPGA 还具有应对高速通信的差分信号(Low Voltage

Difference Signaling,LVDS)等功能。

3、布线元素的结构

连接逻辑块和布线通道的连接块(CB)有输入用和输出用两种,纵向和横向布线通道的交叉处有开关块(SB)。

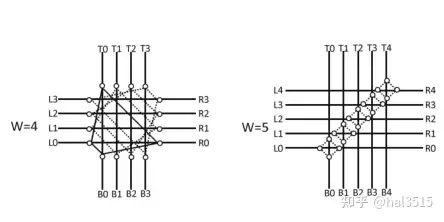

开关块位于横向和纵向布线通道的交叉处,通过可编程开关来控制布线路径。下面给出不相交型开关块的拓扑图,白色圆点相连部分有可编程开关,T0,R0,B0,L0 这四个端口之间可以相互连接,其余类似。

连接块也由可编程开关构成,其功能是连接布线通道和逻辑块的输入/输出。需要注意的是,单纯采用全交叉开关矩阵来实现,连接块的面积就会非常大,因此一般使用节省掉一些开关的稀疏矩阵来实现。上面这个示意图中的连接块由单向线组成,包括正向连线

14 根,反向连线 14 根以及 6 个逻辑块的输入。

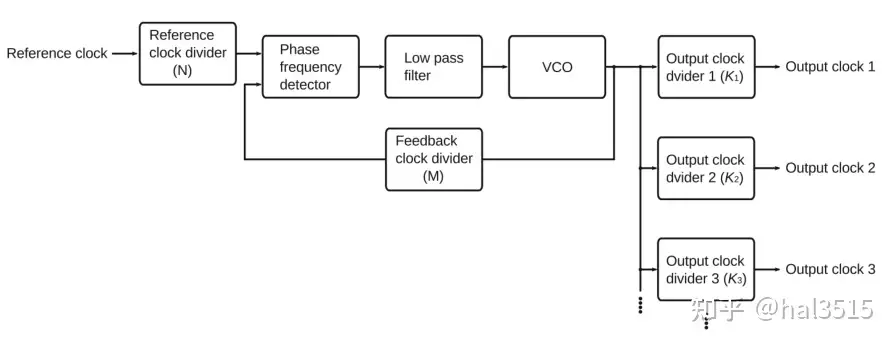

4、时钟结构

生成时钟信号的核心部分是压控传感器

VCO,VCO 是能根据所加的电压调整频率的振荡器。鉴相器可以比较外部输入的基准时钟和 VCO 自身输出时钟间的相位差。如果两个时钟一致则维持

VCO 电压;如果不一致则需要通过控制威廉希尔官方网站

对 VCO

电压进行调整,最终让输出时钟和基准时钟达到一致。为了让输出时钟的频率具有一定的选择性,因此增加参考时钟分频器 N,反馈时钟分频器

M,输出时钟分频器

,并且可以得到基准频率和输出频率的关系如下:

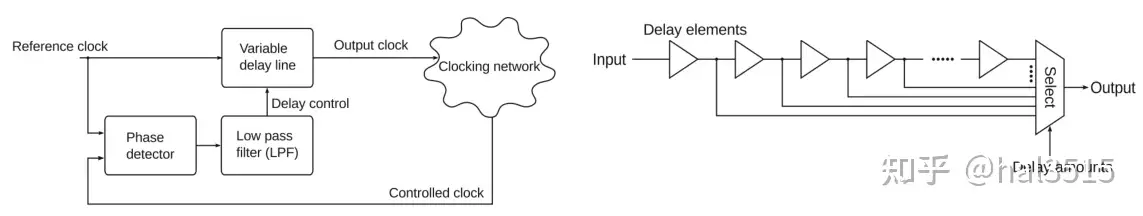

DLL

的作用是消除分配时钟与参考时钟之间存在相位差。工作原理是在参考时钟(Reference Clock)和反馈时钟(Controlled

Clock)之间插入延迟,直到两个时钟的上升边缘对齐,使两个时钟错位360度

(意味着它们是同步的)。右图是一个可变延迟线的示意图,可以通过选择器选择所需延迟量的路径,从而控制具体的延迟量。DLL

网络也可以进行分频,具体的方式与 PLL 相同。

5、存储结构

- 硬宏存储器:硬宏型存储器被称为块存储器(Block RAM,BRAM),实现方法就是以硬宏的形式在架构中嵌入存储器块。

- 查找表存储器:查找表存储器被称为分布式存储器(Distributed

RAM,分布式 RAM),使用 SLICEM 逻辑块查找表中的真值表作为小型的存储器,能实现 BRAM

不能实现的异步访问,但是一般需要小规模存储器时才采用这种方法(不能占用太多的用来实现逻辑的查找表资源)。

6、配置链

将威廉希尔官方网站

编程到 FPGA 上的过程叫做配置,向 FPGA 写入的威廉希尔官方网站

信息叫做配置数据。配置数据中包含在 FPGA 上实现威廉希尔官方网站

的所有信息,比如查找表中真值表的数据、开关块中各个开关的开闭状态等。

- 配置存储器:FPGA

需要一种在芯片上存储配置数据的机制,一般采用 SRAM 存储配置信息。优点是没有重写次数的限制,但 SRAM 是易失性存储器,断电后 FPGA

上的威廉希尔官方网站

信息会丢失。因此一般需要在芯片外部另行准备非易失存储器,在上电时自动将配置信息写入 FPGA。

- JTAG 接口: 使用 JTAG 接口进行配置时,要先将配置数据一位一位序列化,再通过边界扫描用的移位寄存器写入 FPGA。这条移位寄存器的路径就称为配置链。