相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大的影响。##LDO噪声与VCO输出相噪的关系 ##TPS7A8101输出威廉希尔官方网站

优化及对频综相噪的影响

2014-05-14 11:18:30 8141

8141 相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大

2022-08-05 10:25:00 2109

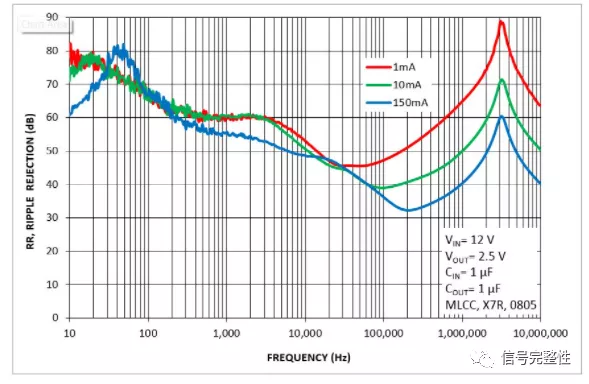

2109 在本文中,我们将介绍噪声和电源抑制比 (PSRR) 在低压差 (LDO) 稳压器中的影响。让我们简要讨论一下什么是 LDO。

2023-09-26 14:29:43 2236

2236

假设射频系统在 2.4GHz 频率下工作,那么 LDO 噪声会将 2.4GHz 上下的 VCO 噪声频谱提高至 LDO带宽。在 VCO 原始噪声图中加入图 2-1 所示的 LDO 噪声后,中心频率附近的 VCO 本底噪声等级提高。

2024-03-05 11:00:05 92

92

在本文中,我们将介绍低压差 (LDO) 稳压器中噪声和电源抑制比 (PSRR) 的影响。让我们简单讨论一下什么是 LDO。

2024-03-15 17:12:08 638

638

+12V输入,要产生+3.3、+5、+1.2、-1.2.LDO低噪线性电源芯片用哪些。求指导

2015-05-26 11:22:59

本文首先简要地介绍了LDO的噪声来源及环路稳定性对输出噪声的影响;其次,根据调频理论推导出VCO的相位噪声与LDO的噪声频谱密度的理论计算关系。在此基础上,为了验证LDO噪声对射频频综输出相噪

2019-06-20 06:57:18

在我们之前的博客中,我们谈到《低压降(LDO)稳压器之理想与现实》,介绍了什么是LDO稳压器及其噪声参数的基本信息。今天,我们将进一步详细谈谈什么是噪声,它是如何分类的,并介绍安森美半导体提供的超低噪声LDO。

2019-07-26 07:52:20

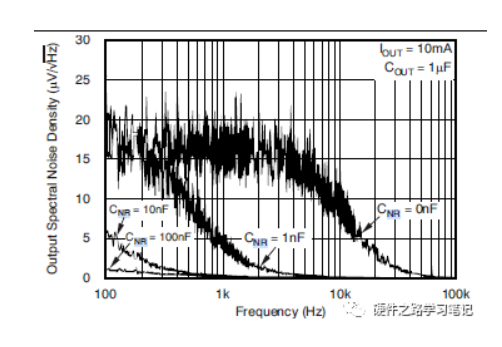

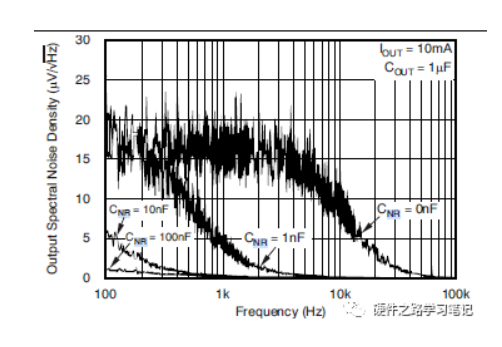

噪声电源供电时,时钟或者转换器 IC 无法达到最高性能。仅仅只是少量的电源噪声,便会对性能产生极大的负面影响。本文将对一种基本 LDO 拓扑进行仔细研究,找出其主要噪声源,并给出最小化其输出噪声的一些

2018-11-29 17:02:59

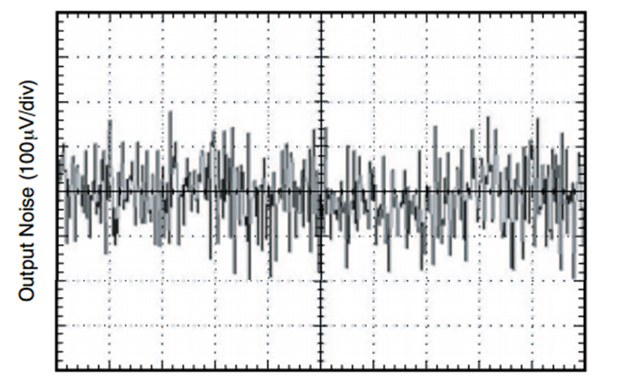

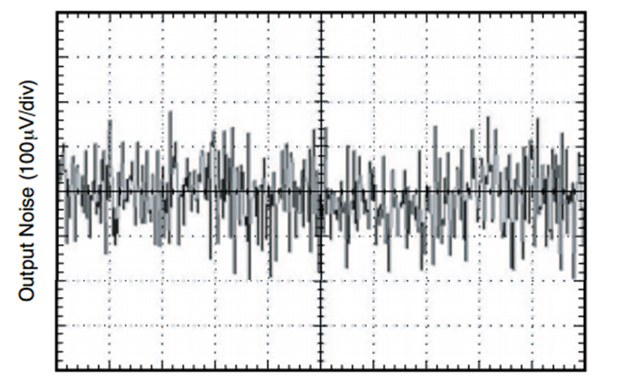

理想的LDO具备没有交流元件的电压轨。但缺点在于LDO会和其他电子设备一样生成本体噪声。图 1 显示了这种噪声在时间域中的表现。

2019-07-31 07:30:39

相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大

2019-08-21 08:04:28

现在很多集成VCO的频率合成器的设计思想,都是利用输出端加分频器来扩展输出范围。

2019-08-22 06:18:43

VCO,鉴相频率为10MHz,VCO=2.8GHz,环路滤波器按照软件默认设置(二阶),AD9517输出频率范围50MHz-300MHz。用频谱仪测量各个AD9517时钟输出管脚的频谱,发现不管时钟频率

2018-10-24 15:57:37

我在用HMC703+HMC733输出0.1-21GHz时,发现在VCO输出频率在高于18GHz后,将带宽span设置为10k时,输出信号底噪不停抖动,且输出相位噪声恶化严重,请问是什么原因造成的,LPF采用100k有源设计??

2018-08-09 07:20:32

如题。我的hmc833配置输出为50MHZ,32分频。 当输入参考为50MHz,功率为8dBm时,输出相噪在100KHZ处为-122dBc/Hz。 当输入参考为20MHz,输入功率为8dBm时,输出

2018-09-20 14:46:02

频率差是两倍中频。分析一条谱线应该是PA输出的两次谐波,另一条谱线可能是VCO的主频跟PA的两次谐波混频后再调制VCO产生的。不知道另一条谱线的分析是否正确。PA的二次谐波到VCO的通道是怎样的?或者

2021-06-24 07:32:26

的ADIsimPLL™等仿真工具则对了解环路传递函数和计算很有帮助。下面让我们依次考察一下PLL构建模块。VCO和VCO推压 电压控制振荡器将来自鉴相器的误差电压转换成输出频率。器件“增益”定义为KVCO,通常

2018-12-21 09:05:27

中心频率校准带有5 V电荷泵的外部VCO选项倍频器输出的基本VCO抑制高于20 dB内部宽带匹配射频输出在6 GHz时提供+6 dBm,在12 GHz时提供+4 dBm单端集成低噪声LDO最大鉴相器

2018-08-24 09:07:47

中心频率校准带有5 V电荷泵的外部VCO选项倍频器输出的基本VCO抑制高于20 dB内部宽带匹配射频输出在6 GHz时提供+6 dBm,在12 GHz时提供+4 dBm单端集成低噪声LDO最大鉴相器

2018-08-24 09:08:55

中心频率校准带有5 V电荷泵的外部VCO选项倍频器输出的基本VCO抑制高于20 dB内部宽带匹配射频输出在6 GHz时提供+6 dBm,在12 GHz时提供+4 dBm单端集成低噪声LDO鉴相器频率

2018-11-12 10:12:30

什么是抖动?时钟抖动有哪几种测量方法?时域测量方法和频域测量方法的原理分别是什么?TIE抖动和相噪抖动之间的关系是什么?

2021-05-08 06:32:56

Z-COMM VCO的相位噪声测量AN-109Phase Noise Measurement Of Z-COMM VCOsPublished phase noise performance can

2009-06-13 07:31:08

压电阻时候比锁相环设计时在100Hz处相噪优化10db!锁相环工作状态下,100Hz的相噪不是很稳定有6db的波动!这个是什么原因呢!adf4002和vcxo采用的一个ldo lp5912给的电,每个馈电都采用π形电感电容滤波!

2019-01-29 10:35:53

LDO。噪声分为两类:内部噪声和外部噪声。内部噪声是不可避免的,每个电子设备都会产生内部噪声。LDO由理想的源供电,这意味着它不受外界影响,因此在输入端没有外部噪声(虽然LDO在输出端确实有

2020-10-27 07:29:38

在我们之前的博客中,我们谈到《低压降(LDO)稳压器之理想与现实》,介绍了什么是LDO稳压器及其噪声参数的基本信息。今天,我们将进一步详细谈谈什么是LDO噪声?LDO噪声是如何分类的?

2019-08-01 07:20:41

LDO。噪声分为两类:内部噪声和外部噪声。内部噪声是不可避免的,每个电子设备都会产生内部噪声。LDO由理想的源供电,这意味着它不受外界影响,因此在输入端没有外部噪声(虽然LDO在输出端确实有

2018-10-30 09:04:53

分析仪或相噪分析仪则存在许多局限且需要额外的设备投资,如何协助数字领域的专业人士利用现有的数字实时示波器进行高精度的抖动分析和相噪测试?

2020-03-09 13:52:45

在从电源(无论是交流线路还是电池)到电子负载的长威廉希尔官方网站

中,低压差(LDO)线性稳压器通常需要覆盖“最后一英里”。在这里,噪声开关调节器不得不支持安静的LDO来为关键的电子负载供电。灵活的LDO(图1

2019-01-17 19:22:05

比如@100KHz处相位噪声-115dBc/Hz,过了二分频器或二倍频器后@100KHz处相噪为多少

2018-08-03 08:49:18

我有一块ADF4351的开发板,但是我现在想用相位噪声测试仪测量ADF4351的VCO开环相位噪声,但是却不知道怎样设置,如果仅仅只是将振荡器移除,测量得到的相位噪声是VCO的闭环相位噪声,有没有大神知道怎么设置才能测量VCO的开环相位噪声, 希望能够指点一二 谢谢

2018-08-02 07:46:23

NCP4688 150 mA,低噪声,LDO线性稳压器的典型应用。 NCP4688是一款CMOS 150 mA LDO线性稳压器,具有高输出电压精度,具有低噪声输出电压和高纹波抑制性能。低电平输出噪声10 Vrms通常保持在任何输出电压

2020-07-25 11:12:30

决定。也即是PLL对参考晶体噪声源呈现低通特性,而对VCO噪声呈现高通特性。因此通过常规的分频锁相方式,由于鉴相器鉴相频率较高以及噪声基底的恶化无法取得较好的相噪指标。本振相位噪声水平很高的时候,射频

2019-06-20 08:09:50

LDO是一种微功耗的低压差线性稳压器,它具有极低的自有噪声和较高的电源抑制比(PSRR)。SGM2007高性能低压差线性稳压器在10Hz至100kHz频率范围内的输出噪声为30 μV(RMS),在

2019-06-19 06:43:54

1 显示了这种噪声在时间域中的表现。图 1:有噪声电源的输出噪声快照在时间域中进行分析是困难的。因此,有两个主要方法来检验噪声:跨越整个频谱,和作为综合值。 您可以使用频谱分析工具来识别LDO

2022-11-10 06:01:02

本文设计了一个适用于以太网物理层芯片时钟同步PLL的高宽带低噪声VCO,采用了具有良好抗噪能力的交叉耦合电流饥饿型差分环形振荡器。仿真结果表明,在同样输入噪声和环境噪声的情况下,本文的VCO中心

2021-02-25 07:39:43

典型LDO应用需要增加外部输入和输出电容器。选择对电容器稳定性方面没有要求的LDO,可以降低尺寸与成本,另外还可以完全消除这些元件。请注意,利用较低ESR的大电容器一般可以全面提高PSRR、噪声以及

2021-01-28 17:09:01

宽带VCO在坚固耐用的RoHS兼容模块中结合了低相位噪声和高输出功率

2019-09-29 14:18:47

单独仿真VCO的相位噪声时,正常出现结果,在加入LDO为其供电后,再仿真相位噪声出现如下错误:有经验的前辈们求解答!!!

2021-06-25 06:38:52

VCO,并配有输出分频器以实现更低的频率。一般而言,低VCO相位噪声取决于高VCO振荡威廉希尔官方网站

Q.高VCO威廉希尔官方网站

Q意味着VCO的小频率范围和灵敏度(Kv),这是VCO设计中的基本权衡。许多倍频程调谐VCO通过

2018-10-26 11:48:38

经常看到很多论文上面都描述电源噪声对VCO相位噪声的影响,但一直都没弄明白,电源噪声是怎么影响VCO的频率抖动的,就拿一个我最近在做的VCO威廉希尔官方网站

图来说, 电源噪声是怎么对VCO造成影响的?是由于电容

2021-06-24 06:11:40

频率的噪声比较关注时,则常常会采用相位噪声来描述。在相噪测量中,相位项可能是离散的或是随机的。所谓分散相位项,由高能量的边带信号产生,与输出信号无谐波关系。在相噪测量中表现为杂散(spur),与产生

2012-02-10 09:42:42

我用两个不同参考时钟作参考,一个8M(步进100kHz),一个8.4M(步进400kHz),实际输出的的相噪8.4M的在10kHz处会有突起的一段噪声,使得10kHz处的phase noise只有

2019-03-12 09:18:04

ADF4351使用板子上的晶振作为参考钟时输出相噪还可以,参考钟使用外接信号源时输出相噪变差很多,这是怎么回事?怎么解决???晶振和信号源输出参考钟的相噪差不多

2018-07-30 06:11:57

ADF4351输出,相噪远不及器件参考值理想。而且在离中心频率最近处的杂散出现在偏离中心频率5KHz的地方。从频谱来分析,我估计如果能减小或者消除该杂散,则相噪应该可以明显变好。电源我采用了两颗

2018-09-29 15:40:47

HMC830测试相噪结果成这样,请问如何改善啊?

2019-01-10 11:49:31

什么是抖动?时钟抖动有哪几种测量方法 ?什么是相噪?测试相噪有哪几种测量方法?抖动与相噪是如何转换的?

2021-04-29 06:13:34

(如ADF4350,HMC830),与直接把这个clipped-sine wave 信号送入VCO锁出来的信号相比相噪在1K地方恶化比较明显,这个情况是正常的吗? 这个恶化是由什么引起的?buffer的抖动30fs按说不是buffer引起的恶化吧。 谢谢。

2018-08-22 09:35:21

关于ADF4350不同频点相噪相差很远的提问?现在发现ADF4350在2.871G和2.870G这里有个分界点,在2.871G频点处,相位噪声在100k的地方可以达到-105dBc/Hz,而在

2018-11-02 09:30:13

噪声敏感的应用要求采用超低噪声 LDO 稳压器

2019-08-27 14:09:03

当锁相环达到锁定状态时,VCO输出频率与参考频率相等(假设没有分频),那么它们的相位是不是相等呢?还是保持恒定的相位差呢?如果是相位相等,那么是怎么使它们的初相相等的呢?如果是保持恒定的相位差,那么

2023-04-24 11:32:51

中间层的地,不是通孔到底层地,具体见图片。请指导一下有哪些可能的原因,谢谢!A:此处是开关电源的问题,产生的70KHz叠加到主频上去了,通过增加电源滤波得到改善,相噪指标一般,还可以考虑通过配置CP

2019-01-16 07:30:47

相位噪声是表征CW信号频谱纯度的非常重要的参数,衡量了信号频率的短期稳定度。通常所说的相噪为单边带(SSB) 相位噪声,相噪的好坏对于系统的性能至关重要!· 对于终端通信而言,如果接收机LO的相噪

2020-07-01 11:12:45

LDO稳压器的PSRR和输出噪声在RF威廉希尔官方网站

中的选择:LDO是一种微功耗的低压差线性稳压器,它具有极低的自有噪声和较高的电源抑制比(PSRR)。SGM2007高性能低压差线性稳压器在10Hz至100kHz频率

2009-09-25 08:19:27 19

19 免调中频VCO的实现分立元件VCO能够提供足够的自由度来满足大多数系统的性能要求(调谐范围、输出功率、相位噪声、电流消耗等等)。然而,对于具有较大批量、价格敏感的

2009-02-08 11:20:10 804

804

压控振荡器已经成为当今时钟恢复威廉希尔官方网站

和频率合成威廉希尔官方网站

中不可缺少的组成部分。本文分别从压控振荡器的振荡频率和相位噪声两个角度,详细阐述影响VCO性能的因素,并提出相应

2009-05-09 12:29:42 2515

2515

三角波、方波输出的VCO威廉希尔官方网站

图

2009-07-14 17:18:18 1454

1454

RF威廉希尔官方网站

中LDO电源抑制比和噪声原理及选择

本文讨论LDO的特点以及RF威廉希尔官方网站

对LDO的电源抑制比和噪声的选择。引言便携产品电源设计需

2010-03-09 16:51:32 2157

2157

本文将对一种基本 LDO 拓扑进行仔细研究,找出其主要噪声源,并给出最小化其输出噪声的一些方法。

2012-12-27 15:23:32 55

55 低噪声LDO可为众多的模拟/RF 设计供电,包括频率合成器(PLL/VCO)、RF混频器和调制器、高速和高分辨率数据转换器(ADC和DAC)以及高精度传感器。然而,这些应用对于功能和灵敏度的要求已经开始逐步考验着传统低噪声LDO的性能极限。

2016-11-05 02:09:15 1417

1417

这个应用报告解释了LDO的噪声和PSRR之间的差异。

2018-05-23 16:36:23 13

13 相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪声往往对锁相环的近端相噪有着很大

2018-07-19 10:19:39 34

34 ADI LDO具有低輸出雜訊、高PSRR、高準確度、快速暫態響應、低壓差、小型封裝尺寸等特性。本展示顯示了ADI超低雜訊LDO如何大幅降低信號鏈中的VCO相位雜訊。

2019-07-30 06:20:00 2105

2105 的源供电,这意味着它不受外界影响,因此在输入端没有外部噪声(虽然LDO在输出端确实有内部噪声)。外部噪声是由外界影响(输入处的纹波——实际源)产生的各种噪声。输入波纹与电源抑制比(PSRR)有关。此外,还有如热和闪烁等噪声的不同

2020-09-08 10:47:00 3

3 本文首先简要地介绍了LDO的噪声来源及环路稳定性对输出噪声的影响;其次,根据调频理论推导出VCO的相位噪声与LDO 的噪声频谱密度的理论计算关系。在此基础上,为了验证LDO噪声对射频频综输出

2020-08-13 18:51:00 4

4 1.5A 负 LDO 提供快速瞬态响应、低输出噪声和精确电流限制

2021-03-20 15:39:16 9

9 宽带VCO在坚固耐用的RoHS兼容模块中结合了低相位噪声和高输出功率

2021-04-18 17:35:10 0

0 和 PSRR 低压差线性稳压器 (LDO) 为调节由较高电压输入产生的输出电压提供了一种简单方法。虽然操作简单,但其自生噪声在很多时候易与电源抑制比 (PSRR) 混淆。这两者在很多情况下统称为“噪声”,这是不恰当的。噪声是由LDO 内部威廉希尔官方网站

中的晶体管和电阻器以及外部元件产生

2021-05-13 15:35:18 3423

3423

噪声敏感型应用需要超低噪声LDO稳压器

2021-05-18 13:13:59 3

3 本威廉希尔官方网站

利用低噪声、低压差(LDO)线性调节器为宽带集成PLL和VCO供电。宽带压控振荡器(VCO)可能对电源噪声较为敏感,因此,为实现最佳性能,建议使用超低噪声调节器。图1所示威廉希尔官方网站

使用完全集成的小数

2021-06-06 11:25:50 2

2 相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。

2022-08-05 10:30:27 2559

2559 LDO基础知识:噪声 - 第1部分

2022-11-01 08:24:58 2

2 LDO基础知识:噪声 - 第2部分

2022-11-01 08:25:02 2

2 许多便携式RF产品使用压控振荡器(VCO)来产生RF载波频率。这些应用通常需要高于主电池电源的低噪声VCO电源电压。通常使用为低噪声线性稳压器供电的 DC/DC 转换器。不幸的是,此解决方案有几个缺点。DC/DC转换器往往会产生可能不会被稳压器抑制的噪声,从而导致稳压器输出噪声远远大于热噪声水平。

2023-03-07 15:20:04 486

486

在一篇LDO基础知识博文中,我讨论了使用低压差稳压器(LDO)过滤因开关模式电源导致的纹波电压。然而,这不是获得净化直流电源唯一要考虑的事情。因为LDO是电子设备,它们自身也会生成一定数量的噪声

2023-03-30 09:43:15 936

936

那么我们如何测量噪声呢?如前所述,内部噪声是由输入端有理想源的 LDO 产生的噪声。在实际测量中,这个理想的源可能是电池,它比 LDO 稳压器具有更低的内部噪声。

2023-06-06 09:52:38 830

830 相位噪声是VCO的核心指标,衡量了输出信号频谱的纯净程度。研究相位噪声的来源和形成机制,对VCO设计与优化有着重要的意义。

2023-07-06 14:42:08 1036

1036

LDO噪声源与降低噪声方式

2023-07-25 08:56:49 1330

1330

频率的比例决定了锁定的频率倍数,因此对于VCO的频率稳定性要求比较高。 2. 延迟:VCO的输出延迟对于PLL系统的工作非常重要。如果VCO的输出延迟太大,则可能会导致锁定时间变长或者无法锁定。 3. 噪声:VCO的输出噪声会影响PLL系统的性能和稳定性。因此,要求VCO的输出噪声较

2023-10-30 10:46:44 358

358 揭秘什么是LDO噪声

2023-12-07 16:05:20 236

236

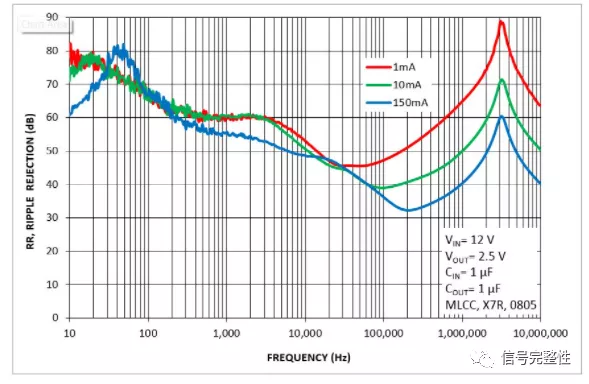

您可以使用频谱分析工具来识别LDO输出线路中的各种交流元件。(应用,“如何测量LDO噪声,”介绍了丰富的噪声测量知识。) 图 2 绘制了1A低噪声LDO TPS7A91的输出噪声。

2024-01-18 15:50:48 237

237

。

。

电子发烧友App

电子发烧友App

评论