在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 5317

5317

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 3278

3278

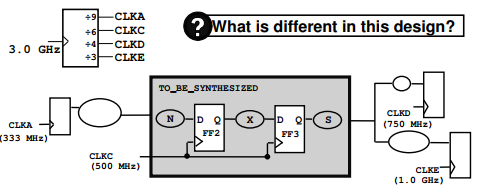

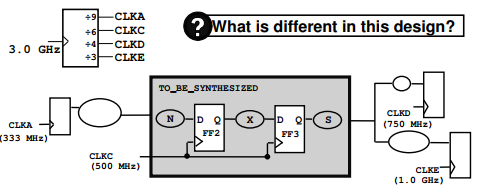

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期

2020-11-23 13:08:24 3565

3565

当这些时钟一启动,它们之间存在一个固定的相位关系,如此可以避免任何建立时间和保持时间违规。只要时钟没有漂移,就没有任何时序违规出现,并且器件会如预想那样工作。

2022-10-28 09:05:11 636

636 本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2023-12-22 09:04:46 875

875

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

FPGA设计实战演练(高级技巧):现代FPGA的结构越来越复杂,多时钟域的设计现在已是常态。对于功能威廉希尔官方网站

来说,复位结构都必不可少。在同步逻辑设计中如何很好地处理异步复位,甚至在多时钟域之间传递

2020-04-22 14:47:39

嗨,我有一个4时钟域的原始设计。在添加第5个时钟域并将设计加载到芯片中后,该设计在硬件中不再起作用。我正在使用斯巴达3E 1600这是一个很大的设计,但作为一个例子,我有一个简单的计数器,如下所示

2019-06-17 14:32:33

本人菜鸟一枚,请问FPGA中(使用verilog)ChipScope显示输入时钟信号(clk50M),报错误,如果通过pll获取其他频率比如clk40M,为什么ChipScope显示的时钟频率一直为

2017-05-09 20:31:19

FPGA的全局时钟是什么?什么是第二全局时钟?在FPGA的主配置模式中,CCLK信号是如何产生的?

2021-11-01 07:26:34

当信号在不相关或者异步时钟域之间传送时,会出现压稳态,它是导致包括FPGA 在内的数字器件系统失败的一种现象。本白皮书介绍FPGA 中的压稳态,解释为什么会出现这一现象,讨论它是怎样导致设计失败的。

2019-08-09 08:07:10

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA多时钟设计

2017-10-21 20:28:45

大型设计中FPGA 的多时钟设计策略Tim Behne 软件与信号处理部经理 Microwave Networks 公司Email: timothyb@microwavenetworks.com利用

2012-10-26 17:26:43

说FPGA的实现,由于是基于触发器的设计实现,这就造成了,在布局布线时,同一时钟域但是布局相隔较远的同步器件再被相同时钟触发时,会有延时,这反映在时钟的skew(相位倾斜),为了解决这个问题,时钟树就出

2019-07-09 08:00:00

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-03-04 09:22:51

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线?

2019-08-30 08:31:41

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

FPGA的多时钟系统设计 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

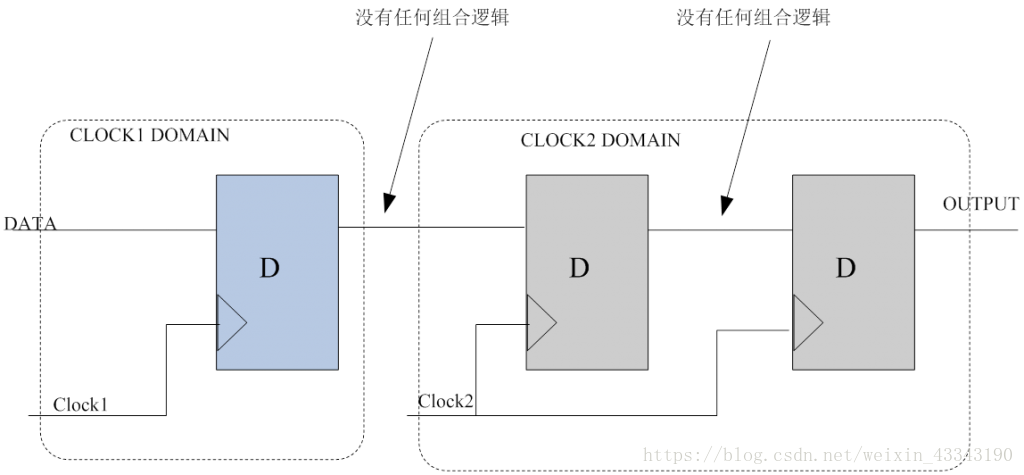

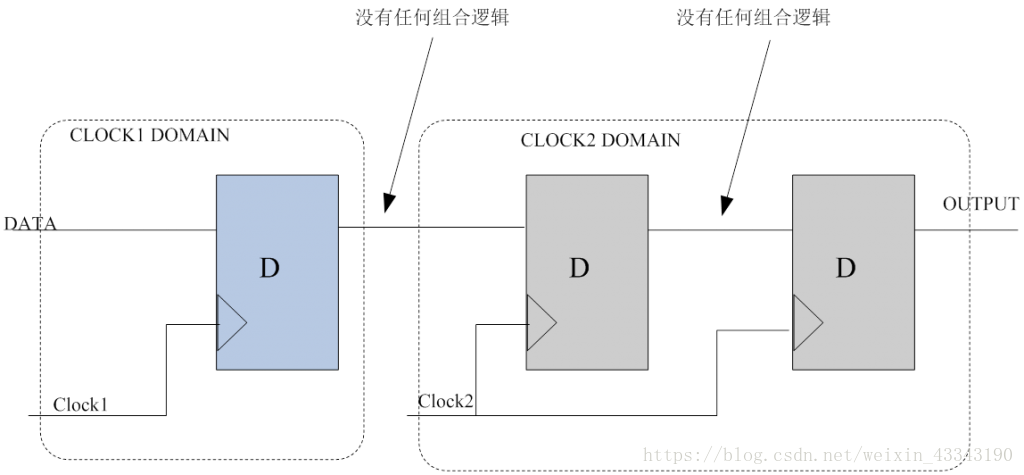

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA开发中,遇到的最多的就是异步时钟域了。[size=11.818181991577148px]检查初学者的代码,发现最多的就是这类

2014-08-13 15:36:55

(10)FPGA跨时钟域处理1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA跨时钟域处理5)结语1.2 FPGA简介FPGA(Field Programmable

2022-02-23 07:47:50

FPGA设计重利用方法(Design Reuse Methodology)SRAM工艺FPGA的加密技术大规模FPGA设计中的多点综合技术定点乘法器设计(中文)你的PLD是亚稳态吗_设计异步多时钟系统的综合以及描述技巧使用retiming提高FPGA性能

2014-04-30 23:57:42

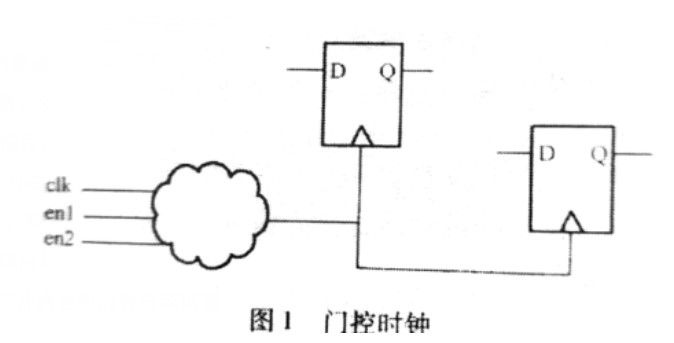

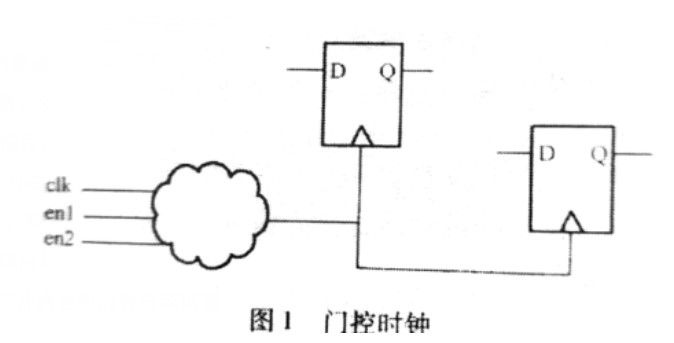

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。1.全局时钟对于一个设计项目

2012-12-14 16:02:37

时钟域威廉希尔官方网站

设计中由于不存在时钟之间的延迟和错位,所以建立条件和保持条件的时间约束容易满足。而在多时钟域里由于各个模块的非同步性,则必须考虑亚稳态的发生,如图1所示。 2 多时钟域数据传递方案 多时钟

2011-09-07 09:16:40

时钟)的逻辑。在真正的ASIC设计领域,单时钟设计非常少。2、控制信号从快时钟域同步到慢时钟域与同步器相关的一个问题是来自发送时钟域的信号可能在被慢时钟域采样之前变化。将慢时钟域的控制信号同步到快时钟域

2022-04-11 17:06:57

文章目录前言时钟及时钟域时钟,时序逻辑的心跳时钟信...

2021-07-29 07:43:44

1、IC设计中的多时钟域处理方法简析我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。跨时钟域处理技术是IC设计中非常重要的一个

2022-06-24 16:54:26

视频信号(包括数据与时钟,其中数据位宽16位,时钟1位,最高工作频率148.5MHZ).2.遇到的问题时钟相对于数据的延时,也就是信号的建立与保持时间在经过FPGA后出现偏移。造成后端的DA不能正确的采集到数据。

2014-02-10 16:08:02

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟 FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系

2012-03-05 14:42:09

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨时钟域

2021-02-21 07:00:00

60MHz的时钟上升沿变化,而FPGA内部需要使用100MHz的时钟来处理ADC采集到的数据(多bit)。在这种类似的场景中,我们便可以使用异步双口RAM来做跨时钟域处理。 先利用ADC芯片提供的60MHz

2021-01-08 16:55:23

ISE中编译为.bit文件。系统被设计为多重锁定域,其中第一个域只是获取数据并负责写入和重置共享FIFO,并且从相机计时(因此也以相同的时钟速度运行 - 大约8MHz) - 此信号用于Sys.gen。具有

2019-08-27 06:28:47

关于异步时钟域的理解的问题: 这里面的count[25]、和count[14]和count[1]算是多时钟域吧?大侠帮解决下我的心结呀,我这样的理解对吗?

2012-02-27 15:50:12

你好,我在Viv 2016.4上使用AC701板。我需要同步从一个时钟域到另一个时钟域的多位信号(33位)。对我来说,这个多位信号的3阶段流水线应该足够了。如果将所有触发器放在同一个相同的切片

2020-08-17 07:48:54

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中

2015-05-22 17:19:26

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

跨时钟域处理是什么意思?如何处理好跨时钟域间的数据呢?有哪几种跨时钟域处理的方法呢?

2021-11-01 07:44:59

时钟域转换中亚稳态是怎样产生的?多时钟域数据传递的FPGA实现

2021-04-30 06:06:32

对多时钟系统的同步问题进行了讨论å提出了亚稳态的概念及其产生机理和危害;叙述了控制信号和数据通路在多时钟域之间的传递õ讨论了控制信号的输出次序对同步技术的不同要求,重点论述了常用的数据通路同步技术----用FIFO实现同步的原理及其实现思路

2012-05-23 19:54:32

亲爱的朋友们, 我有一个多锁设计。时钟为50MHz,200MHz和400Mhz。如果仅使用400MHz时钟并使用时钟使能产生200Mhz和50Mhz时钟域。现在我需要将信号从一个时钟域传递到另一个

2019-03-11 08:55:24

跨时钟域处理是 FPGA 设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个 FPGA 初学者的必修课。如果是还在校生,跨时钟域处理也是面试中经常常被问到的一个问题。这里主要介绍三种跨

2020-10-20 09:27:37

大型设计中FPGA的多时钟设计策略利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟

2020-04-26 07:00:00

逻辑出身的农民工兄弟在面试时总难以避免“跨时钟域”的拷问,在诸多跨时钟域的方法里,握手是一种常见的方式,而Stream作为一种天然的握手信号,不妨看看它里面是如做跨时钟域的握手

2022-07-07 17:25:02

。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收

2022-10-14 15:43:00

小弟最近在研究FPGA时钟资源的手册,遇到一个问题想请教各位大神。在Virtex6系列FPGA中,Bank分为top层和bottom层,请问我怎么查看一个Bank到底是在top层还是在bottom层

2015-02-10 10:30:25

请问,想通过FPGA的PLL倍频产生个500MHz的时钟来使用,以此时钟来做定时精密延迟,不知道PLL倍频倍数有什么要求,比如好像有的器件支持不到500MHz,有没有可推荐的器件呢

补充内容 (2017-1-4 09:26):

或者有大神用过类似能到500MHz的FPGA推荐么

2017-01-03 17:04:23

1、跨时钟域信号的约束写法 问题一:没有对设计进行全面的约束导致综合结果异常,比如没有设置异步时钟分组,综合器对异步时钟路径进行静态时序分析导致误报时序违例。 约束文件包括三类,建议用户应该将

2022-11-15 14:47:59

bq1_dat稳定在1,bq2_dat也输出稳定的1。最后,从特权同学的经验和实践的角度聊一下。跨时钟域的信号同步到底需要1级还是2级,完全取决于具体的应用。如果设计中这类跨时钟域信号特别多,增加1级

2020-08-20 11:32:06

] set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]设计中fifo前端时钟域是cmos_pclk在TimeQuest

2018-07-03 11:59:59

,以及为带门控时钟的低功耗ASIC进行原型验证。本章讨论一下在FPGA设计中多时钟域和异步信号处理有关的问题和解决方案,并提供实践指导。

这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步

2023-06-02 14:26:23

Multiple Clock System Design PLD设计技巧—多时钟系统设计

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 DLL在FPGA时钟设计中的应用:在ISE集成开发环境中,用硬件描述语言对FPGA 的内部资源DLL等直接例化,实现其消除时钟的相位偏差、倍频和分频的功能。时钟威廉希尔官方网站

是FPGA开发板设计中的

2009-11-01 15:10:30 33

33 在大规模集成威廉希尔官方网站

设计中,一个系统包含了很多不相关的时钟信号,当其目标域时钟与源域时钟不同时,如何在这些不同域之间传递数据成为了一个重要问题。为了解决这个问题,

2009-12-14 10:19:07 14

14 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 645

645

1 多时钟片上网络架构的分析

片上网络结构包含了拓扑结构、流量控制、路由、缓冲以及仲裁。选择合适网络架构方面的元素,将对片上网络的性能产生重大影响[2]

2010-09-02 09:43:47 832

832

本文采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一 时钟域 (如66 MHz)的8位并行数据到另一低时

2011-08-29 11:33:44 905

905

在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 3472

3472

基于AD9540产生多时钟输出

2011-11-25 00:02:00 31

31 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1100

1100

DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 16:33:47 0

0 基于FPGA的数字时钟设计,可实现闹钟的功能,可校时。

2016-06-23 17:15:59 64

64 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

2017-11-25 09:16:01 3907

3907

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 2854

2854 时钟是FPGA设计中最重要的信号,FPGA系统内大部分器件的动作都是在时钟的上升沿或者下降沿进行。

2019-09-20 15:10:18 5065

5065

一、概述 在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以

2020-07-17 09:38:20 478

478

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20:00 2487

2487

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540产生多时钟输出

2021-03-18 23:03:12 2

2 引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。 FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-05-10 16:51:39 3719

3719

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2021-09-23 16:39:54 2763

2763 一、概述 在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以

2021-09-30 09:57:40 1533

1533

(08)FPGA时钟概念1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA时钟概念5)结语1.2 FPGA简介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (29)FPGA原语设计(差分时钟转单端时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(差分时钟转单端时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原语设计(单端时钟转差分时钟)1.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)FPGA原语设计(单端时钟转差分时钟)5)结语1.2 FPGA简介FPGA

2021-12-29 19:41:48 10

10 在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。此文内容就是阐述异步FIFO的设计。

2022-03-09 16:29:18 2309

2309 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 686

686

我们在ASIC或FPGA系统设计中,常常会遇到需要在多个时钟域下交互传输的问题,时序问题也随着系统越复杂而变得更为严重。

2023-04-06 10:56:35 413

413 当设计存在多个时钟时,根据时钟的相位和频率关系,分为同步时钟和异步时钟,这两类要分别讨论其约束

2023-04-06 14:34:28 886

886

FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

2023-05-25 15:21:31 1953

1953

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗

2023-08-23 16:10:01 336

336

电子发烧友App

电子发烧友App

评论