Video Frame Buffer IP 简介 Video Frame Buffer Read/Write IP 支持您将视频数据从存储器域(AXI4 存储器映射接口)迁移

2020-11-16 15:23:01 4834

4834

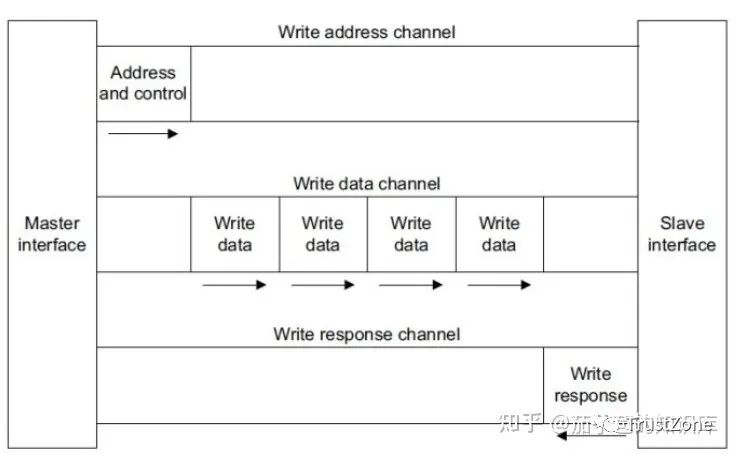

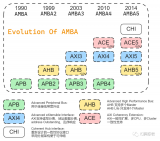

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4

2020-12-04 12:22:44 6179

6179

/ip_documentation/axi_10g_et... IP核提供一个MAC模块和一个PCS/PMA模块,PCS/PMA模块支持10GBASE-R/10GBASE-KR。客户端接口协议为AXI4 Stream

2020-12-30 12:56:30 2887

2887

赛灵思 AXI Verification IP (AXI VIP) 是支持用户对 AXI4 和 AXI4-Lite 进行仿真的 IP。它还可作为 AXI Protocol Checker 来使用。

2022-07-08 09:24:17 1281

1281 在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)。

2022-07-08 09:31:38 1945

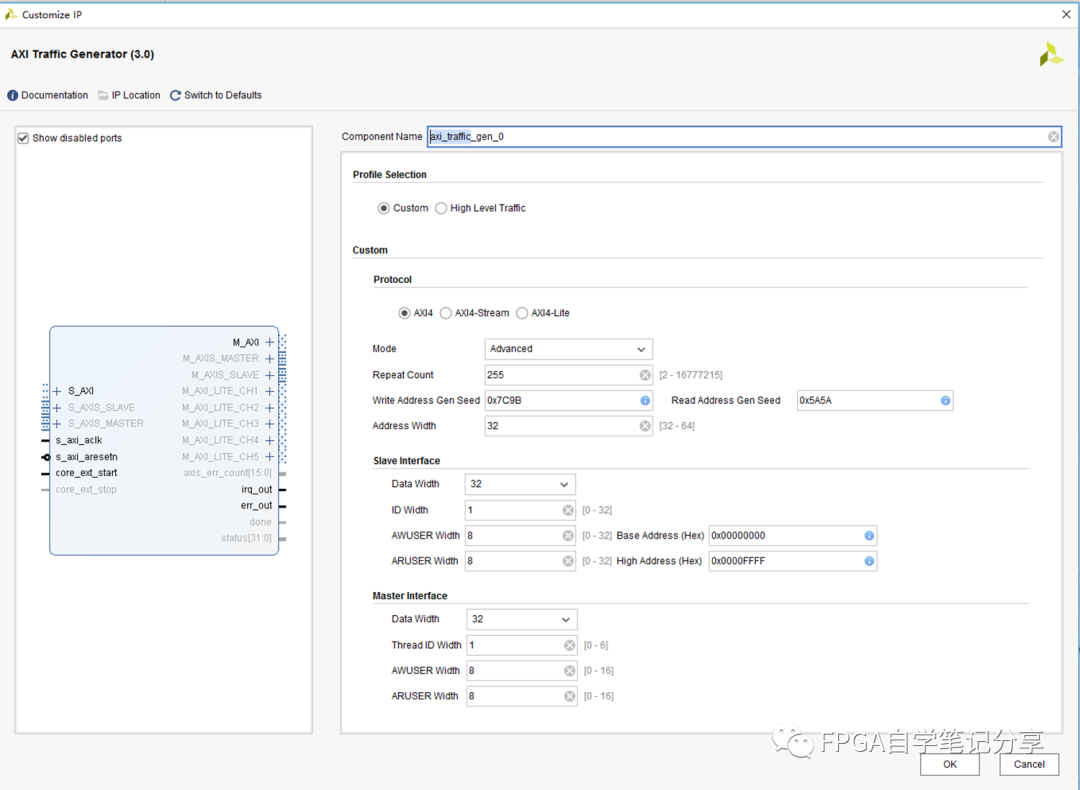

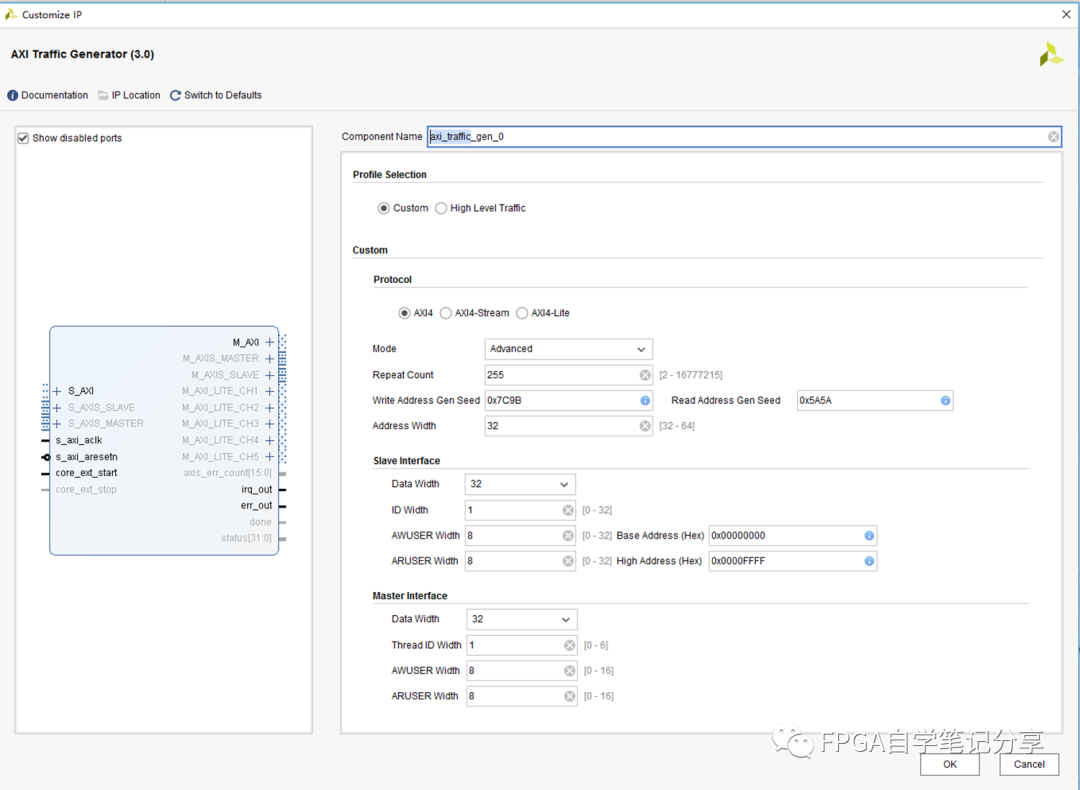

1945 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。它根据IP的编程和选择的操作模式生成各种类型的AXI事务。是一个比较好用的AXI4协议测试源或者AXI外设的初始化配置接口。

2023-11-23 16:03:45 580

580

寄存器配置最多支持4个AXI4 Master接口最多支持4个AXI4 Slave接口最多支持4个AXI4 Stream input 和Stream output接口AXI4 Master,Slave

2016-03-11 10:57:58

和功能。为了避免命名冲突,对于具有多个AXI4S输入接口的IP,信号前缀s_axis_video应该附加到s_axis_videok,其中k是各个输入AXI4S的索引;例如,对于流0

2022-11-14 15:15:13

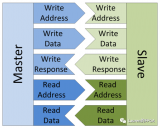

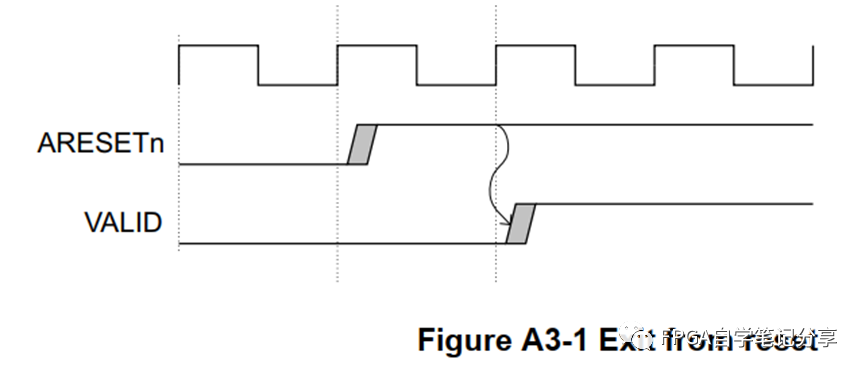

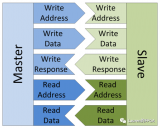

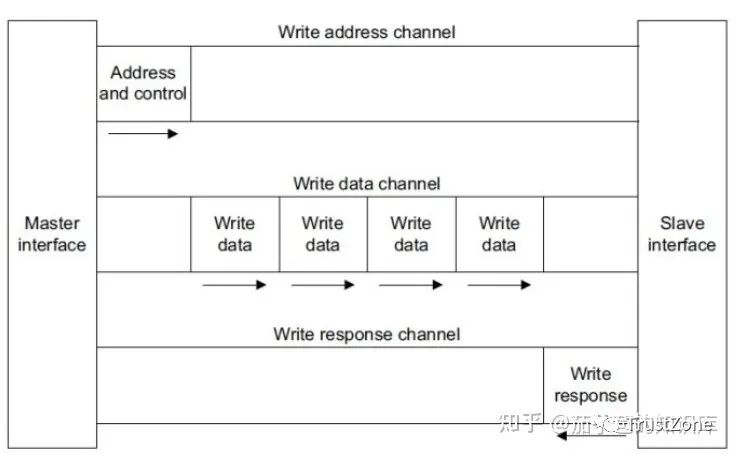

AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易

2021-01-08 16:58:24

最近在搞AXI4总线协议,有一个问题困扰了两天,真的,最后知道真相的我,差点吐血。 问题是这样的,我设置了突发长度为8,结果,读了两个轮回不到,断了,没有AWREDATY信号了,各种找,最后发现设置

2016-06-23 16:36:27

如果在仿真的时候出现可以写,可以读,但是读出来的数据一直是那么几个的问题,很有可能,你和我一样,是个马大哈了,去看DQ,是不是地址也来来去去就那么几个?是的话,可以考虑考虑你的地址的问题,AXI4

2016-06-24 16:25:38

我想知道AXI4流互连IP 2中True Round-Robin和Round-Robin仲裁方案之间的区别,特别是当所有从接口都不活动时。我已经参考了文档PG085,并提到“如果所有从接口都不活动

2020-05-20 14:51:06

Checker IP 的检测呢 ? https://www.xilinx.com/support/documentation/ip_documentation/axi_protocol_checker/v2_0

2020-02-28 13:44:01

的数据流标识符。xilinx封装的ip中没有此信号。 9.TDEST 用于提供路由信息,xilinx封装的ip中没有此信号。 10.TUSER AXI4协议留给用户自定义的。xilinx封装的ip中没有

2021-01-08 16:52:32

AXI有哪些性能?AXI的特点是什么?AXI4有哪些工作模式?

2021-06-23 08:13:52

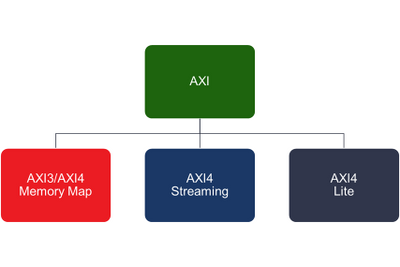

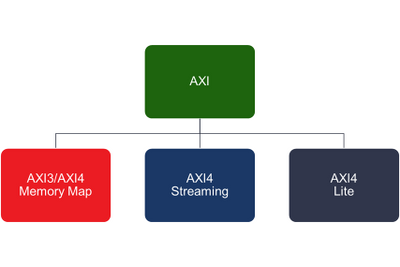

AXI 总线上面介绍了AMBA总线中的两种,下面看下我们的主角—AXI,在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:AXI4

2022-04-08 10:45:31

Axi4ReadOnlyDecoder对于Axi4读操作而言,其指令的完成由ar、r两个通道完成,相较于写操作,其通道数虽然少了一个,但也是两个方向的数据流:ar:master——>

2022-08-04 14:28:56

: xilinx.com:ip:axi_vdma:6.2 ERROR: [Common 17-39] 'create_bd_cell' failed due to earlier errors. while

2020-10-06 22:22:12

,而是接受不应该通过的其他CAN消息。我已多次阅读LogiCORE IP CAN v5.0产品指南,并检查了AFR,AFMR和AFID寄存器的设置。我正在使用CAN B(扩展ID) -J1939 CAN

2019-04-02 10:37:07

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比

2021-11-24 21:47:04

我想我在Xilinx 2015.4生成的verilog AXI组件代码中发现了一个问题。为清楚起见,我选择了“工具>创建和打包IP”,选择“创建AXI4外设”,并选中“启用中断支持”。我能够

2020-08-12 06:43:37

今天有空来学习一下xilinx的axi_iic ip。下面的链接是xilinx官网关于axi_iic的数据手册,大家点一下就可以看了pg090-axi-iic pdf数据手册先给我们这个ip的顶层

2022-01-18 07:00:13

您可以将协议断言与任何旨在实现AMBA®4 AXI4的接口一起使用™, AXI4 Lite™, 或AXI4流™ 协议通过一系列断言根据协议检查测试接口的行为。

本指南介绍SystemVerilog

2023-08-10 06:39:57

XHB将AXI4协议转换为AHB-Lite协议,并具有AXI4从接口和AHB-Lite主接口。有关AXI4事务如何通过XHB桥接到AHB-Lite的信息,请参阅第2-2页的表2-1

2023-08-02 06:51:45

can be created using Xilinx AXI IP. The use of AXI Interconnect, Memory Interface Generator (MIG

2012-01-26 18:57:03

的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。今天,首先说一下自定义AXI4的IP核,至于AXI4

2019-12-13 17:10:42

这是SoC Designer AXI4协议包的用户指南。该协议包包含SoC Designer组件、探针和ARM AXI4协议的事务端口接口(包括对AMBA4 AXI的支持)。

2023-08-10 06:30:18

或起点吗?此外,我的VHDL模块具有AXI4流接口,而其他模块具有自定义接口。如何使它们兼容?将等待有用的回复。问候

2020-05-22 09:24:26

-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP:选择Next>>选择Create AXI4 Peripheral>>

2018-01-08 15:44:39

Vivado中实现一个AXI4接口的IP核,用于对DDR3进行读写测试。本章包括以下几个部分:99.1简介9.2实验任务9.3硬件设计9.4软件设计9.5下载验证9.1简介我们在前面的实验中介绍了一些

2020-10-22 15:16:34

原子公众号,获取最新资料第十五章AXI4接口之DDR读写实验Xilinx从Spartan-6和Virtex-6系列开始使用AXI协议来连接IP核。在7系列和ZYNQ-7000 AP SoC器件中

2020-09-04 11:10:32

我根据以下快速拍摄视频完成了我的设计:http://www.xilinx.com/video/hardware/using-jtag-to-axi-master-in-vivado.html在视频

2020-08-12 09:16:08

问候,因此,我在创建IP外设并在VIVADO中使用ZYBO板单击“使用AXI4 BFM仿真接口验证外设IP”选项时收到此错误消息。我只想看到AXI接口的模拟我甚至没有它的逻辑,我创建了一个虚拟项目

2019-04-12 15:17:23

HI, 我正在尝试使用浮点IP在Zedboard上生成一个系统(SoC)(使用VIVADO 2016.4)。由于这个IP具有分层接口,我使用AXI DMA将此ip添加到AXI系统总线。但现在我的问题是如何使用Xilinx SDK检查此IP? (表示如何向IP发送输入以及如何检查输出)。谢谢

2020-05-26 14:04:10

多选一的抉择相较于Axi4写通路,多通路的多选一就容易多了。对于Axi4ReadOnlyArbiter,其仅需处理两个问题:Ar通路多端口仲裁,其处理和写通路aw通路基本相同,采用多端口RR调度即可

2022-08-08 14:32:20

你好。Vivado 2015.1 IP目录包含AXI_interconnect V1.7(默认情况下),同时DIR .. / data / IP / xilinx包含文件

2019-04-08 10:30:32

。例如,我是否会自己编写实例和一切代码?或者我应该使用向导,例如添加LogiCore IP的新来源?我可能会马上遇到障碍,并提出一个更基本的问题。那之后我肯定会遇到问题。正如我所说,我完全迷失了......

2020-06-18 15:31:21

元素(如混合端序结构)的支持。

本文档重点介绍AXI4中定义的AXI的关键概念,并强调了差异

适用时,适用于AXI3。AXI5扩展了AXI4,并引入了一些性能和Arm

架构特征。此处描述的关键概念仍然适用,但

AXI5在此未涵盖

2023-08-09 07:37:45

大家好。我目前正在使用GTH收发器实现更复杂的设计,这些收发器工作在2.8 GHz(5.6GB),我想知道我是否可以使用AXI4流以某种方式从收发器中提取输入数据。有没有办法将数据写入内存并

2019-05-05 13:14:10

你好是否可以使用带有AXI4接口的逻辑核心ip reed solomon编码器版本9。问候Rose Varghese

2020-05-20 15:44:58

be experienced AXI4-Stream to Video Out IP core?Is there any special keys I need to pay attention to make

2019-03-08 10:00:05

我想在ZYNQ上的PS也就是ARM上跑linux系统,然后PL中有加入一个AXI4的IP,IP中有多个寄存器,我不知道该如何开发驱动程序来对这个寄存器列表进行读写。然后单个寄存器在Embedded

2015-07-22 19:11:29

读写分离的设计在Axi4总线中,读和写通道是完全相互独立,互不干扰。故而无论是在设计Decoder还是Arbiter时,均可以采用读写分离的方式。如前文所述,SpinalHDL在基于Axi4总线

2022-08-03 14:27:09

,ar)共用一组信号的接口(arw,w,b,r)。关于总线互联的设计凡是设计中用到Axi4总线的设计总离不开总线互联。在Xilinx FPGA使用中,VIvado针对Axi4总线提供了丰富的IP,对于

2022-08-02 14:28:46

嗨,我已经通过以太网MAC IP作为“LogiCORE IP 10千兆以太网MAC v13.1”U.G. PG072。由于我对AXI没有太多了解,因此我几乎没有查询读取AXI4-Stream接口

2020-04-28 10:00:42

大家好。我遇到了xilinx视频内核的问题,并试图解决这个问题好几周但都失败了。有人能给我一些关于AXI4-Stream到Video核心的技巧吗?我试图在我的项目中实现Video Scaler核心

2019-11-08 09:53:46

microblaze通过串口读写FPGA内部axi4总线上的寄存器

2020-12-23 06:16:11

不正确吗?我正在使用的AXI4-Stream FIFO版本是LogiCORE IP FIFO Generator v9.3我已经附上了png,以防它不清楚谢谢,杰姆

2019-08-12 07:29:20

UG157 - LogiCORE™ IP Initiator/Target v3.1 for PCI™ 入门指南

2008-07-28 15:45:41 50

50 Xilinx ISE Design Suite 12.4 现在将更好地帮助您全面提升和改进设计。

Spartan-6 FPGA 将静态功耗削减 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持现已开始投产,可满足即插即用

2010-12-23 21:55:07 1294

1294 你可以将两块FPGA甚至是两块FPGA板捆绑在一起,使用并行或串行I/O以及Chip2Chip LogiCORE和AXI IP的组合,使他们相当于一个器件进行工作。这在新的应用笔记“AXI

2017-02-09 02:11:08 2167

2167 Northwest Logic 的 DMA 内核现已支持 Vivado 设计套件中的 IP 集成器工具流。 IP 集成器流可为客户简化将基于 AMBA® AXI4 接口的 IP

2017-02-09 08:12:36 319

319

本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。 1AXI简介(本部分内容参考官网资料翻译) 自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用

2018-06-29 09:33:00 14958

14958

了解如何使用Xilinx AXI验证IP有效验证和调试AXI接口。

该视频回顾了使用的好处,以及如何使用示例设计进行模拟。

2018-11-20 06:38:00 3561

3561 Xilinx Logicore IP直接数字合成器(DDS)编译核心采用Axi4流兼容接口,实现高性能、优化的相位生成和相位-正弦威廉希尔官方网站

。

2019-09-09 08:00:00 20

20 xilinx logicore™ip块内存生成器(bmg)核心是一个高级内存构造函数,它使用xilinx fpgas中的嵌入式块ram资源生成面积和性能优化的内存。用户可以快速创建优化的内存,以利

2019-10-30 08:00:00 5

5 AXI-4 Memory Mapped也被称之为AXI-4 Full,它是AXI4接口协议的基础,其他AXI4接口是该接口的变形。总体而言,AXI-4 Memory Mapped由五个通道构成,如下图所示:写地址通道、写数据通道、写响应通道、读地址通道和读数据通道。

2020-09-23 11:20:23 5453

5453

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,但PS与PL之间的接口却只支持前两种,AXI-Stream只能在PL中实现,不能直接和PS相连,必须通过AXI

2020-09-24 09:50:30 4289

4289

在FPGA程序设计的很多情形都会使用到AXI接口总线,以PCIe的XDMA应用为例,XDMA有两个AXI接口,分别是AXI4 Master类型接口和AXI-Lite Master类型接口,可通过

2020-10-30 12:32:37 3953

3953

引言 近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq、Zynq MP、MicroBlaze 和全新的 Versal 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有

2020-09-27 11:06:45 5857

5857

侧接口,选择AXI4。基本上,Xilinx的IP都提供了AXI标准接口,所以,控制Xilinx的IP,要先学会AXI协议。 2、点击Next,进入下一配置页面

2020-11-26 15:02:11 7386

7386

XDMA是Xilinx封装好的PCIE DMA传输IP,可以很方便的把PCIE总线上的数据传输事务映射到AXI总线上面,实现上位机直接对AXI总线进行读写而对PCIE本身TLP的组包和解包无感。

2020-12-28 10:17:23 2692

2692 AXI-Lite或AXI4转接。PS与PL之间的物理接口有9个,包括4个AXI-GP接口和4个AXI-HP接口、1个AXI-ACP接口。 Xilinx提供的从AXI到AXI-Stream转换的IP核有:AXI-DMA,AXI-Datam

2020-11-02 11:27:51 3880

3880

Xilinx LogiCORE IP块内存生成器(BMG)内核是一种高级内存构造函数,它使用XilinxFPGAs中的嵌入式块RAM资源生成区域和性能优化的内存。

2020-12-09 15:31:00 22

22 本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4。

2021-03-17 21:40:29 25

25 ,它使用通用的AXI4接口在系统中移动或转换数据,而不解释数据。 这些基础的IP各自有自己的常用的功能,下面列举出一部分AXI接口的基础构架IP。 ° AXI Register slices

2021-05-11 14:52:55 5612

5612

本系列我想深入探寻 AXI4 总线。不过事情总是这样,不能我说想深入就深入。当前我对 AXI总线的理解尚谈不上深入。但我希望通过一系列文...

2022-02-07 11:36:33 4

4 本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 7547

7547

本文主要介绍关于AXI4-Stream Video 协议和AXI_VDMA的IP核相关内容。为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2022-07-03 16:11:05 6846

6846 AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解

2022-07-04 09:40:14 5818

5818 Xilinx vivado下通常的视频流设计,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556 上面两图的区别是相比AXI3,AXI4协议需要确认AWVALID、AWREADY握手完成才能回复BVALID。为什么呢?

2023-03-30 09:59:49 668

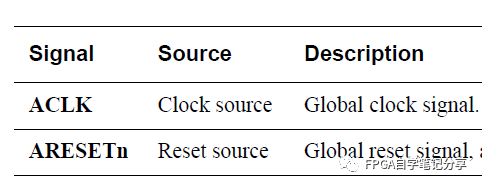

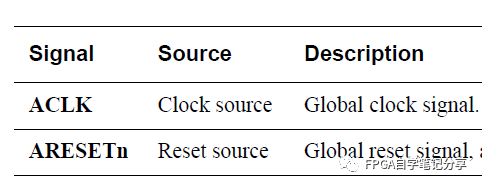

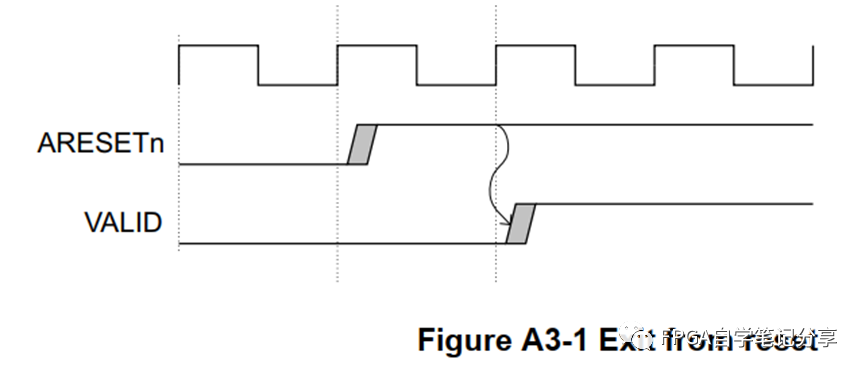

668 AXI4 协议定义了五个不同的通道,如 AXI 通道中所述。所有这些通道共享基于 VALID 和 READY 信号的相同握手机制

2023-05-08 11:37:50 700

700

大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。

2023-05-18 14:55:16 966

966

上文FPGA IP之AXI4协议1_协议构架对协议框架进行了说明,本文对AXI4接口的信号进行说明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4协议1_信号说明把AXI协议5个通道的接口信息做了说明,本文对上文说的信号进行详细说明。

2023-05-24 15:06:41 669

669

最近需要用到AXI接口的模块,xilinx的IP核很多都用到了AXI总线进行数据和指令传输。如果有多个设备需要使用AXI协议对AXI接口的BRAM进行读写,总线之间该如何进行仲裁,通信?

2023-06-19 15:45:14 4243

4243

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

2023-06-21 15:21:44 1729

1729

AXI4协议是一个点对点的主从接口协议,数据可以同时在主机(Master)和从机(Slave)之间**双向** **传输** ,且数据传输大小可以不同。

2023-06-21 15:26:43 1388

1388

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

2023-06-25 16:31:25 1914

1914

外部存储器接口( EMIF )通信常用于FPGA和DSP之间的数据传输,即将FPGA作为DSP的外部SRAM、或者协同处理器等。Xilinx提供了AXI-EMC IP核,将其挂载到AXI总线用于

2023-08-31 11:25:41 2357

2357

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE IP AXI以太网内核,而无需使用完整的DMA解决方案。

2023-09-25 10:55:33 497

497

Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过IP定制Vivado

2023-10-16 10:12:42 410

410

LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过 AXI4-Lite 接口进行连接。

2023-10-16 11:02:01 1762

1762

Xilinx LogiCORE IP视频定时控制器内核是一款通用视频定时生成器和检测器。该内核可通过完整的寄存器集进行高度编程,从而控制各种定时生成参数。这种可编程性与一组全面的中断位相结合,可轻松集成到处理器系统中,实现对模块的实时系统控制。视频定时控制器提供一个可选的AXI4-Lite兼容接口。

2023-10-16 11:06:40 292

292

以AXI4为例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种: •AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

本文主要集中在AMBA协议中的AXI4协议。之所以选择AXI4作为讲解,是因为这个协议在SoC、IC设计中应用比较广泛。

2024-01-17 12:21:22 224

224

电子发烧友App

电子发烧友App

评论